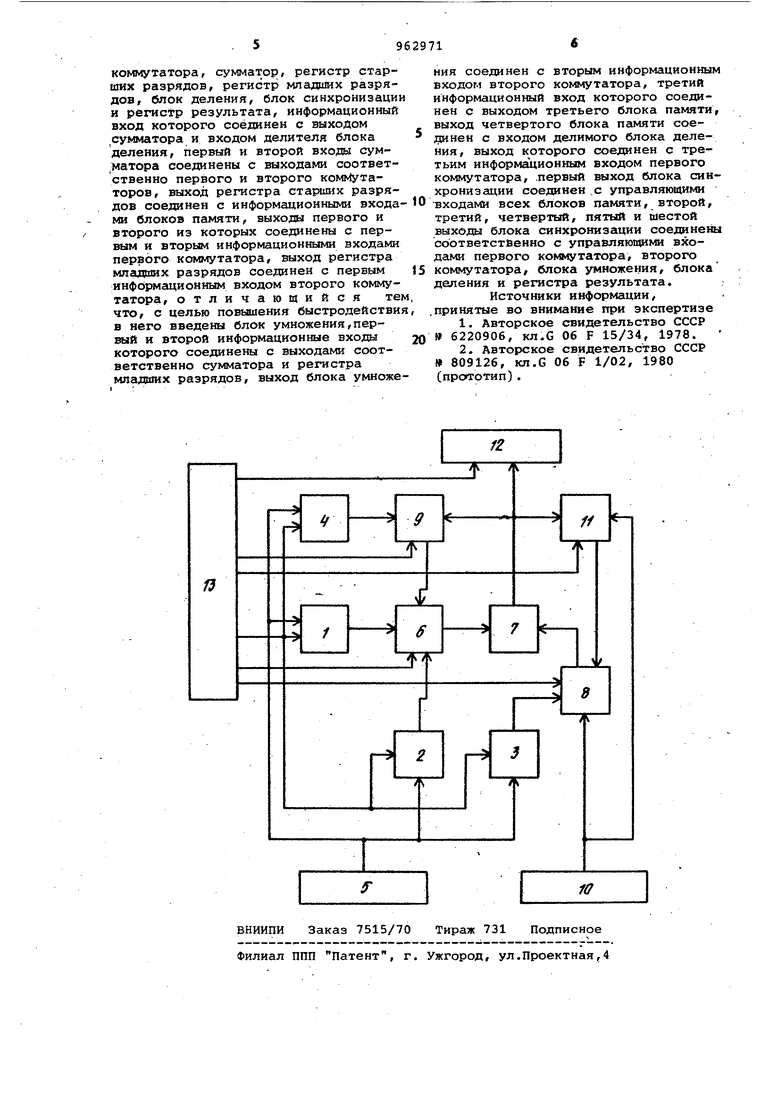

Изобретение относится к вычислительной технике и может быть использовано для аппаратурной реалиЗс1ции функций в специализированных и универсальных быстродействующих ци ровых вычислительных машинах. Известен функциональный преобразо ватель, содержащий регистры старших и младших разрядов аргумента, блоки памяти, умножителя и сумматор 1J. Недостатком преобразователя является низкая точность преобразования Наиболее близким по технической сущности к предлагаемому является устройство, содержащее регистр старших разрядов аргумента, соединенный с адресными входами четырех блоков памяти, первый и второй из которых через первый коммутатор соединены с первым входом сумматора, другой вход которого через второй коммутатор под ключен к выходу регистра младших разрядов аргумента, а выход сумматора соединен с входом делителя блока деления и с выходным регистром C2J. Недостатком данного устройства является необходимость применения двух последовательных операций деления, что существенно снижает его .быстродействие. Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что преобразователь, содержащий четыре блока памяти, два коммутатора сумматор, регистр старших разрядов, регистр младших разрядов, блок деления, блок синхронизации и регистр результата, информационный вход которого соединен с выходом сумматора и входом делителя блока деления, первый и второй входы сумматора соединены с выходакш соответственно первого и второго коммутаторов, выход регистра старших разрядов соединен с информационными входа ш блоков памяти, выходы первого и второго из которых соединены с первым и вторым информационными входами первого коммутатора, выход регистра младших разрядов соединён с первым информационным, входом второго коммутатора, дополнительно введены блок умножения, первый и второй информационные входы которого соединены с выходами соответственно сумматора и регистра младших разрядов, выход блока умножения соединен с вторым информационным входом второго коммутатора, третий информационный вход которого соединен с выходом третьего блока памяти, выход четвертого блока памяти соединен с входом делимого блока деления, выхо которого соединен с третьим информа ционным входом первого коммутатора первый выход блока синхронизации соединен с управляющими входами все блоков памяти, второй, третий, четвертый, пятый и шестой выходы блока синхронизации соединены соответстве но с управляющими входами первого коммутатора, второго коммутатора, блока умножения, блока деления и регистра результата. Вычисление значений функции производится на основе следующих соотношений. Пусть задана функция FCx), O-fia x BCl, удовлетворяющая условию IFCx)/, значения аргумента х пред ставляются п-разрядным двоичным кодом, а значения функции у FCx) тр буется находить с п-верными двоичны мй цифрами после запятой. Разобьем аргумент х 0, х х,. . в сумму двух слагае Ф х Хд 0, X. , .. х.,0. . .0 и UX 0,0...0 1 о. х..х;-,х: XQ+ ьх Расчеты показывают, что значения заданной функции F(x) можно аппрок мировать выражением иЫ --ИЧо)(т(о)Ч(Уои &V 1; где F(XO), А(ХС,), B(XO), С(х,) зависят только от .промежуточного аргумента Хд, но не зависят от их и определяются следующим образом: А(Х oV- )-Ф(о) I Ф(М ()/Ф(ад; С(.о)- -ФгСХо)); ),--(;4. Значение параметра k для получе верными всех двоичных разрядов результата п необходимо взять из выр жения К-Г(У И4-еое М)|41. .,Ф|а)()} ФаСг),Сг) I, C35ZSB o, Где значение коэффициентов Р(х,) , АСхр), В(хр), С(Хо) предварительно рассчитываются по указанным формам запоминаются по соответствующим адресам блоков памяти предлагаемого устройства. На чертеже представлена блок-схе ма преобразователя. Устройство содержит блоки 1-4 па мяти, регистр 5 старших разрядов, коммутатор б, сумматор 7, коммутатор 8, блок 9 деления, регистр 10 млс1длшх разрядов, блок 11 умножения регистр 12 результата, блок 13 синхронизации. Преобразователь работает следующим образом. В первом такте по адресу х,, передаваемому с выходу регистра старших разрядов аргумента 5 на входы блоков 1-4 памяти, на выходах которых появляются соответственно значения коэффициентов РСХд), С(Хо), А(ХО), В(х). По сигналам блока 13 синхронизации, поступающим на первый и второй коммутаторы б и 8, значения С(хо) с выхода блока 2 памяти и&х с выхода регистра 10 младших разрядов аргумента поступают на входы сумматора 7, на выходах которого формируется значение ССх,) +лх. Во втором такте работы по сигналу из блока 13 синхронизации, поступающему на блок 9 деления, на его входы поступают значения B(XO) с выхода блока 4 памяти и С(х) и х с выхода сумматора 7. При этом на выходе блока деления формируется частное В (х)/(С (х) -«-AX). В третьем такте работы по сигналу из; блока 13 синхронизации,поступающему на блок 11 умножения, значение сум1 ы с выхода сумматора 7 и значение Afx) с выхода регистра 10 младших разрядов аргумента поступают на входы блока 11 умножения, на выходе которогр формируется произведение (А(ХО) + B(XO) /(С(Хо) +Ах)Ьдх. В последнем, пятом, такте работы устройства произведение с выхода блока 11 умножения и его значение F(X{,) под действием сигналов из блока 13 синхронизадии, поступающих на первый и второй коммутаторы 6 и 8, передаются на входы сумматора 7, на вУходе которого образуется сумма F(x)F(x-o) + CAtxo)+BCxo)/(C(xo)+ux;))Ax По сигналу из блока 13 синхронизации значение Р(х) с выхода сумматора 7 передается на регистр 12 результата. Таким образом, время Ту, требуемое для вычисления значения функции . в предлагаемом устройстве, составляет Ту де в ° в время для устройства прототипа время вычисления функции определяется Тп 4.1с„+2гдел. Полагая, что tb,eA 21л,„„(умножёние с анализом двух разрядов множителя), получаем V л Ту, 4t,,. Таким образом, предлагаемое устройство обеспечивает вьшгрьни во времени на 25% по сравнению с известным устройством, что существенно повышает его быстродействие. Формула изобретения Функциональный преобразователь, содержащий четыре блока памяти,два

коммутатора, сумматор, регистр старших разрядов, регистр младших разрядов, блок деления, блок синхронизации и регистр результата, информационный вход которого соединен с выходом сумматора и входом делителя блока деления, первый и второй входьз сум Матора соединены с выходами соответственно первого и второго коммутаторов, выход регистра старших разрядов соединен с информационньлми входами блоков памяти, выходы первого и второго из которых соединены с первым и вторым информационными входами первого коконутатора, выход регистра младйшх разрядов соединен с первым информационным входом второго коммутатора, отличающийся тем что, с целью повышения быстродействия в него введены блок умножения,первый и второй информационные входы которого соединены с выходами соответственно сумматора и регистра млёщших разрядов, выход блока умножения соединен с вторым информационным входом второго коммутатора, третий информационный вход которого соединен с выходом третьего блока памяти, выход четвертого блока памяти соединен с входом делимого блока деления, выход которого соединен с третьим информационным входом первого коммутатора, .первый выход блока синхронизации соединен,с управляющими входами всех блоков памяти, второй, третий, четвертый, пятый и шестой выходы блока синхронизации соединены соответственно с управляющими входг1ми первого коммутатора, второго коммутатора, блока умножения, блока деления и регистра результата.

Источники информации, .принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 6220906, кл.С 06 F 15/34, 1978.

2.Авторское свидетельство СССР 809126, кл.С 06 F 1/02, 1980 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь | 1983 |

|

SU1126968A1 |

| Цифровой функциональный преобразователь | 1982 |

|

SU1027732A1 |

| Устройство для вычисления функций | 1982 |

|

SU1067510A1 |

| Цифровой генератор функции | 1977 |

|

SU711556A1 |

| Цифровое устройство для воспроизве-дЕНия фуНКций | 1979 |

|

SU809126A1 |

| Множительное устройство | 1978 |

|

SU824206A1 |

| Устройство для вычисления функций двух аргументов | 1983 |

|

SU1191917A1 |

| Устройство для вычисления тригонометрических функций тангенса и котангенса | 1980 |

|

SU907545A1 |

| Цифровой генератор функций | 1980 |

|

SU894692A1 |

| Устройство для логарифмирования двоичных чисел | 1981 |

|

SU1059572A1 |

Авторы

Даты

1982-09-30—Публикация

1980-06-30—Подача