Изобретение относится к вычислительной технике и может быть использовано для ускоренного вычисления произвольной функции двух арryisieHTOB, в частности для вычисления функции необходимой при выполнении преобразования декартовых координат в полярные координаты.

Известно вычислительное устройство, предназначенное для вычисления функций двух аргументов и соддержащее регистр старших разрядов первого аргумента, регистр младших разрядов первого аргумента, регистр старших разрядов второго аргумента, регистр младших разрядов второго аргумента, блок памяти, сумматор, выход которого соединен со входами буферного регистра и регистра результата, и блок синхр-онизации 1 .

Недостатком такого устройства являются отмосительно невысокие точность и быстродействие.

Наиболее близким к предлагаемому по технической сущности является устройство для вычисления функций, содержащее регистр старших разрядов аргy eнтa, регистр младших, разрядов аргумента, три блока памяти, блок умножения, два коммутатора, сумматор, буферный регистр и регистр результата, причем выход регистра старших разрядов первого аргумента соединен с первым входом блока памяти/ первый выход которого соединен с первым информационным входом первого коммутатора, выход которого саедннен с входом регистра результата и информационным входом буфер- . него регистра, выход которого соединен с первым информационным входдом второго коммутатора, выход ре гистра ушадших разрядов первого аргумента соединен с входом первого блока умножения 2j .

Целью изобретения является рас.ширение класса решаемых задач за счет возможности дополнительного вычисления функции от одного и двух аргументов.

Поставленная цель достигается тем, что в устройство для вычисления функций, содержащее регистр старших разрядов первого аргумента, регистр младших разрядов первого .аргумента, блок памяти, первый блок умножения, первый и второй коммутаторы, буферный регистр, сумматор и регистр результата, причем выход регистра старших разрядов первого аргумента соединен с первым входом блока памяти,. первый выход которого соединен с первым информационным входом первого коммутатора, выход которого динен с первым входом сумматора, выход которого соединен с входом регистра результата и информационньам входом буферного регистра, выход которого соединен с первым ниформационным входом второго коммутатора, выход регистра младааих раэ рядов первого аргумента соединен с первым входом первого блока умноження дополнительно введены блок синхронизации, регистр старших разрядов второго аргумента, регистр млаД ших разрядов второго аргумента и второй блок умножения, первый и второй входы которого соединены соответственно с выходом регистра младших разрядов второго аргумента и вторым выходом блока памяти, третий выход которого соединен со вторым входом первого блока 5 множения, выход которого соединен со вторым информационным входом первого коммутатора, управляющий вход которого соединен с первым выходом блока синхронизации, второй и третий выходы которого соединены соответственно со входами записи буферного регистра и управляющим входом второго коммутатора, второй информационный вход и ВЕЛход которого соединены соответственно с выходом второго блока умножения и вторым входом сумматора, выход регистра старших разрядов второго аргумента соединен со вторым входом блока памяти.

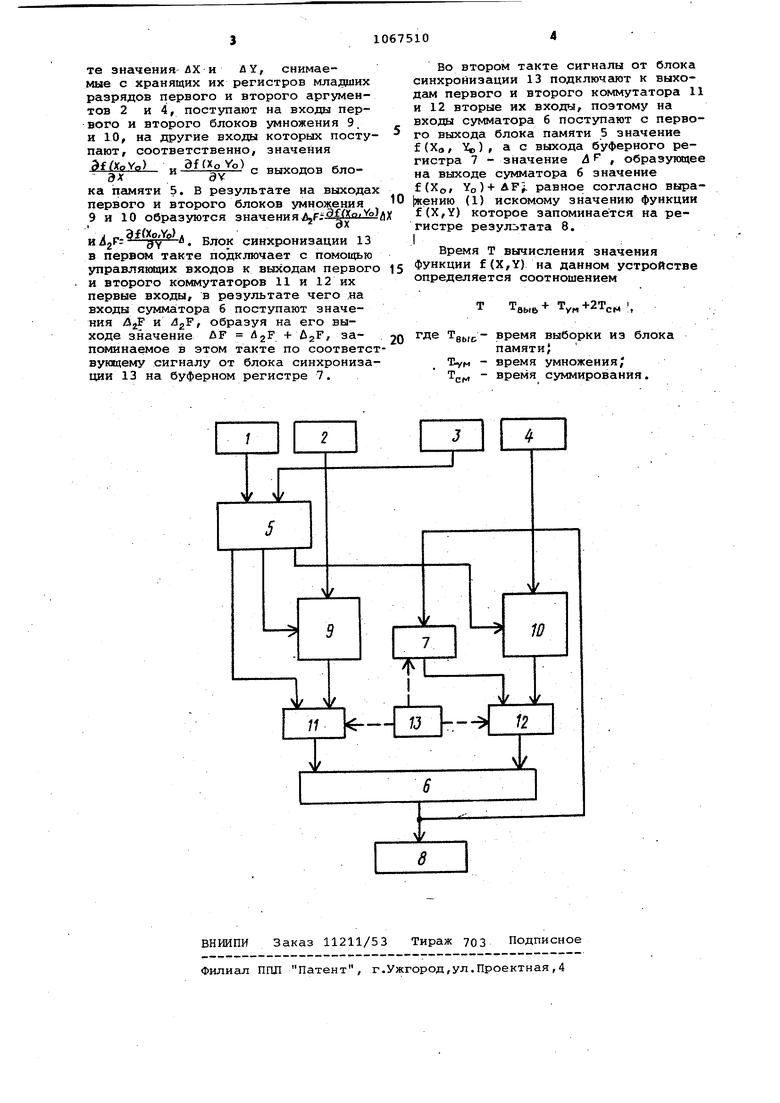

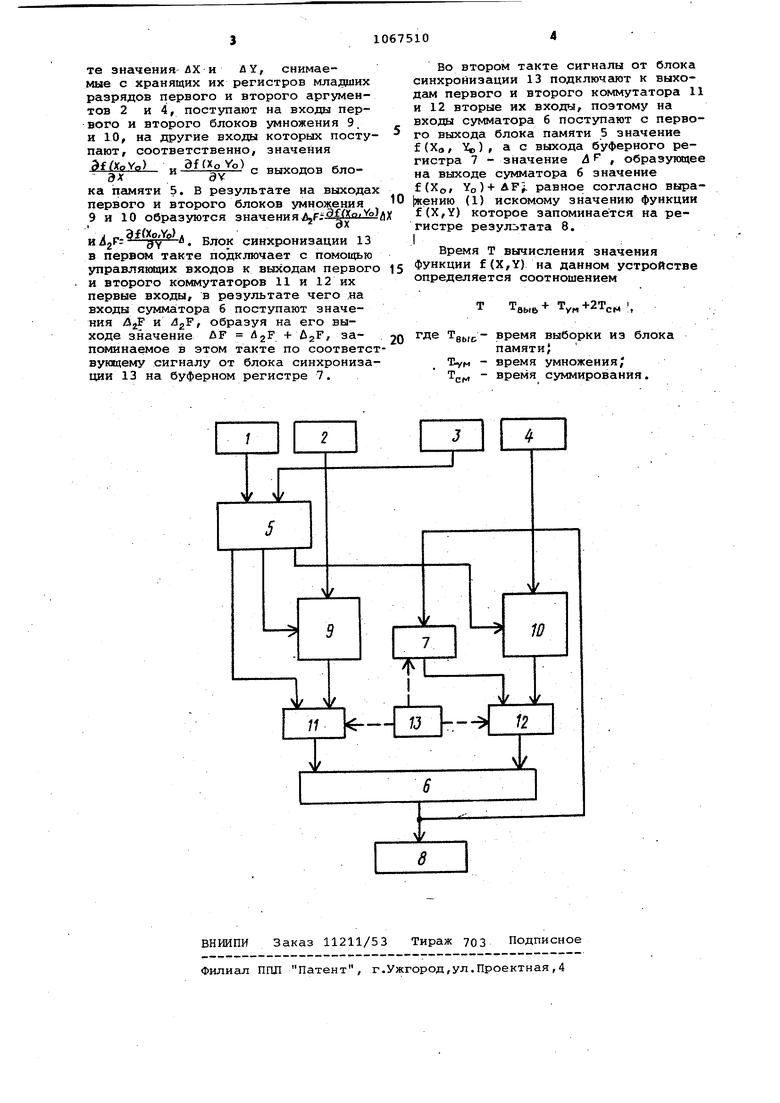

На чертеже изображена блок-схема предлагаемого устройства.

Ус.тройство содержит регистр 1 старших разрядов первого аргумента, регистр 2 младших разрядов первого аргумента, регистр 3 старших разрядов второго аргумента, регистр 4 младших разрядов второго аргумента, блок памяти 5, сумматор 6, буферный регистр 7, регистр результата 8, блоки умножения 9, 10, коммутаторы 11 и 12, блок синхронизации 13.

Вычисление значения функции f(X, Y) в устройстве производится на основе соотношения

f(X,W-fao,y.) %

ЛУ

(1)

где ХоИ Y(5 определяются старшими, разрядами, соответственно, аргументов Хи Y, а ДХиЛУ определяются младшими разрядами аргументов X и У.

Устройство работает в два такта определяемых блоком синхронизации 13 На входы блока памяти 5 с регистра 1 старших разрядов первого аргумента поступает значение Х,, а с регистра 3 старших разрядов второго аргумента, поступает значение Y.Блок памяти 5 хранит три таблицы значений, соответственно f(Xo, Y);

f(yo,Yo) . . рФСу.р.Уо). , в первом так. Эл ЗУ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функций двух аргументов | 1983 |

|

SU1191917A1 |

| Устройство для вычисления функций | 1982 |

|

SU1078427A1 |

| Устройство для вычисления функций двух переменных | 1983 |

|

SU1123034A1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU955082A1 |

| Цифровой генератор функций | 1984 |

|

SU1168921A1 |

| Устройство для вычисления функций | 1984 |

|

SU1206767A1 |

| Множительное устройство | 1978 |

|

SU824206A1 |

| Устройство для вычисления функции арксинуса | 1986 |

|

SU1456950A1 |

| Устройство для вычисления функции arctg y/x | 2017 |

|

RU2642385C1 |

| Устройство для интерполяции | 1984 |

|

SU1171807A1 |

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ, содержащее регистр старших разрядов первого аргумента,регистр младших разрядов первого аргумента, блок памяти, первый блок умножейия, первый и второй коммутаторы, буферный регистр, сумматор и регистр результата, причем выход регистра старших разрядов первого аргумента соединен с первыгл входом блока памяти, первый выход которого соединен с первым информационным входом первого коммутатора, выход которого соединен с первым входом сумматора, выход которого соединен с входом регистра результата и информационным входом буферного регистра, выход :которого соединен с первым информационным входом второго коммутатора, выход регистра младших разрядов первого аргумента соединен с первым входом первого блока умножения, о тличающееся тем, что, с целью расширения класса решаемых задач за счет возможности вычисления функций от аргументов, в него введены блок синхронизации, регистр старших разрядов второго аргумента, регистр младших разрядов второго аргумента и второй блок умножения, первый и второй входы которого соединены соответственно с выходом регистра младших разрядов второго аргумента и вторым выходом блока i памяти, третий .выход которого соединен со вторым входом первого блока умножения, выход которого соединен со вторым информационным входом первого коммутатора, управляющий вход которого соединен с первр.лм выходом блока синхронизации, второй и третий выходы которого соединены соответственно с входом записи буферного регистра и управляющим входом второго коммутатора, второй информационный вход и выход которого соединены соответственно с выходом второго блока умножения и втоСП рым входом сумматора, выход pe иcтра старших разрядов второго аргумента соединен со вторым входом блока памяти.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для сбора и удаления мусора | 1987 |

|

SU1413045A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Сплав для отливки колец для сальниковых набивок | 1922 |

|

SU1975A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Потапов В.И./ Нестерук В.Ф | |||

| и Флоренсов А.Н | |||

| Быстродействующие арифметико-логические устройства цифровых вычислительных машин | |||

| Новосибирск | |||

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

| Коридорная многокамерная вагонеточная углевыжигательная печь | 1921 |

|

SU36A1 |

Авторы

Даты

1984-01-15—Публикация

1982-09-27—Подача