Jl3o6peTeHHe относится к вычислительной технике и может, быть использовано для аппаратурной реализации функций в специализированных и универсальнык быстродейству(о1цих цифровых вычислительных машинах о

Известно устройство для логарифмирования, содержащее регистры старших и младших разрядов . аргумента,. три блока памяти, коммутатор, oivfMaтор, регистр результата 1j ,

Недостатком известного устройства является узкий класс peraaei ibK задач .

Наиболее близким к пpeдлaгaeмo является функциональный преобразователь содержащий регистр мп:адт11их разрядов аргумента, регистр старших разрядов аргумента, соединенный с адресными входами первого и второго блоков памяти, выход которого подключен к входу делимого блока деления, блок умножения, третий и четвер тый блок памяти, сумматор, выход которого связан с входом регистра результата 2J .

Недостатком данного устройства является необходимость последовательного применения операций деления и умножения, что существенно сншжает их производительность.

Цель изобретения - увеличение быстродействия устройства.

Поставленная цель достигаете тем, что в функциональный преобразователь, содержащий регистр старишх разрядов аргумента, регистр maдшиx разрядов аргумента, четыре.блока памяти, первьй сумматор, блок умнолсеHHHj блок деления и регистр результата, информационный вход которого соединен с выходом первого сумматора выход регистра старших р.азрядов аргумента соединен с адресными входами первого и второго блоков памяти, выход второго блока памяти -соединен с входом делимого блока делениЯ} дополнительно введены три промежуточ ных регистра, второй и третий сумматоры и блок синхронизации, пер вый выход которого соединен с входами синхронизации первого и второго промежуточных регистров и регистра результата, второй вькод блока синхронизации соединен с входами сишсро нпзацин регистров старших и младших разрядов аргумента и третьего промежуточного регистра, вькод регистра

младши-х разрядов аргумента соединен с первым входом второго сумматора и информационным входом второго промежуточного регистра, выход которого соединен с первым входом блока умнолсения, второй вход и выход которого соединены соответственно с выходом третьего и первым входом первого сумматоров, выход первого блока памяти соединен с вторым входом второго сумматора, выход которого соединен с входом делителя блока деления, выход которого подключен к информационному входу третьего промежуточного регистра, выход которого соединен с первьт входом третьего cyNiMaTOpa, выход регистра старших разрядов аргумента соединен -с информационные входом первого промежуточного регистра, выход которого соединен с адресными входами третьего и четвертого блоков памяти, выходы которых соединены с вторьлми входами соответственно третьего и первого сумматоров, информационные входы регистров старших и младших разрядов аргумента соединены с входами соответственно старших и младших разрядов аргумента устройства,

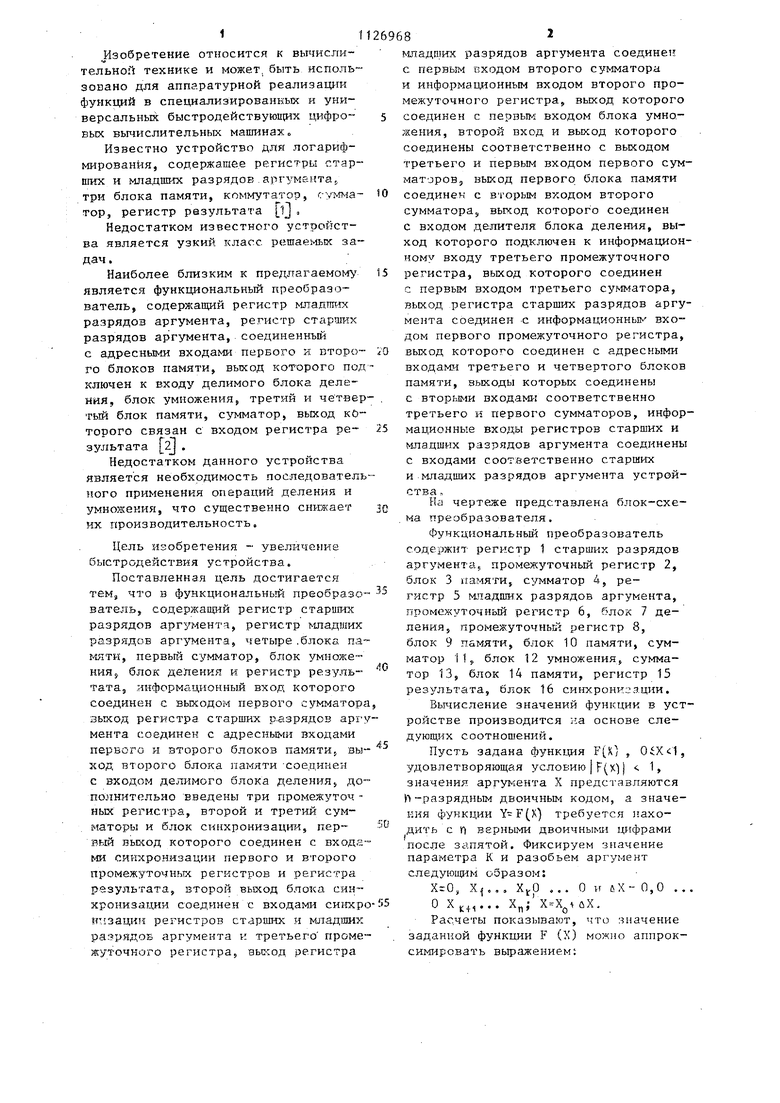

На черте-же представлена блок-схе, на преобразователя.

Функциональный преобразователь содержит регистр 1 старших разрядов аргумента, промежуточный регистр 2, блок 3 памяти, сумматор 4, регистр 5 м-падших разрядов аргумента, промежуточный регистр 6, блок 7 деления, промежуточньй регистр 8, блок 9 памяти, блок 10 памяти, сумматор 1 15, блок 2 умножения, сумматор 13, блок 14 памяти, регистр 15 результата, блок 16 синхронксации.

Вычисление значений функции в устройстве производится на основе следующих соотношений.

Пусть задана функция F(K) , , удовлетворяющая условию F(x) 1 1, значения аргумента X представляются У -разрядным двоичным кодом, а значения функции Y-F(X) требуется иахо дить с п верными двоичным цифрами после зггпятой. Фиксируем значение параметра К и разобьем аргумент следуюи0-1м образом:

ХгО, Х,,. Xj-O ... О V 6Х-0,0 ..

О X

Х„; ,йХ.

К-1-1

.четы показывают, что значение заданной функции F (X) можно аппроксимировать выражением: и (X)rF(Xj,) + 4X.(A(X(j)tB (Хо)/ /(С(Хо)44Х)),(1) где коэффициенты F(Xp), А(Хд), B(X( C(XQ) зависят только от промежуточного аргумента Х, но не зависят от ik X и определяются следующм обра зом: )ф/Хд)-Ф;(Хо)/Ф,(Хд), А(ХО) В(Х,)-ф|(Х)/ФиХо), С(Хо)-Ф2(Хо)/Фз(Хо) Ф(г)рЧг) 11, ,А. Значение параметра К для получения верными всех двоичных разрядов результата П необходимо взять из выражения: (пи + )/41 tP,t))) М члах 2(2)-.Ф,и Oi,2 2Значения коэффициентов Г(Хд), А(Х(), B(XQ), ССХд) предварительно рассчитываются по вышеуказанным фор мулам и запоминаются по соответству щим адресам блоков памяти рассматриваемого устройства. Устройство работает следующим образом. В первом такте блок 16 синхронизации формирует на втором вьсходе си нал синхронизации С1, который посту пает на управляющие входы регистра старших разрядов аргумента и регист ра 5 младших разрядов аргумента, на которые заносится код первого аргумента. Код старших разрядов аргумен та с выхода регистра 1 старших разрядов аргумента поступает на адресные входы первого 3 и второго 9 бло ков памяти. На выходе первого блока памяти формируется значение С(Х), которое поступает на вход второго сумматора 4. На выходе второго сумма jpa 4 образуется значение C(X)t лХ, поступающее на вход делителя блока 7 деления. Код ВСХо) с выхода блока 9 памяти поступает на вход делимого блока 7 деления, на выходе которого формируется значение промежуточного результата F,(x)(.Xo) / С(Хо 6Х). Во втором такте работы блок 16 синхронизации формирует на первом 684 выходе сигнал синхронизации С2, который поступает на управляющие входы, регистра 2 и регистра 6,при этом код первого аргумента переписывает- ся с выхода регистра 1 старших разрядов аргумента на промежуточный регистр 2 и с выхода регистра 5 младших разрядов аргумента на промежуточньш регистр 6. Код Х старших разрядов аргумента с выхода промежуточного регистра 2 поступает на адресные входы третьего 10 и четвертого 14 блоков .памяти. При этом на выходе третьего блока 10 памяти формируется значение А(ХО), а на выходе четвертого блока 14 памяти - значение F(XQ) . В третьем такте работы устройства блок 16 синхронизации формирует очередной сигнал серии С1, под управлениём которого в регистр 1 старших разрядов аргумента и регистр 5 младших разрядов аргумента заносится код второго аргумента. Одновременно в промежуточный регистр 8 заносится код промежуточного результата F|(X) , поступающий затем на вход третьего сумматора 11, на друЬом входе которого уже находится код А()(о) . С выхода третьего сумматора 11 сумма (А(ХО)А- Р(()1) поступает на первый вход блока 12 умножения, на втором входе которого находится код iX. Произведение ДХ(А(Хо)4 F (X)) суммируется со значением F(Xo) на первом сумматоре .13, на выходе которого образуется значение результата F(X) F(Xo)4AX-(A((o)t F(X)) . В четвертом такте блок 16 синхро- низации формирует сигнал С2, под управлением которого код второго аргумента заносится .на промежуточные регистры 2 и 6. Одновременно код результата F(X) передается с выхода первого сумматора 13 в регистр 15 результата. В дальнейшем процесс воспроизве дения функции циклически повторяется так, как это описано для предыдущих тактов работы устройства. Таким образом, производительность предлагаемого устройства приблизительно в 1,5 раза вьш1е производительности устройства-прототипа.

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь | 1980 |

|

SU962971A1 |

| Устройство для логарифмирования двоичных чисел | 1981 |

|

SU1059572A1 |

| Устройство для логарифмирования двоичных чисел | 1984 |

|

SU1241237A1 |

| Устройство для вычисления тригонометрических функций тангенса и котангенса | 1980 |

|

SU907545A1 |

| Множительное устройство | 1978 |

|

SU824206A1 |

| Цифровой функциональный преобразователь | 1986 |

|

SU1361547A1 |

| Устройство для вычисления функций | 1984 |

|

SU1206767A1 |

| Цифровой генератор функции | 1977 |

|

SU711556A1 |

| Конвейерное устройство для вычисления тригонометрических функций | 1984 |

|

SU1168931A1 |

| Устройство для логарифмирования двоичных чисел | 1980 |

|

SU924705A1 |

ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий регистр старших разрядов аргумента, регистр младших разрядов аргумента, четыре блока памяти, первый сумматор, блок умножения, блок деления и регистр результата, информационный вход которого соединен с вьгходом первого сумматора, выход регистра старших разрядов аргумента соединен с адресными входами первого и второго блоков памяти, BbtxoA второго блока памяти соединен с входом делимого блока деления, отличающийся тем, что, с целью увеличения быстродействия, в него введены три промежуточ.ных регистра, второй и третий сумматоры и блок синхронизации, первьш выход которого соединен с входами синхронизации первого и второго промежуточных регистров и регистра результата, второй выход блока синхронизации соединен с входами синхронизации регистров старших и младших разрядов аргумента и третьего промежуточного регистра, выход регистра младших разрядов аргумента соединен с первым входом второго сумматора и информационным входом второго промежуточного регистра, выход которого соединен с первьп { входом блока умножения, второй вход и выход которого соединены соответственно с выходом третьего и лервым входом первого сумматоров, выход первого блока памяти соединен с вторым входом второго сумматора, ВЬЕХОД которого со.единен с входом делителя блока деления, выход которого подключен к информационному входу третьего промежуточного регистра, выход которого соединен с первьп входом третьего сумматора, выход регистра старших разрядов аргумента соединен с информационным входом первого промежуточного регистра, выход которого соединен с адресными входа1 м третьего и четвертого блоков памяти, выходы которьк соединены с вторыми входами, соответственно третьего и первого сумматоров, информационные входы регистров старших разрядов и младших разрядов аргумента соединены с входами соответственно старших и младших разрядов аргумента устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Потапов В.И., Нестерук В.Ф., Флоренсов А.Н | |||

| Быстродействующие арифметико-логические устройства цифровых вычислительных машин | |||

| Новосибирск, 1978 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Функциональный преобразователь | 1980 |

|

SU962971A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

Авторы

Даты

1984-11-30—Публикация

1983-07-15—Подача