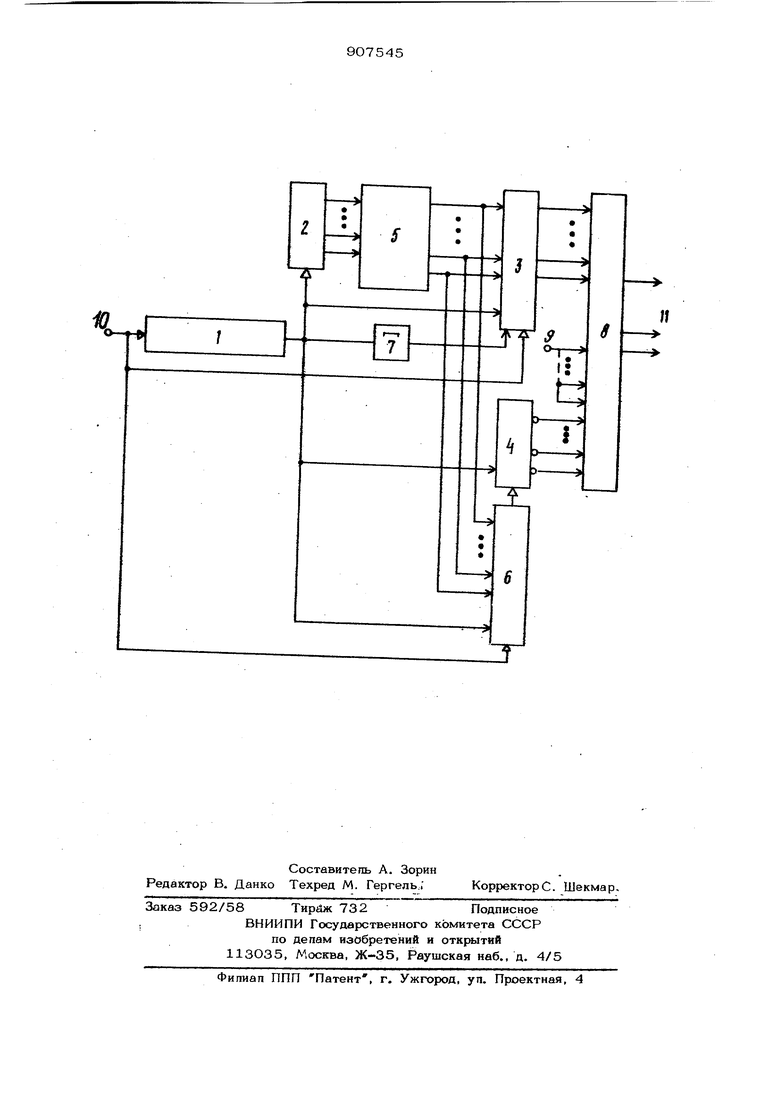

(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ТРИГОНОМЕТРИЧЕСКИХ ФУНКЦИЙ ТАНГЕНСА И КОТАНГЕНСА Изобретение относится к цифровой вычиспитепьной технике и может быть использовано в вычиспитепьных и информационно-измерительных устройствах и системах дпя вычисления тригонометрических функций тангенса и котангенса. Известно устройство, где вычиснение осуществляется с помощью итерационной процедуры многократного решения раэностных рекуррентных соотношений, реализующих численный алгоритм цифра за цифрой . Достоинством устройства явпяется малая номенклатура основных функциональных блоков и связанная с этим достаточно высокая однородность структуры С помощью устройства в принципе возможно получение результата с любой тре буемой точностью lj. Однако этому устройству пртсуши и серьезные недостатки: оно громоздко, имеет сложную кгноготактную логику работы, требует больших аппаратуртых затрат и характеризуется мапым быстродей ствием. Наиболее близким по технической сущности к предлагаемому является устройство, содержащее у -разрядный регистр аргумента (W -разрядность аргумента), блок памяти, блок управления, блок умножения, первый и второй регистр&з промежуточных результатов, блок деления, группу эпементсйв ИЛИ и входной регистр, при этом выхо№1 старших разрядов регистра аргумента соединены с адресными вхоfiKffi блока памяти, в котором :фанятся -разрядные значения функции тангенса, инфсч}мационные выходы блока памяти подсоединены к первым в ходам блок ОБ управления и умножения, а также ко входам старших разрядов второго регистра промежуточного результата, выходы мпадших S- разрядов регистра аргумента подсоединены к вторым входам блоков управления н умножения, а также к входам мяадших 2 разрядов второго регистра промежуточного результата, выходы бпока умножения подсоединены к входам мяадших f разрядов первого регистра. промежуточного рюзультата, в старших -х разрядах коюрого постоянно записаны логические единицы, выходы первого и второго регистров промежуточных результатов подсоединены к входам блока деления выходы которого соединены с первыми входами группы элементов ИЛИ, вторые входы которых подсоединены к выходам блока управления, а выходы - к входам выходного регистра устройства. В устройстве VI -разрядный код аргумента X представляется в виде суммыХ Х(5 -2 лХгде Хо и Д X - содержимое старших и младших разрядов регистра аргумента соответственно. С выхода блока памяти снимается -разрядный код t XoЕсли Хо равно нулю, то вычисление не -.-и/-2, осуществляется, а значение 2; ДХ через блок управления и группу эпементов ИЛИ прямо ретранслируется в вт гходной регистр. При смене входов блока деления вычисляется функция котангенса 2j, Данное устройство обладает достаточно высоким быстродействием и характеризуется сравнительно небольшим обьемом блока памяти. Но ему присущ и ряд серьезных недостатков, связанных прежде всего с пониженной точностью вычислений, а также с большими аппаратурными затратами. Как показывают результаты моделирования работы данного устройства, абсолютная погрешность вы юслений А при некоторых значениях аргумента может достигать значений, лежащих в диапазоне 2 (ЧТО приводит в таких ситуациях к практической недостоверности уг младших разрядов результата. Цель изобретения - повышение точности ycTpoifCTBa при упрощении конструкции Эта цель достигается тем, что в устройство, содержащее блок памяти и блок деления, дополнительно введены четыре счетчика, имеющие VW И-т П и vn разрядов соответственно, где и- разрядность аргумента, Уп- младшие разряды аргумента, элемент задержки и и - раз рядный накапливающий сумматор, тактирующий вход суммирования которого соединен с входом устройства и счетными входами пертого и третьего счетчиков, а выход переполнения - с счетным входом четвертого счетчика, выход перепопнения первого счетчика соединен с входами сброса в нулевое состояние третьего и четвертого счетчиков и накапливакмцего сумматора, входом элемента задержки и счетным входом второго счетчика, выхоKiды прямого кода всех разрядов которого подсоединены к адресным входам блока памяти, выходы которого подсоединены к соответствующим информационным входам накапливающего сумматора и соответствующим установочнь1М входам третьего счетчика, тактирующий вход предустановки которого подсоединен к ьыходу элемента задержки, выходы прямого кода всех разрядов третьего счетчика подсоединены к первым входам блока деления, старшие (И- ш) вторых входов которого подсоединены к входу с потенциалом логической единицы устройства, младшие Ул вторых входов блока деления соединены с инверсными выходами соответствующих разрядов четвертого счетчика, а выходы блока депен«я подключены к выходам устройства. На чертеже представлена структурная схема устройства. Устройство содержит Счетчики 1-4, и. Jющиe, соответственно УХ), n-vn, И и W разрядов, блок 5 постоянной п 1мяти, у - разрядный двоичный накапливающий сумматор 6, элемент 7 задержки, блок 8 деления, вход 9 с потенциалом логической единицы, вход 1О и выходы 11. I В основу алгоритма работы предлагаемого устройства положены следующие соображения. Аргумент X, выраженный в радианах , может быть представлен в виде - xl-ДX Пpи этом - 1Ю1дЛ121А 1 t--tgXo--b AX (1) При малых Л)(-Ь2ДХ ДХможно записать соотношение tg-Xo+ АХ g -l- -tgXo Если динамический диапазон возможных значений аргумента закодирован с помощью И двоичных разрядов, то в качестве U X может быть принято значение W) младших, .а в качестве XQ- (старших разрядов аргумента. Методическая погрешность замены ДХ уходит за пределы разрядной сотки уже при значениях ш чуть больших и|2/например для И 8 при Шг 5, для И - 12 при (Г)8, для ут.16 при VYi 10. Это обстоятельство позволяет существенно сократить число разрядов ( отводимых для представления значений Хо и тем самым уменьшить число значений tPXo R блоке памяти. Чтобы при этих условиях обеспечить методическую погрешность вычисле590НИИ, не превышающую-погрешности дискретности, в блоке памяти, как показыва ют расчеты, спедует хранить значения tgXo содержащие не менее у разрядов. Информационная емкость D бпока памяти при хранении И - разрядных значений ЬоХо составгшет в этом Q.бит. Например при И - 8 и т- 5 D 2 Х8 64 бит, при и :) 2 f Х12 192 бит, при У) 16 и 3 2х 16 1024 бит (в известном ус ройстве при тех же значениях h информ ционная емкость бпока памяти, равная п/а п -- бит, составляет соответственно 64, 384 и 2048 бит). При замене выражения (1) выражением (2) чиспитепь вычисляется с некоторой отрицательной, а знаменатель - с некоторой положительной погрешностью. И даже если эти погрешности не превышают погрешности дискретности, в конеч ном итоге данное обстоятельство приводит к тому, что резупьтирзующая погрешность вычислений после выполнения операции деления может составить несколько единиц младшего разряда результата. Для ее компенсации вместо выражения 1 - AX-tgXQ которому соответствует дополнительный код iiX-tp/fj целесообразно испопьзовать обратный код значе- кия AXtgXo- При этом знаменатель вы ражения (2) так же,как и числитель вычисляется с некоторой отрицательной погрешностью, и тем самым осуществляется к рекция результата вычислений. Как показывает анализ, в этом случае погрешнос вычислений не превосходит единицы млад шего разряда резу льтата при всех возмо ных значениях аргумента. Устройство работает следующим образом. В исходном положении все разряды счетчиков 1-4 и накаппивающего сумматора 6 устанавливаются в нулевое состояние. На выходах блока 5 памяти в исходном состоянии также присутствует нулевой код. Аргумент X в числоимпупьсном коде подается на вход 1О устройства. Импугеь сы входного кода поступают на счетные входы счетчиков 1 и 3 и тактирующий вход суммирования сумматора 6, который суммирует коды, снимаемые с т 1ходов блока 5 памяти. Сигнапы перепониения сумматора 6 поступают на счетный вход счетчика 4. При каждом перепопнении hi-разрядного г;четчика 1, осушествпяю- шего подсчет ДХ, к содержимому (h-W 56 разрядного счетчика 2, формирующего значения XQ добавляется единица. И-разрядные счетчик 3 и сумматор 6, а также Wi -разрядный счетчик 4 сбрасываются в нулевое состояние, а через некоторое время, зависящее от динамических свойств элементов счетчика 3 и определяемое элементом 7 задержки, счетчик 3 захватывает VI -разрядный код очередного значения tOXо/снимаемый с выходов блока 5 памяти. Тем самым, в соответствии со структурой выражения (2), в счетчике 3 формируется текущая сумма ( р Хр+ДХ); а в сумматоре 6 совместно си счетчиком 4 - текущее значение iiX . Счетчик 4 имеет только Уп разрядов, так как число суммирований очередных значений VI -разрядного кода -LoXo сумматором 6 в промежутках между сигналами сброса равно 2 - емкости счетчика 1. По окончании пост плсния импульсов входного чиспоимпульского кода прямой vn -разрядный код (-tpXot-AX) выходов счетчика 3 подается на первые входы блока деления. На вторые входы блока деления подается И-разрядный код 1-Л/.ЬоХо/образованный сочетанием разрядного инверсного кода счетчика 4, подаваемого на соответствующие младшие In вторых входов, и (и-Ум) -разрядного кода, содержащего во всех разрядах логические единицы и подаваемого с шины 9 на (Vi-VM.) старших вторых входов. На выходах 11 бпока деления, являющихся одновременно и выходами устройства, формируется VI-разрядный код результата вычислений. При этом, если в блоке деления код, поступающий на первые входы, делится на код, поступающий на вторые входы, вычисляется функция тангенса, в прютивном случае - котангенса. В сравнении с известным предлагаемое устройство прежде всего обладает существенно более высокой точностью вычислений (максимальная абсолютная методическая погрешность вычислений уменьшается по крайней мере в 2 раз, где И число разрядов результата). Кроме того, сокращаются аппаратурные затраты как за счёт частичного уменьшения необходимого объема блока памяти (например для Vi 12 или для У 16 - в два раза), так и за счет исключения ряда блоков (первого регистра промежуточного результата, бпока управления, группы элементов ИЛИ, выходного регистра) или их значительного упрощения (вместо бпока умножения двух кодов используется сочетание накапливающего сумматора 6 и счетчика 4). ного устройств соизмеримы по сложности. Так, например, УУ -разрядный счетчик 1 и (vi-yn)-разрядный счетчик 2 в совокупности соизмеримы по аппаратурным затратам с И -разрядным регистром аргумента известного устройства, а И-разрядный счетчик 3-е Vi-разрядным вторым регистром промеж -точного результата. Бпок деления в обоих устройствах,в принципе, может быть использован идентичный. Форм у-па изо бретения Устройство для вычиспения тригонометрических функций тангенса и котангенса, содержащее блок памяти и блок деления, отличающееся тем, что, с цегЕью повышения точности,в него введе ны четыре счетчика, имеющие соответственно vvi, У)-УТ), И и VY разрядов, где Иразрядность аргумента, т- м/шдшие раз ряды аргумента, элемент задержки и И - разрядный накапливающий сумматор, тактирующий вход суммирования которого соединен с входом устройства и счетными вхоцами первого и тре1ъего счетчиков, а выход переполнения с счетным входом четвертого счетчика, выход переполнения са в нулевое состояние третьего и четвертого счетчиков и накапливающего сумматора, входо:и элемента задержки и счетным входом второго счетчика, выходы прямого кода всех разрядов которого подсоединены к адресным входам блока памяти, выходы которого подсоедин ны к соответствующим информационным входам накапливающего сумматора и соответствующим установочным входам третьего счетчика, тактирующий вход предустановки которого подсоединен к выходу элемента задержки, выходы прямого кода всех разрядов третьего счетчика подсоединены к первой группе входов блока деления, старшие ( И -1 ) входов второй группы которого подсоединенБ к входу логической единицы устройства, младщие 1 входов блока деления соединены с инверсными выходами соответствующих разрядов четвертого счетчика, а выходы блока деления подключены к выходам устройства. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 650073, кл. Q 06 F 7/38, 1979. 2.Авторское свидетельство СССР № 595738, кп. G 06 F 15/32, 1978 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой генератор функций | 1980 |

|

SU980083A1 |

| Устройство для вычисления функций синуса и косинуса | 1980 |

|

SU907546A1 |

| Устройство для извлечения квадратного корня | 1980 |

|

SU1099318A1 |

| Цифровой вычислитель функций тангенса и котангенса | 1976 |

|

SU595738A1 |

| Устройство для вычисления квадратного корня | 1983 |

|

SU1141407A1 |

| Устройство для извлечения корня третьей степени | 1983 |

|

SU1129609A1 |

| Устройство для извлечения корня третьей степени | 1980 |

|

SU903870A1 |

| Устройство для вычисления тангенса | 1975 |

|

SU650073A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU940155A1 |

| Устройство для извлечения квадратного корня | 1983 |

|

SU1132289A1 |

Авторы

Даты

1982-02-23—Публикация

1980-07-24—Подача