(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с коррекцией информации | 1981 |

|

SU957273A1 |

| Запоминающее устройство | 1981 |

|

SU1029228A1 |

| Запоминающее устройство с обнаружением и исправлением ошибок | 1980 |

|

SU959167A1 |

| Запоминающее устройство с коррекцией дефектных элементов памяти | 1981 |

|

SU980165A1 |

| Запоминающее устройство | 1975 |

|

SU649044A1 |

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

| Резервированное многоканальное запоминающее устройство | 1980 |

|

SU942142A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU864339A1 |

| Запоминающее устройство | 1983 |

|

SU1203596A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU955209A1 |

.

Изобретение относится к запоминаю | щим устройствам и может быть использовано при изготовлении больших интегральных схем запоминающих, устройств с произвольной выборкой (ЗУПВ) со словарной организацией.

Известно запоминающее устройство (ЗУ), которое содержит матрицу элементов памяти, схемы логики обрамления и коррекции, дополнительные элементы памяти, позволяющие производить коррекций одного отказавшего элемента памяти в каждой строке матрйш LlJ

Недостаток данного устройства - низкая надежность.

Наиболее близким к предлагаемому является ЗУ, содержащее дешифратор адреса слова, соединенный с адресными i ганнами матрицы элементов памяти, ршз-; рядные шины которой соединены с выходами вентилей и информационными ;входа, ми блока считывания, управлякнциё входы которого подключены к выходам дешифратора адреса разряда и первым входам

вентилей, вторые входы которых соедине;ны с шиной. разрешения записи, третьи : 1Бходы - с шиной управления и первыми входами первых и вторых выходных блоков, выходы блока считывания соед1гаены с входами трехвходовых мажоритарных элементов и вторыми входами вторых выходных блоков, шины записи, выходьт и вторых выходных блоков С 2 3 .

10

Недостатком известного устройства является то, что оно позволяет производить коррекпию дефектных элементов памяти только в одной из трех подматриц матришл элементов памяти, за счет чего

15 используется только часть матрицы элементов памяти и, следовательно, уменьшается эффективная информационная емiKoctb устройства.

Цель изобретения - повышение эффек- i

20 тйвной информационной еЛжости устройст

Эа. .: . ..

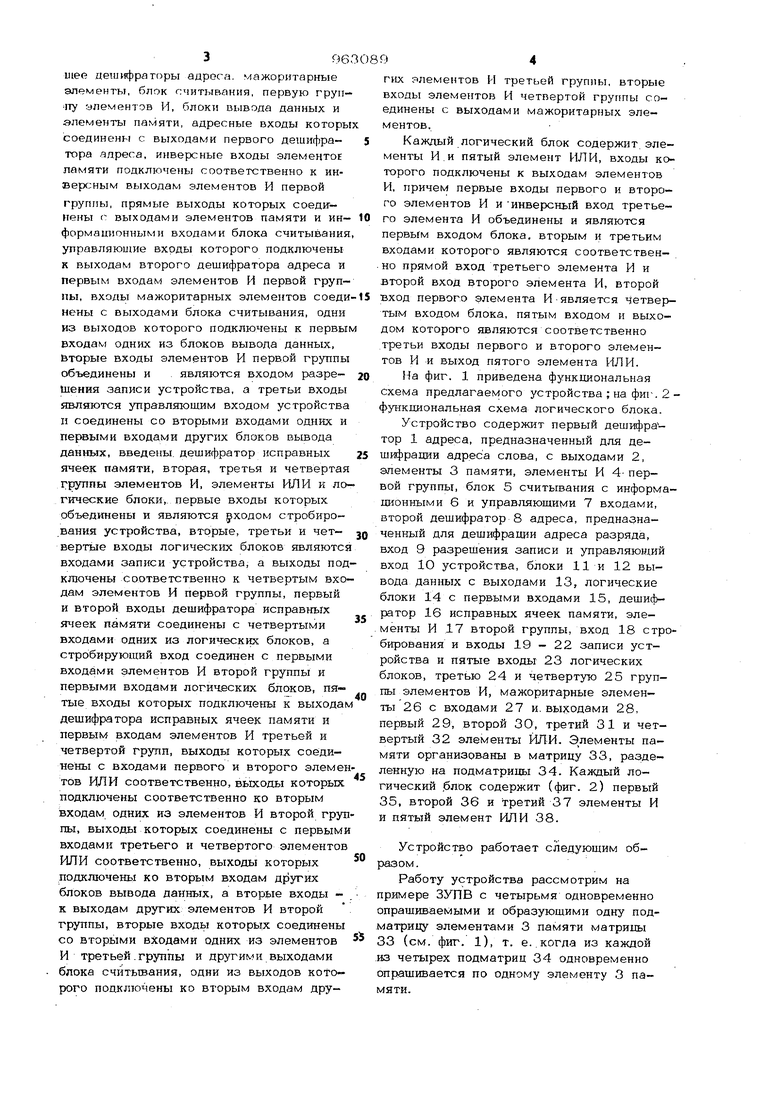

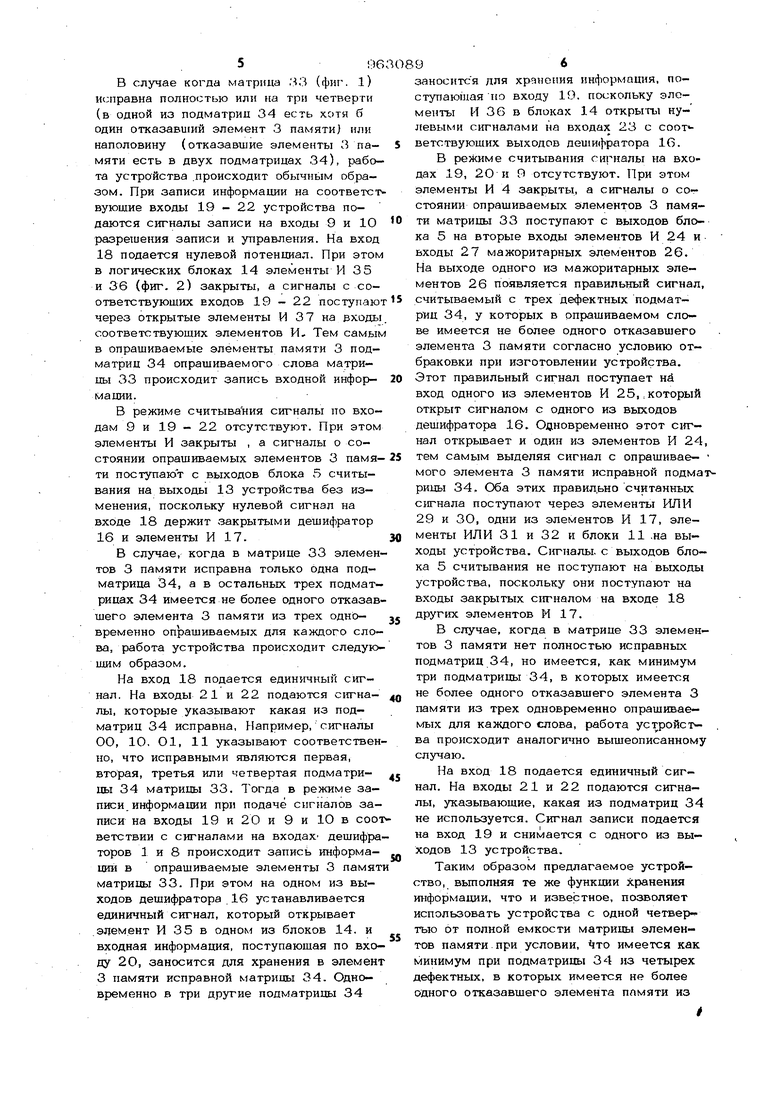

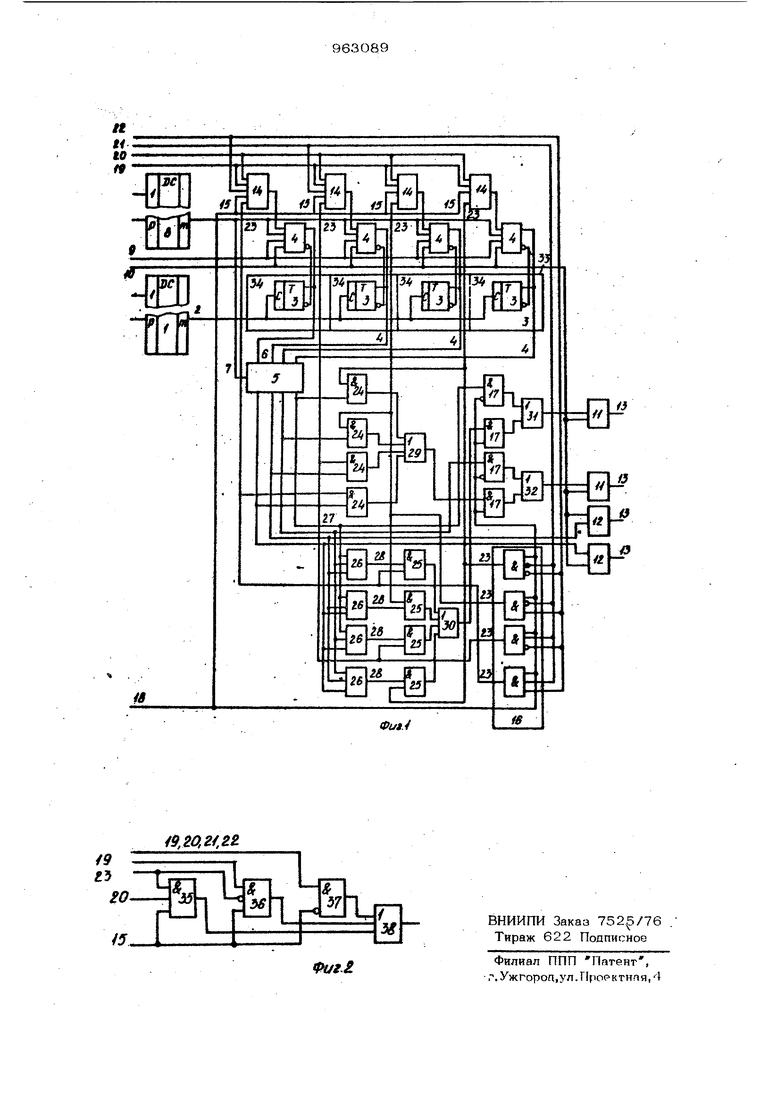

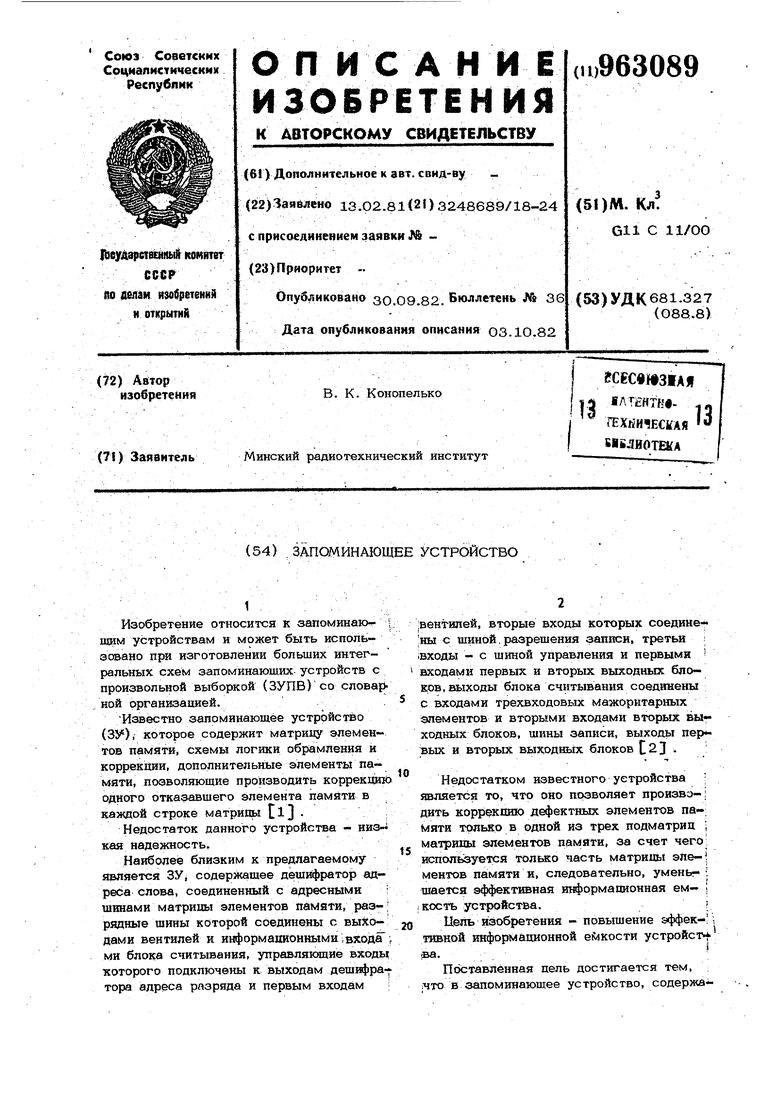

Поставленная цель достигается тем, |Что в запоминающее устройство, содержа uiee дelu fфpaтopы адреса, мажоритарные элементы, блок считывания, первую труп- 1ту улементов И, блоки вывода данных и элементы , адресные входы которы соединены с выходами первого дешифратора адреса, инверсные входы элементоЕ памяти подключены соответственно к инБерс;ным выходам элементов И первой группы, прямые выходы которых соедиг- нены с выходами элементов памяти и ин формационными входами блока считывания управляющие входы которого подключены к выходам второго дешифратора адреса и первым входам элементов И первой группы, входы мажоритарных элементов соеди нены с выходами блока считывания, одни из выходов которого подключены к первы входам одних из блоков вывода данных, Вторые входы элементов И первой группы объединены и являются входом ршзре{цения записи устройства, а третьи входы являются управляющим входом устройства и соединены со вторыми входами одних и перюыми входами других блоков вывода данных, введены, дешифратор исправных ячеек памяти, вторая, третья и четвертая группы элементов И, элементы ИЛИ и ло гические блоки,, первые входы которых объединены и являются уходом стробкрО вания устройства, вторые, третьи и четвертые входы логических блоков являются входами записи устройства, а выходы под ключены Соответственно к четвертым вхо дам элементов И первой группы, первый и второй входы дешифратора исправных ячеек памяти соединены с четвертыми входами одних из логических блоков, а стробирующий вход соединен с первыми входами элементов И второй группы и первыми входами логических блоков, пятые входы которых подключены к выхода дешифратора исправных ячеек памяти и первь1м входам элементов И третьей и четвертой групп, выходы которых соединены с входами первого и второго элемен тов Р1ДИ соответственно, выходы которых подключены соответственно ко вторым входам одних из элементов И второй груп пы, выходы которых соединены с первым входами третьего и четвертого элементов ИЛИ соответственно, выходы которых подключены ко вторым входам других блоков вывода данных, а вторые входы - к выходам других элементов И второй группы, вторые входы которых соединены со вторыми входами одних из элементов И третьей.группы и другими выходами блока счнтьшания, одни из выходов которого подключены ко вторым входам дру- гих элементов И третьей группы, вторые входы элементов И четвертой группы соединены с выходами мажоритарных элементов. Каждый логический блок содержит элементы И.и пятый элемент ИЛИ, входы которого подключены к выходам элементов И, причем первые входы первого и второго элементов И и инверсный вход третьего элемента И объединены и являются первым входом блока, вторым и трютьим входами которого являются соответственно прямой вход третьего элемента И и второй вход второго элемента И, второй вход первого элемента И-является четвертым входом блока, пятым входом и выходом которого являются соответственно третьи входы первого и второго элементов И и выход пятого элемента ИЛИ. Ыа фиг. 1 приведена функциональная схема предлагаемого устройства ; на фиг. 2 функшюнальная схема логического блока. Устройство содержит первый дешифратор 1 адреса, предназначенный для дешифрации адреса слова, с выходами 2, апементы 3 памяти, элементы И 4- первой группы, блок 5 считывания с информационными 6 и управляющими 7 входами, второй дешифратор 8 адреса, предназначенный для дешифрации адреса разряда, вход 9 разрешения записи и управляюн;ий вход 10 устройства, блоки 11 и 12 вывода данных с выходами 13, логические блоки 14 с первыми входами 15, дешифратор 16 исправных ячеек памяти, элементы И 17 второй группы, вход 18 стробирования и входы 19 - 22 записи устройства и пятые входы 23 логических блоков, третью 24 и четвертую 25 группы элементов И, мажоритарные элементы 26 с входами 27 и. выходами 28, первый 29, второй 30, третий 31 и четвертый 32 элементы ИЛИ. Элементы памяти организованы в матрицу 33, разделенную на подматрицы 34. Каждый логический блок содержит (фиг. 2) первый 35, второй 36 и третий 37 элементы И и пятый элемент ИЛИ 38. Устройст во работает следующим образом. Работу устройства рассмотрим на примере ЗУПВ с четырьмя одновременно опрашиваемыми и образующими одну подматрицу элементами 3 памяти матрицы 33 (см. фиг. 1), т. е. когда из каждой из четырех подматриц 34 одновременно опрашивается по одному элементу 3 памяти. В случае когда матрица 33 (фиг. 1) исправна ПОЛИОСТЕ Ю или на три четверти (в одной из подматриц 34 есть хотя б один отказавший элемент 3 памяти) или наполовину (отказавшие элемеЕ{ты 3 памяти есть в двух подматрицах 34), работа устройства .происходит обычным образом. При записи информации на соответст вующие входы 19 - 22 устройства подаются сигналы записи на входы 9 и 10 разрешения записи и управления. На вход 18 подается нулевой потенциал. При этом в логических блоках 14 элементы И 35 и 36 (фиг. 2) закрыты, а сигналы с соответствующих входов 19 - 22 поступаю через открытые элементы И 37 на входы соответствующих элементов И, Тем самым в опрашиваемые элементы памяти 3 подматриц 34 опрашиваемого слова матри- цы 33 происходит запись входной инфор- мадии. В режиме считывания сигналы по входам 9 и 19 - 22 отсутствуют. При этом элементы И закрыты , а сигналы о состоянии опрашиваемых элементов 3 памя- ти поступают с выходов блока 5 считывания на выходы 13 устройства без изменения, поскольку нулевой сигнал на входе 18 держит закрытыми дешифратор 16 и элементы И 17. В случае, когда в матрице 33 элемен тов 3 памяти исправна только одна подматрица 34, а в остальных трех подматрицах 34 имеется не более одного отказав шего элемента 3 памяти из трех одно- временно опрашиваемых для каждого слова, работа устройства происходит следующим образом. На вход 18 подается единичный сигнал. На входы 21 и 22 подаются сигналы, которые указывают какая из подматриц 34 исправна. Например, сигналы ОО, 10, О1, 11 указывают соответствен но, что исправными являются первая, вторая, третья или четвертая подматрицы 34 матрицы 33. Тогда в режиме записи, информации при подаче сигналов записи на входы 19 и 20 и 9 и 10 в соот ветствии с сигналами на входах дешифра торов 1 и 8 происходит запись информации в опрашиваемые элементы 3 памят матрицы 33. При этом на одном из выходов дешифратора 16 устанавливается единичный сигнал, который открывает элемент И 35 в одном из блоков 14. и входная информация, поступающая по входу 20, заносится для хранения в элемент 3 памяти исправной матрицы 34. Одновременно в три другие подматрицы 34 заносится для храисЕшя информация, поступающая по входу 19. поскольку элементы И 36 в блоках 14 открыты нулевыми сигналами на входах 23 с соот ветствующих выходов дешифратора 16. В режиме считывания сигналы на входах 19, 2О и 9 отсутствуют. При этом элементы И 4 закрыты, а сигналы о состоянии опрашиваемых элементов 3 памяти матрицы 33 поступают с выходов блока 5 на вторые входы элементов И 24 и входы 27 мажоритарных элементов 26. На выходе одного из мажоритарных элементов 26 появляется правильный сигнал, считываемый с трех дефектных подматриц 34, у которых в опрашиваемом слове имеется не более одного отказавшего элемента 3 памяти согласно условию отбраковки при изготовлении устройства. Этот правильный сигнал поступает ни вход одного из элементов И 25, .который открыт сигналом с одного из выходов дешифратора 16. Одновременно этот сигнал открывает и один из элементов И 24, тем самым выделяя сигнал с опрашивае- мого элемента 3 памяти исправной подматрицы 34. Оба этих правильно считанных сигнала поступают через элементы ИЛИ 29 и ЗО, одни из элементов И 17, элементы ИЛИ 31 и 32 и блоки 11 .на выходы устройства. Сигналы, с выходов блока 5 считывания не поступают на выходы устройства, поскольку они поступают на входы закрытых сигналом на входе 18 других элементов И 17. В случае, когда в матрице 33 элементов 3 памяти нет полностью исправнььх подматриц 34, но имеется, как минимум три подматрицы 34, в которых имеется не более одного отказавшего элемента 3 памяти из трех одновременно опрашиваемых для каждого слова, работа устройств ва происходит аналогично вышеописанному случаю. На вход 18 подается единичный сигнал. На входы 21 и 22 подаются сигналы, указывающие, какая из подматриц 34 не используется. Сигнал записи подается на вход 19 и снимается с одного из выходов 13 устройства. Таким образом предлагаемое устройство, вьшолняя те же функции хранения информации, что и известное, позволяет использовать устройства с одной четвер-р тью от полной емкости матрицы элементов памяти при условии, то имеется как минимум при подматрицы 34 из четырех дефектных, в которых имеется не более одного отказавшего элемента памяти из трех одновременно опрашиваемых для каждого слова. При производстве извест вые устройства при таких условиях рас положения откакэавших элементов памяти .отбраковываются, поскольку при эксплуата шш неизвесуно на позициях расположены отказавшие элементы памяти. Тех нико-экономическое преимущество предлагаемого ЗУ заключается в том, что оно позволяет увеличить используемую информанионную емкость в два раза по сравнению с прототипом при условии, что имеет ся одна полностью исправная подматрица, а в остальных трех подматринах имеется не более одного отказавшего элемента памяти из трех одновременно опрашиваемых для ка одого слова, тогда как в прототипе при таких условиях расположения очтсазавших элементов памяти использовалась только одна четверть информационно емкости. Форм у-П а изобретения 1. Запоминающее устройство, содер йсашее дешифраторы адреса, мажоритарные элементы, блок считьшания, первую группу элементов И, блоки вьшода данных и элементы памяти, aдpeo tыe входы которы соединены с выходами первого дешифратора адреса, инверсные входы эдементо памяти подключены соответственно к инверсным выходам элементов И первой группы, прямые выходы которых соедине- ,ны с выходами .элементов памяти и инфор мадионными входами блока считывания, :управляюшие входы которого подключены к выходам второго дешифратора адреса и первым входам элементов И первой группы, входы мажоритарных элементов со-г единены с выходами блока считывания, ;одни из выходов которого подключены к первым входам одних из блоков вьгоода данных, вторые входы элементов И пер;Вой группы объединены и являются входов разрешения х записи устройства, а третьи входы являются управляющим входом устройства и соединены со вторыми входами одних и первыми входами других блоков вывода данных, отличающееся тем, что, с целью повьпиения эффективной информационной емкости, оно содержит дешифратор исправных ячеек памяти, вто рую, третью и четвертую группы элементов И, элементы ИЛИ и логические блоки первые входы которых объединены и явля ртся входом стробирования-устройства вторые, третьи и четвертые входы логиЧеских блоков являются входами записи устройства, а выходы подключены соответственно к четвертым входам элементов И первой группы, первый и второй Входы дешифратора исправных ячеек памяти соединены с четвертыми входами одних из логических блоков, а стробирующий вход соединен с первыми входами элементов И второй группы и первыми входами логических блоков, пятые входы которых подключены к выходам дешифратора исправНых ячеек памяти и первым входам элементов И третьей и четвертой групп, выходы которых соединены- с входами первого и второго элементов ИЛИ соответственно, выходы которых подключены соответственно ко вторым входам одних из элементов И второй группы, выходы .которых соединены с первыми входами третьего и четвертого элементов ИЛИ соответственно, выходы которых подйлючены -ко .вторым входам других блоков вывода данкых, а вторые входы - к выходам других элементов И второй группы, вторые входы которых соединены со вторыми входами одних из элементов И третьей группы.и другими выходами блока считывания, одни из выходов которого подключены ко вторым входам других элементов И третьей группы, вторые входы элементов И четвертой группы, соединены с выходами ,мажоритарных элементов. . 2, Устройство по п. 1, о т л и ч а ющ е ее я тем, что каждый логический блок содержит элементы И и пятый элемент ИЛИ, входы которого подключены к выходам элементов И, причем первые входы первого и второго элементов И и -инверсный вход третьего элемента И. объединены и являются первым входом блока, вторым и третьим входами которого являются соответственно прямой вход третьего элемента И и второй вход второго элемента И, второй вход первого элемента И вляется четвертым входом блока, пятым входом и выходом которого являются соответственно третьи входы первого и вто iporo элементов И и вькод пятого элемен;та ИЛИ.. Источники информаиии, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 746741, кл. Gil С 11/00, 1978. 2.Городний А. В., Корнейчук В. И; Проблемы высоконадежной памяти. - Автоматика и телемеханика, 1974, № 7, с, 160 (прототип).

Авторы

Даты

1982-09-30—Публикация

1981-02-13—Подача