Изобретение относится к вычислительной технике и может быть использовано при изготовлении больших интегральных схем запоминающих устройств с произвольной выборкой и матричной организацией (ЗУПВ).

Известны ЗУПВ с матричной организацией, которые содержат матрицу элементов памяти, схемы логики обра ления и коррекции дополнительные элементы памяти fl}.

Недостатком этих устройств является низкая надежность из-за коррекции только однократных ошибок в слове и необходимости введения дополнительш11х элементов памяти и сложности схем коррекции.

Наиболее близким к изобретению по технической сущности и схемному решению является запоив нающее устройство, содержащее дешифратор адреса, блок считывания, шины управления и записи считывания, элементы И, ИЛИ, накопитель и позволякхцее повысить надежность запоминающего устройства за.счет корэкции дефектов элементов памяти

Недостатком устройства является низкая надежность устройства изза возможности возникновения оши- бок в различных частях накопителя.

Цель изобретения - повышение надежности устройства за счет обеспечения возможности использования запоминающего устройства с дефекта

в различных частях накопителя. I

Поставленная цель достигается

тем, что запоминаюцее устройство, содержащее накопитель, первая груп входов которого является адресными входами первой группы устройства, входы второй группы накопителя соединены с выходами первой гру пы блока элементов И и со входами первой группы блока усилителей считывания, входы второй группы которого соединены с выходами второй группы блока элементов И и с выходами накопителя, выходы блока усилителей считывания соединены с со входами элемента ИЛИ и входами первой группы блока мажоритарных элементов, входы, второй группы которого являются адресными входа1 ш второй группы устройства, а выходы соединены со входами селектора, выходы которого соединены с первьАм входом первого коммутатора, второй вход которого соединен с выходом элемента ИЛИ, а выход является информационным вызсодсви устройства, дешифратор, первая группа входов, которого является адресными входами третьей группы устройства, первый,второй и третий управляющие входы блока элементов И являются первым,вторым, третьим управляющим входом устройства, третий вход первого коммутатора соединен с первым управляющимвходом блока , элементов И, дополнительно содержит блок формирователей четности второй кои утатор, элемент И, инвертор, блок адресных формирователей, входы первой и второй групп которого соединены с выходами дешифратора, входы второй группы которого соединены с выходами второго коммутатора, управлякнций вход которого соединен с первым управляющим входом блока адресных формирователей и выходом инвертора, вход

5 которого соединен.с-первым входом элемента И и является четвертым управляющим входом устройства, выход элемента И соединен с четвертым входом первого коммутатора, а втоQ рой вход соединен с первым входом второго коммутатора и является первым старшим адресным входом устройства, второй вход второго сумматора является вторым стаЕниим ад5 pecHbw входом устройства, второй вход блока адресных формирователей является пятым управляющим входом устройства, входы блока формирователей четности соединены с входами второй группы устройства, а выходы

0,соединены со входами блока элементов И.

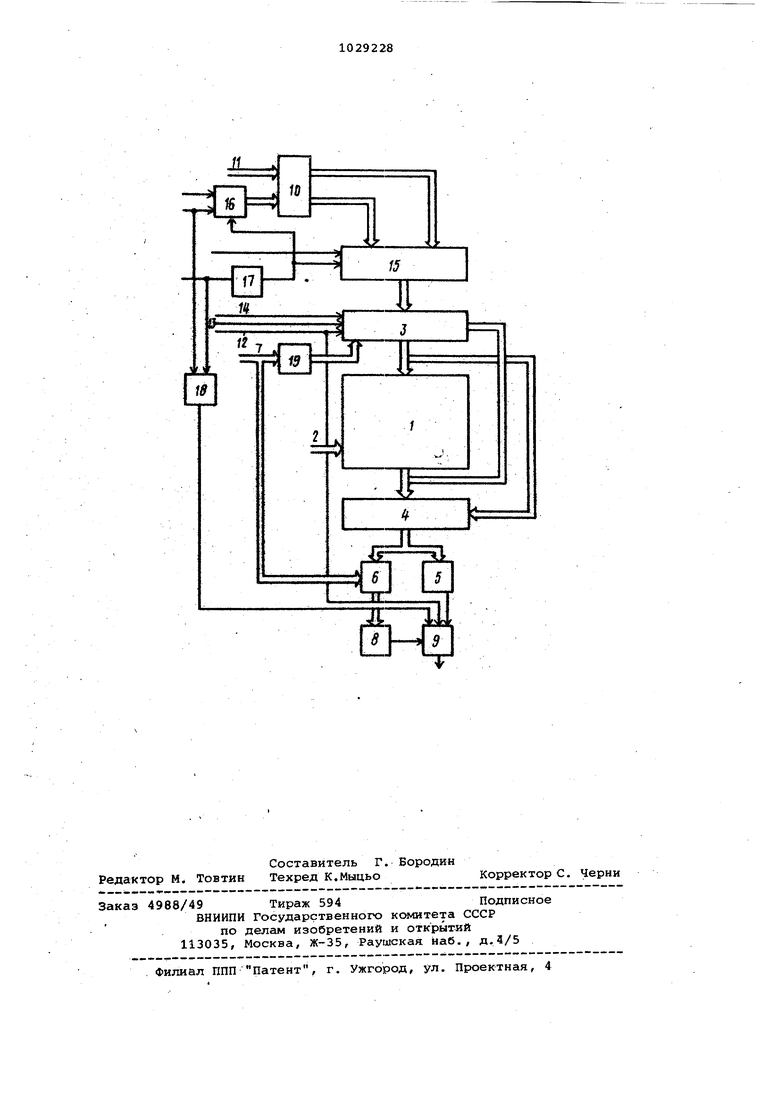

На чертеже представлена функциональная схема запоминающего устройства.

Запоминающее устройство содержит накопитель 1, перваягруппа входов которого является адресными входами 2 устройства первой группы, входы второй группы накопителя 1

0 соединены с выходами первой группы блока элементов И 3 и со входами первой группы блока усилителей считывания 4, входы второй группы которого соединены с выходами второй

5 группы блока элементов И 3 и с выходами накопителя 1, выхор}л блока усилителей считывания 4 соединены со входами элемента ИЛИ 5 и входами первой группы блока маикоритарных

П элементов 6, входы второй группы которого являются адресными входа-, ми второй группы 7 устройства, а выходы соединены со входами селектора S: выходы которого соединвны с первым входом первого коквиутатора 9,

второй вход которого соединен с выI кодом элемента ИЛИ 5 и выход является информационным шлходом устройства, дешифратор 10, первая группа входов которого является адрес0 НШ4И входами третьей группы 11 уст- ройства, первый, второй и третий управляющие входы блока элементов И 3 являются первым 12, вто(%ш 13 и третьим 14 управляющим входами устройства, третий вход первого коммутатора 9 соединен с первым 12 управлгощим входом блока элементов ИЗ, блок адресных формирователей 15, входы первой и второй групп которого соединены с выходами дешифратора 10, входы второй группы которого соединены с выходгши второг коммутатора 16, управляющий вХод которого соединен с первым управляК8ЦИМ входом блока ад1 есных формирователей 15 и выходом инвертора 17, вход которого соединен с первым входом элемента И 18 и язля&тся четвертым управляющим входом устройства, клход элемента И 18 содинен с четвертым входом первого коквлутатора 9, а второй вход соед нен с первым входом второго ксалмутатора и является первым старшим адресным входом устройства, второй вход второго коммутатора 16 является вторлм старшим адресньм входом устройства, второй вход блока адресных формирователей 15 является пятым управлякяцим входом устройства, выходы блока формирователей четности 19 соединены с входами второй группы 7 устройства, а выходы соединены со входами блока элементов И 3.

Устройство работает следующим образом.

В случае, когда накопитель полностью исправен или исправны три его четверти, или половина его накопителя, то. работа происходит . образом.

в сзлучае, когда в накопителе исправна только одна четверть, а в осталышх трех подматрицах имеется не-более одного отказавшего эле мента памяти из трех одновременно опрашиваега:ах элементов памяти для каждого слова, работа устройства происходит следующим образом.

На пятый управляющий вход устройства подается единичный сигнал, на входы 7 - сигналы, которые указывают какая из подматриц исправна. Тогда в режиме записи информа1улк при подаче сигналов на шины

разрешения записи 14, записи 13, управления 12 в соответствии с сигналом на шинах 2 и сигналом на старшем адресном входе устройства на входах 11 дешифратора 10 происходит запись информации в опргиииваемых блоком адресных формирователей элементах Пс1мяти. При этом, если на старшем адресном входе имеется ну-левой сигнал, то опрашивается эле0мент памяти из исправной подматришл. Если на этом входе будет единичный сигнал, то опрашивается одновременно три элe 4eнтa памяти ( поодному из дефектных подататриц по

5 адресу определяемому с выходов дешифратора 10, поскольку при этом в формирователях четности 19 происходит инвертирования сигнала со входов 7. Тогда сработают соответствукщие фс ЕФШрователи из блока 15 и произ ;х11яет запись информации.

В режиме считнваиия сигналы по шинам 13 и 14 отсутствуют. При этом если на старшем адресном сигнале единичный сигнал,, то опрашиваются

5 элементы памяти из дефектных подматриц. Информация, считываемая и трех дефектных подалатриц, поступает на входы мажефитарных элементов б и на элемгиты ИЛИ 5. На одном иэ выходов мажоритарных элементов памяти появится правильный сигнал. С помощью селектора 8 и коммутатора 9 осуществляется выдача его. на выходустройства.

5

В случае, когда в матрице памяти нет полностью исправной подматрицы, но имеется как минимум три подматрицы, в которых содержится не более одного отказавшегчэ .элемента пгкмятинз трех одновременно опра0шивае1Ф2К, работа устройства происходит аналогично описанному, только на входов 7 подаются сигналы, которые указьшают, какие из подматриц не «споль зуются.

5

Такюв образом возможно использование устр&йства с дефектными элемента14и, что свидетельствует о повышении надежности устройства.

18

16

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Запоминающее устройство с коррекцией информации | 1981 |

|

SU957273A1 |

| Запоминающее устройство | 1981 |

|

SU963089A1 |

| Резервированное запоминающее устройство | 1986 |

|

SU1417041A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| Постоянное запоминающее устройство с самоконтролем | 1984 |

|

SU1274005A1 |

| Модульное запоминающее устройство с коррекцией ошибок | 1985 |

|

SU1320848A1 |

| Запоминающее устройство с самоконтролем /его варианты/ | 1984 |

|

SU1272358A1 |

| Динамическое полупроводниковое запоминающее устройство | 1979 |

|

SU1001173A1 |

гЧЗ

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Запоминающее устройство | 1975 |

|

SU746741A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1983-07-15—Публикация

1981-11-23—Подача