блока и соединен с выходом второго элемента И, второй вход третьего элемента И является четвертым выходом блока.

3. Устройство по п. 1, отличающееся тем, что блок анализа ошибок содержит первый и второй D-триггеры, сумматор но модулю два, четвертый, нятый, шестой, седьмой, восьмой, девятый, десятый элементы И и третий элемент ИЛИ, выход которого соединен с нервым входом четвертого элемента И, второй вход которого соединен с первым входом пятого, первым входом inecToro элементов И и является вторым входом блока, первый вход блока соединен соответственно с первым входом седьмого, вторым входом восьмого и вторым входом шестого элементов И, третий вход которого соединен с третьим входом седьмого элемента И, первым входом восьмого элемента И, вторым входом девятого элемента И, первым входом десятого элеИзобретение относится к вычислительной технике, а именно к запоминающим устройствам, и может быть использовано для повышения быстродействия устройства при отбраковке микросхем.

Цель изобретения - повьииение быстродействия устройства.

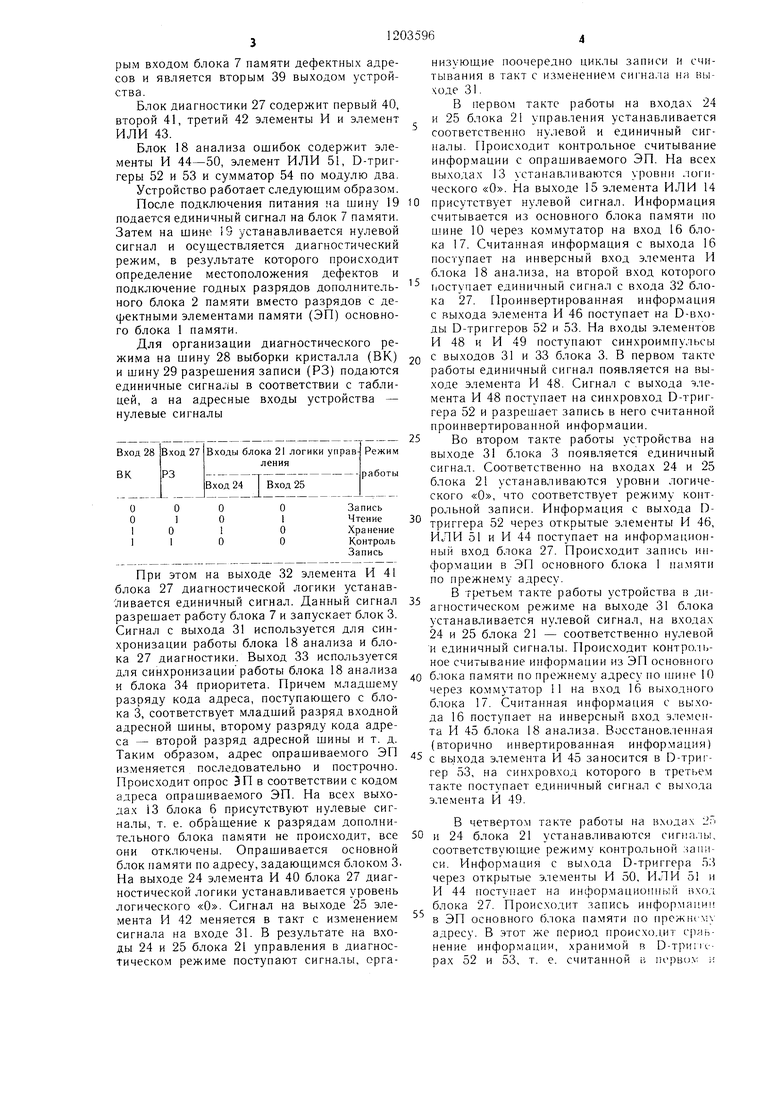

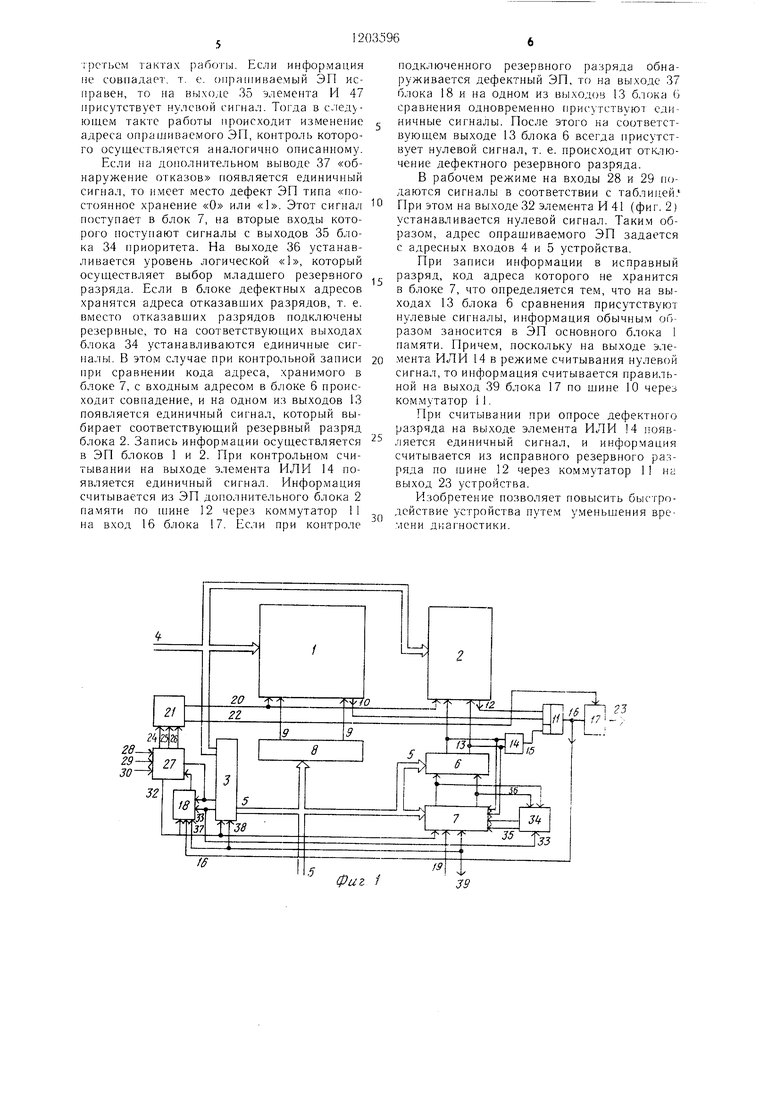

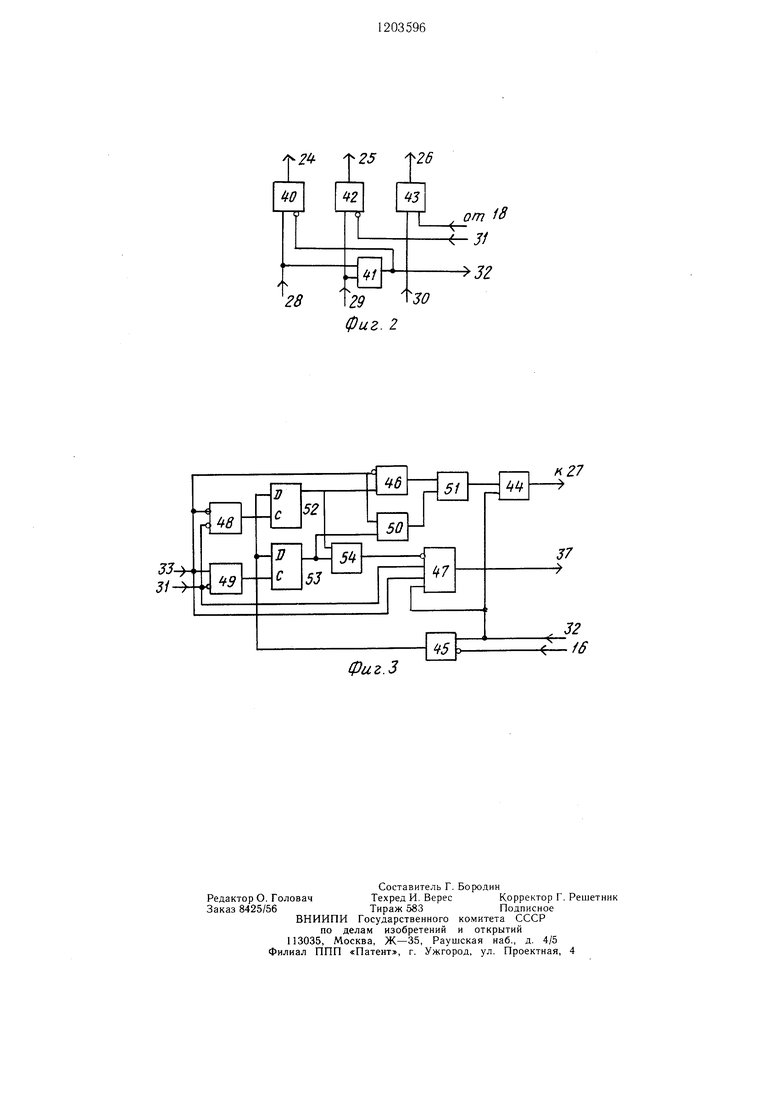

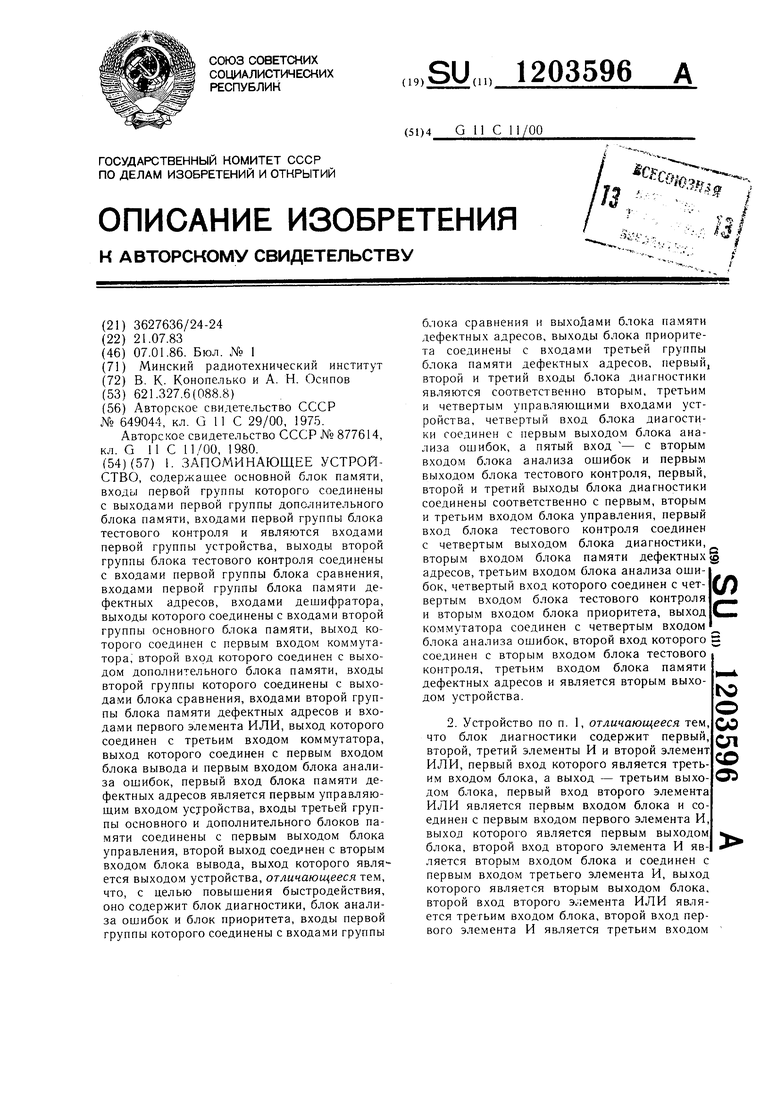

На фиг. представлена блок-схема за- по.минаюш.его устройства; на фиг. 2 - функциональная схема блока диагностики; на фиг. 3 - функциональная схема блока анализа .

Запоминаюшее устройство содержит основной блок 1 памяти, входы первой группы которого, соединены с входами первой группы дополнительного блока 2 памяти, выходами первой группы блока 3 тестового контроля и являются входами первой группы 4 устройства, выходы второй группы 5 блока 3 тестового контроля соединены с входами первой группы блока 6 сравнения, входами первой группы блока 7 памяти дефектных адресов, входами дешифратора 8, выходы 9 которого соединены с входами второй группы основного блока 1 памяти, выход 10 которого соединен с первым входом коммутатора 11, второй вход которого соединен с выходом 12 дополнительного блока 2 памяти, входы второй группы которого соединены с выходами 13 блока 6 сравнения, входами второй группы блока 7 памяти дефектных адресов и входами первого ИЛИ 14 элемента, выход 15 которого соединен с третьим входом коммутатора 11, выход 16 которого соединен с нервым входом блока 17 вывода, первым

мента И и является третьим входом блока, четвертый вход блока соединен с вторым входом пятого элемента И, выход пятого э. гемента И соединен с D-входами первого и второго D-триггеров, выход первого D- триггера соединен с первым входом девятого элемента И и первым входом сумматора по модулю два, выход которого соединен с вторым входом шестого элемента И, выход второго D-триггера соединен с вторым входом сумматора по модулю два и вторым входом десятого элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, второй вход третьего элемента ИЛИ соединен с выходом девятого элемента И, выходы седьмого и восьмого элементов И соединены соответственно с синхровходами первого и второго D-триггеров, выход ujecTO- го элемента И и является вторым выходом блока.

входом блока 18 анализа ошибок, первый 19 вход блока 7 памяти дефектных адресов является первым управляющим входом устройства, входы третьей группы основного 1 и дополнительного 2 блоков памяти соединены с первым выходом 20 блока 21 управления, второй выход 22 которого соединен с вторым входом блока 17 вывода, выход которого является нервым выходом 23 устройства, первый 24, второй 25 и третий 26 выходы блока 27 диагностики соединены с соответствующими входами блока 21 управления, первь й, второй и третий входы блока 27 диагностики являются вторым 28, треть им 29 и четвертым 30 управляющими входами

5 устройства, четвертый вход блока 27 диагностики соединен с первым выходом блока 18 анализа ошибок, пятый вход 31 блока диагностики соединен с вторым входом блока 18 анализа ошибок и первым выходом блока 3 тестового контроля, первый вход блока 3

0 тестового контроля, соединенный с четвертым 32 выходом блока 27 диагностики, вторым входом блока 7 памяти дефектных адресов, третьим входом блока 18 анализа ошибок, четвертый вход которого соединен с вторым 33 выходом блока 3 тестового контроля и входом блока 34 приоритета, выходы которого соединены с входами третьей 35 группы блока памяти дефектных адресов, а входы соединены с входами второй группы блока сравнения и выходами 36 блока 7 памяти

дефектных адресов, четвертый выход 37 блока 18 анализа ошибок соединен с вторым входом 38 блока 3 тестового контроля, вторым входом блока 7 памяти дефектных адресов и является вторым 39 выходом устройства.

Блок диагностики 27 содержит первый 40, второй 41, третий 42 элементы И и элемент ИЛИ 43.

Блок 18 анализа ошибок содержит элементы И 44-50, элемент ИЛИ 51, D-триг- геры 52 и 53 и сумматор 54 по модулю два.

Устройство работает следующим образом.

После подключения питания иа шину 19 подается единичный сигнал на блок 7 памяти. Затем на шиж- iS устанавливается нулевой сигнал и осуш,ествляется диагностический режим, в результате которого происходит определение местоположения дефектов и подключение годных разрядов дополнительного блока 2 памяти вместо разрядов с дефектными элементами памяти (ЭП) основного блока 1 памяти.

Для организации диагностического режима на шину 28 выборки кристалла (ВК) и шину 29 разрешения записи (РЗ) подаются единичные сигналы в соответствии с таблицей, а на адресные входы устройства - нулевые сигналы

При этом на выходе 32 элемента И 41 блока 27 диагностической логики устанав- ливается единичный сигнал. Данный сигнал разрешает работу блока 7 и запускает блок 3. Сигнал с выхода 31 используется для синхронизации работы блока 18 анализа и блока 27 диагностики. Выход 33 используется для синхронизации работы блока 18 анализа и блока 34 приоритета. Причем младшему разряду кода адреса, поступаюшего с блока 3, соответствует младший разряд входной адресной шины, второму разряду кода адреса - второй разряд адресной шины и т. д. Таким образом, адрес опрашиваемого ЭП изменяется последовательно и построчно. Происходит опрос ЗП в соответствии с кодом адреса опрашиваемого ЭП. На всех выходах 13 блока 6 присутствуют нулевые сигналы, т. е. обрашение к разрядам дополнительного блока памяти не происходит, все они отключены. Опрашивается основной блок памяти по адресу, задающимся блоком 3. Па выходе 24 элемента И 40 блока 27 диагностической логики устанавливается уровень логического «О. Сигнал на выходе 25 элемента И 42 меняется в такт с из.менением сигнала на входе 31. В результате на входы 24 и 25 блока 21 управления в диагностическом режиме поступают сигналы, организующие поочередно циклы записи и считывания в такт с изменением сигнала ня кы- ходе 31.

В первом такте работы на входах 24 и 25 блока 21 управления устанавливается соответственно нулевой и единичный сигналы. Происходит контрольное считывание инфор.мации с опрашиваемого ЭП. Па всех выходах 13 х станавливаются уровни .логического «О. На выходе 15 элемента ИЛИ 14

0 присутствует нулевой сигнал. Информация считывается из основного блока памяти по шине 10 через коммутатор на вход 16 блока 17. Считанная информация с выхода 16 поступает на инверсный вход элемента И блока 18 анализа, на второй вход которого

гюступает единичный сигнал с входа 32 блока 27. Проинвертированная информация с выхода элемента И 46 поступает на D-BXO- ды D-триггеров 52 и 53. На входы элементов И 48 и И 49 поступают синхроимпульсы

Q с выходов 31 и 33 блока 3. В первом такте работы единичный сигнал появляется на выходе элемента И 48. Сигнал с выхода элемента И 48 поступает на синхровход D-триг- гера 52 и разрешает запись в него считанной проинвертированной информации.

5 Во втором такте работы устройства на выходе 31 блока 3 появляется единичный сигнал. Соответственно на входах 24 и 25 блока 21 устанавливаются уровни логического «О, что соответствует режиму контрольной записи. Информация с выхода D- триггера 52 через открытые элементы И 46, ИЛИ 51 и И 44 поступает на инфор.мацион- ный вход блока 27. Происходит запись информации в ЭП основного блока 1 памяти по прежнему адресу.

В третьем такте работы устройства в диагностическом режиме на выходе 31 блока устанавливается нулевой сигнал, на входах 24 и 25 блока 21 - соответственно нулевой и единичный сигналы. Происходит контрольное считывание информации из ЭП основного

0 блока памяти по прежнему адресу по шине 10 через коммутатор 11 на вход 16 выходного блока 17. Считанная информация с выхода 16 поступает на инверсный вход элемента И 45 блока 18 анализа. Восстановленная (вторично инвертированная инфор.мация)

5 с вь1хода элемента И 45 заносится в D-триггер 53, на синхровход которого в третьем такте поступает единичный сигнал с выхода элемента И 49.

В четвертом такте работы на нхода.х 25 0 и 24 блока 21 устанавливаются сигнп.чы, соответствующие режиму контрольной .записи. Информация с выхода D-триггера 53 через открытые элементы И 50, ИЛИ 5 и И 44 поступает на информацио1 1 ыи ivxo.i блока 27. Происходит запись информани в ЭП основного блока памяти по прсжнсмч адресу. В этот же период происходит сряь- нение информации, хранимой в О-трипч-- рах 52 и 53, т. е. считанной в нервом ;:

0

гретьем тактах работы. Если информация не совпадает, т. е. опрашиваемый ЭП исправен, то на выходе 35 элемента И 47 присутствует нулевой сигнал. Тогда в следу- кядем такте работы происходит из.менеиие адреса опраши аемого ЭП, контроль которого осуществляется аналогично описанному. Если на дополнительном выводе 37 «обнаружение отказов появляется единичный сигнал, то имеет место дефект ЭП типа «постоянное хранение «О или «1. Этот сигнал поступает в блок 7, на вторые входы которого поступают сигналы с выходов 35 блока 34 приоритета. На выходе 36 устанавливается уровень логической «1, который осуществляет выбор младщего резервного разряда. Если в блоке дефектных адресов хранятся адреса отказавших разрядов, т. е. вместо отказавших разрядов подключены резервные, то на соответствующих выходах блока 34 устанавливаются единичные сигналы. В этом случае при контрольной записи при сравнении кода адреса, хранимого в блоке 7, с входным адресом в блоке 6 происходит совпадение, и на одном из выходов 13 появляется единичный сигнал, который выбирает соответствующий резервный разряд блока 2. Запись информации осуществляется в ЭП блоков 1 и 2. При контрольном считывании на выходе элемента ИЛИ 14 появляется единичный сигнал. Информация считывается из ЭП дополнительного блока 2 памяти по 1пине 12 через коммутатор 11 на вход 16 блока 17. Если при контроле

j. 0 -

подключенного резервного разряда обнаруживается дефектный ЭП, то на выходе 37 блока 18 и на одном из выходов 13 блока 6 сравнения одновременно присутствуют единичные сигналы. После этого на соответствующем выходе 13 блока 6 всегда присутствует нулевой сигнал, т. е. происходит отключение дефектного резервного разряда.

В рабочем режиме на входы 28 и 29 подаются сигналы в соответствии с таблицей. При этом на выходе 32 элемента И 41 (фиг. 2) устанавливается нулевой сигнал. Таким образом, адрес опрашиваемого ЭП задается с адресных входов 4 и 5 устройства.

При записи информации в исправный разряд, код адреса которого не хранится в блоке 7, что определяется тем, что на выходах 13 блока 6 сравнения присутствуют нулевые сигналы, информация обычны.м образом заносится в ЭП основного блока 1 памяти. Причем, поскольку на выходе элемента ИЛИ 14 в режиме считывания нулевой сигнал, то информация считывается правильной на выход 39 блока 17 по шине 10 через ком.мутатор 11.

При считывании при опросе дефектного разряда на выходе элемента ИЛИ 4 появляется единичный сигнал, и информация считывается из исправного резервного разряда по шине 12 через коммутатор 1 на выход 23 устройства.

Изобретение позволяет повысить быстродействие устройства путем уменьшения времени диагностики.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с обнаружением и исправлением ошибок | 1980 |

|

SU959167A1 |

| Сигнатурный анализатор | 1989 |

|

SU1714602A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU955209A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1725261A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| Сигнатурный анализатор | 1988 |

|

SU1580366A1 |

| Запоминающее устройство | 1975 |

|

SU746741A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU877614A1 |

| Запоминающее устройство | 1983 |

|

SU1107176A1 |

| Запоминающее устройство матричного типаС САМОКОНТРОлЕМ | 1979 |

|

SU849309A1 |

fs

фиг 1

I гз

33- 3iфиг. 2

фиг.З

| Запоминающее устройство | 1975 |

|

SU649044A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU877614A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-01-07—Публикация

1983-07-21—Подача