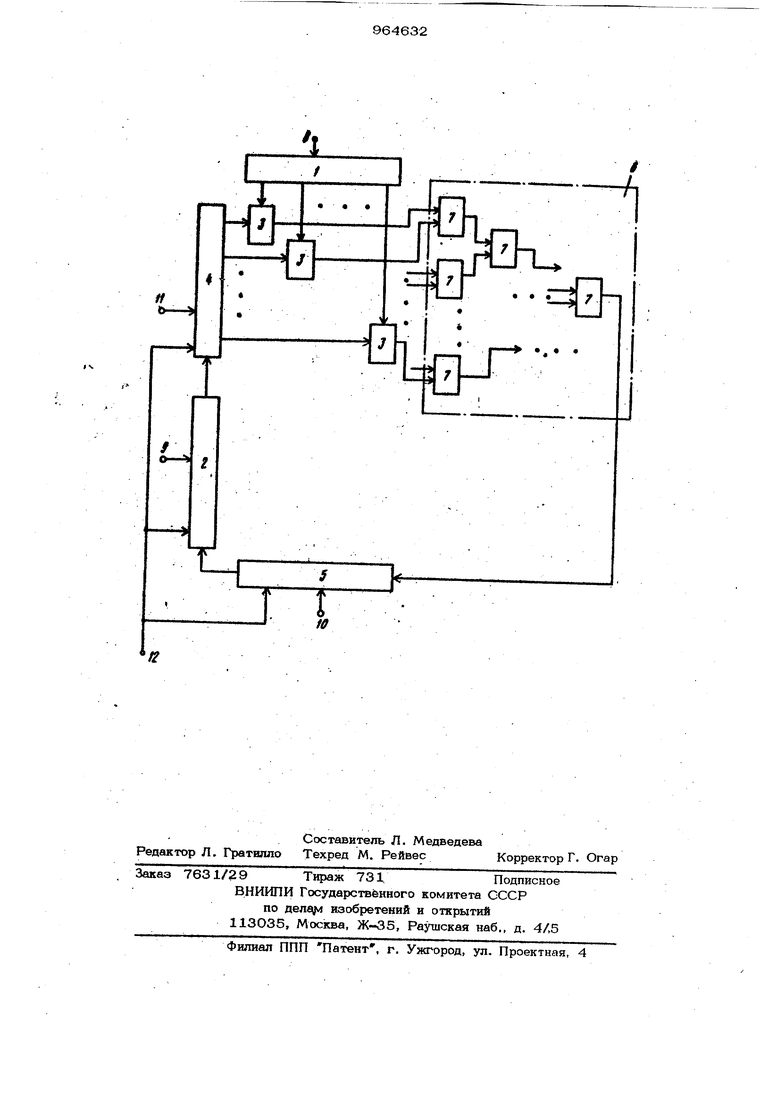

(54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ДВУХ И-РАЗРЯДНЫХ ЧИСЕЛ : 1 . Изобретение относится к вычислительной технике и может быть испольаованр в арифметических устройствах IBM и устро ствах обработки цифровой информации. Известно устройство для умножения двух у -разрядных чисел, содержащее мат рицу из элементов И, первый (2И-1)разрядный блок элементов ИЛИ, И -разрядный регистр множимого, (2И-1)-разрйдный сумматор, tl-разрядный I регистр множителя, первый и второй vi-разрядные блоки элементов И, второй И-разрядный блок элементов ИЛИ и h -разрядный блок элементов задержки 11 Недостатком указанного устройства является низкое быстродействие. Наиболее близким к изобретению по технической сущности является устройсч во для умножения двух И -разрядных чисел, содержащее Ц-разрядный регистр множимого, Vi-разрядный регистр множителя, V элементов И, и-разрядный сумма тор, причем информационные входы регист ра множимого и регистра множите являются соответственно входами первого и второго операндов устройства, вход синхронизации регистра множителя явл;яется входом синхронизации устройства, разрядные выходы регистра множимого соединены соответственно с первыми входами элементов И, выходы которых соединены Соответственно с входами сумматора ЗНедостатком этого устройства является низкое быстродействие при больщой разрядности сомножителей, так как задержка, вносимая сумматором в одном такте умножения, пропорциональна разрядности сомножителей. Целью изобретения является повьпиение быстродействия. Поставленная цель достигается тем, что в устройство введены два и -разрядных регистра, причем входы синхронизации первого и второго регистров соединены с входом син;фонизации р егистра множителя, входы сброса первого и второго регистров соединены с входом сброса уст ройств, Ьыход сумматора соединен с информационным входом первого регистра, выход младшего раэрйда которого соединен с входом регистра множителя, выход младшего разряда которого соединен с информационным входом второго регистра, раэрадные выходы которого соединены соответственно с вторыми входами эпе ментов И. На чертеже приведена структурная схема устройства для умножения двух П -раз 15ядных чисел.: Устройство содержит и-разрядный регистр 1 множимого и и-разрядный ре. гистр 2 множителя, .элементы И 3, регис ры 4 и 5, у -разрадный сумматор 6, . состоящий из пирамидально соединенных сумматоров 7 последовательного действия входы 8 и 9 операндов устройства, входы 1О и 11 сброса устройства, вход 12. синхронизации устройства. В устройстве информационные входы ., регистра 1 множимого-и регистра 2 множителя являются соответственно входами S и 9 операндов устройства, вход 12 син хронизахши устройства, разрядные выходы регистра 1 множимого соединены соответственно с первыми входами элементов ИЗ выходы которь{х соединены соответственно с входами сумматора 6, входы синхронизации регистров 4 и 5 соединены с вхо дами 10 и 11 сброса устройства; выход сумматора 6 соединен с информационным входом регистра 5, выход младшего разряда которого соединен с информационным -ВХОДОМ регистра 2 множителя, выход млад шего разряда которого соединен с йнфор мационным входом регистра 4, разрадные выходы которого соединены соответственно с вторыми входами элементов И 3, входы синхронизации регистров-4 и 5 соединены с входом синхронизации регис-г ра 2 множителя. Устройство работает следующим образом. Регистры 4 и 5 перед началом работы устройства устанавливаются в нулевое состояние. В регистр 1 множимого и регистр 2 множителя записываются соот ветственно множимое (О, Cf ..., Ci,, ..., ,) и множитель (Ъ, Ь .... bj, ... Ьу,). В первом такте производится сдвиг на один разряд содержимого регистров 2, 4 и 5, и на вход регистра 4 поступает младший разряд множители Ъу.С выхода И -го разряда регистра 4 на первый вход И НПО элемента И 3 поступает сигнал О или 1, соответствующий значению 96 24 младшего множителя Ь|. На второй вход И -го элемента И поступает сигнал Cfy с выхода .И-го разряда регистра 1 множимого. С выхода-:элемента И 3 сигнал, соответствующий коньюнкции , поступает на вход сумматора 6. С выхода сумматора 6 сигнал, соответствующий младшему разряду произведения, поступает на вход регистра 5. Во втором такте производится сдвиг на один разряд содержимого регистров 2, 4 и 5, и на вход регистра 4 поступает второй младший разряд множителя Dvi--f . Соответственно на первый вход И-го элемента И 3 поступает второй младший разряд множителя Ьу,, а на первый вход (И - 1)-го элемента И 3 первый младший разряд множителя Ъч- На вторые входы (И - 1)-го и И.-го элементов И 3 поступают соответртвенно разряды множимого CJy Сигналы, соответствующие коньюшсциям d j bpj.-f и CJyj.-ibM. с выходов элементов И 3 поступают на входы сумматора 6. В сумматоре 6 производится суммирование по модулю два ,C Ц ealoмккaнкe переноса в следующий разряд произведения происходит в одном из сумматоров 7 последовательного действия сумматора 6, С выхода сумматора б на вход регистра 5 поступает {2 1)-й разряд произведения. В следующих тактах производится поразрядный сдвиг содержимого регистров 2, 4 и 5. С выходов элементов И 3 сигналы, соотве1 ствующие коньюшсциям (3)5/. поступают на входы соответствующих разрядов сумматора 6. В сумматоре 6 производится суммирование по модулю два Й Ьис переносом из предыдущего разряда произведения. Запоминание переносов в Следующие разряды произведения происходит в сумматорах 7 последовательного действия сумматора 6. С выхода сумматора 6 на вход регистра 5 поступает соответствукяций разряд произведения. В {2i|1- 1)-м такте старший разряд множителя Ъ с выхода регистра 4 поступает на первый вход первого элемента И 3, на второй вход которого поступает старший разряд множимого . С выхода элемента И 3 сигналпоступает на вход сумматора 6. В сумматоре 6 производится сложение Q/j с переносом из предыдущего разряда произведения, С выхода -сумматора 6 эта сумма поступает на вход регистра 5. Перенос из (2И-1)-го разряда произведения поступает на выход сумматора 6 во 2-м такте, как самый старший разряд произведения. Таким образом, после 2ц-го такта в регистре 2 хранятся младшие разряды, а в регистре 5 - старшие разряды произведения. Конец операции умножения фиксируется по нулевому состоянию регистра 4, что позволяет сократить число тактов умно- . жения при числе разрядов множителя, меньшему . Предлагаемое устройство для умножения двух И -разрядных чисел является более быстродействующим по сравнению с известным устройством, время вьшолнения умножения -bj в котором определяется, следующим обрааом : t -время сложения двух И-разрядных чисел; Ьсдв- время сдвига М-разрядного чис Задержка, вносимая сумматором в одном такте умножения, пропорциональна разрядности сомножите хей, . т. е. , где t - задержка, вносимая синим разрядом сумматора в известном устройстве. Задержка, вносимая сумматором в одном такте ; умножения, в устройстве t определяется числом jCog С Уровней сумматоров последовательного действия ii--3eogr,j viB:2, где CjL - задержка, вносимая одним разрядом сумматора в предлагаемо устройтве. Время выполнения умножения в yeTpou стве T-ulопределяется следующим образом -fc д «1и-Ь in 3 tt: 2. Обычно величины ir , Тд и-1.д примерно равны. Тогда, так как функция V - il.. УЧ ta . ясвляется возрастающей с увеличением и уже при VI 4 становится больше едини пы, то, следовательно, при большей раз- рвдности сомножителей предлагаемое уст ройство является более быстродействующим, чем известное устройство. При И . 9 326 Кроме того, в реальных синхронных устройствах умножения время суммирования .и сдвига представляет собой один одинаковый, такт работы устройства управле- ния, синхронизирующего работу узлов операционной части. В этом случае -Чдв, 3Eogr,jMi: и уже при И 2 К 1, Ф о рмупа изобретения Устройство для умножения двух и-разрядных чисел, содержащее ц-Разрядный регистр множимого, и -разрядный регистр . множителя, и элементов И, и - раэрядный сумматор, причем информационные входы репютра множимого и регистра множителя яивляются соответственно входами первого и второго операндов устройства, вход синхронизации регистра множителя являет ся входом синхронизашш устройства, разрядные выходь регистра множимого соединены соответственно с первыми .входами элементов И, выходы которых соединены сооюетствённо с входами сумматора, о тли чаю щ е е с я тем, что, с целью повьпиения быстродействия, в него введены два ff-разрядных регистра, причем входы синхронизации первого и второго регистгров соединены с входом синхронизации регистра множителя, входы сброса первого и второго регистров соединены с входом сброса устройства, вьхход сумматора соединен с информационным входом первого регистра, выход младшего разряда которого соединен с входом регистра множителя, В1Ыход младшего разряда которого соединен с информационным входом второго регистра, разрядные выходы которого соединены соответственно с вторыми входами влементов И. Источники информации, щжнятые во внимание при экспертизе 1.Авторское свидетельство СССР № 6232О4, кл.бОбР 7/52, 1977. . 2.Папернов. А. Логические основы цифровой вьгаиспительной техники. М., Советское радио , 1972, с. 195, р. 2 (прототип)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения чисел | 1980 |

|

SU920713A1 |

| Устройство для умножения двух @ -разрядных чисел | 1988 |

|

SU1575174A1 |

| Устройство для умножения двух @ -разрядных чисел | 1987 |

|

SU1439581A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Устройство для умножения | 1988 |

|

SU1654814A2 |

| Устройство для умножения целых чисел в р-кодах Фибоначчи | 1986 |

|

SU1345190A1 |

| Устройство для умножения в избыточной двоичной системе | 1982 |

|

SU1059568A1 |

| Устройство для умножения | 1976 |

|

SU651341A1 |

| Устройство для умножения @ - разрядных чисел | 1989 |

|

SU1735843A1 |

| Конвейерное множительное устройство | 1981 |

|

SU1043642A1 |

to

Авторы

Даты

1982-10-07—Публикация

1981-03-04—Подача