со

сд

оо

Изобретение относится к вычислительной технике, в частности к устройствам для определения модуля комплексных чисел в реальном времени, и может быть использовано в вычислительных устройствах.

Известно устройство для вычисления модуля комплексного числа, содержащее два входных регистра, два сумматора, вычитатель и коммутатор, выход которого соединен с выходом устройства, информационные входы коммутаторов подключены к выходам соответствующим сумматоров, выход знакового разряда вычитателя подключен к управляющему входу коммутатора, первые входы сумматоров и вычитателя подключен к выходу первого входного регистра, вторые входы сумматоров и вычитателя подключены к выходу второго входного регистра, входы первого и второго входных регистров подключены к соответствующим входам

устройства 1.

Однако устройство характеризуется недостаточной точностью вычисления значения модулр комплексного числа.

Наиболее близким к изобретеш1ю по технической сущности является устройство для вычисления функции X . содержащее первый входной регистр, второй входной регистр, два коммутатора, первый сумматор, второй сумматор, выход которого является выходом устройства, и схему сравнения, выход которой соединен с управляю- , щими входами коммутаторов, информационные входы которых соединены с выходами первого и второго входньк регистров соответственно, входы схемы сравнения подключены к выходам входных регистров, входы первого сумматора подключены к выходам первого коммутатора и второго сумматора, четыре входа которого подключены к выходу второго коммутатора 2.,

Недостатком известного устройства являются его сравнительно низкое быстродействие, обусловленное последовательным прохождением сигнала через все блоки устройства, а также тем, что второй сумматор должен производить суммирование четырех чисел.

Цедь изобретения - повышение быстродействия.

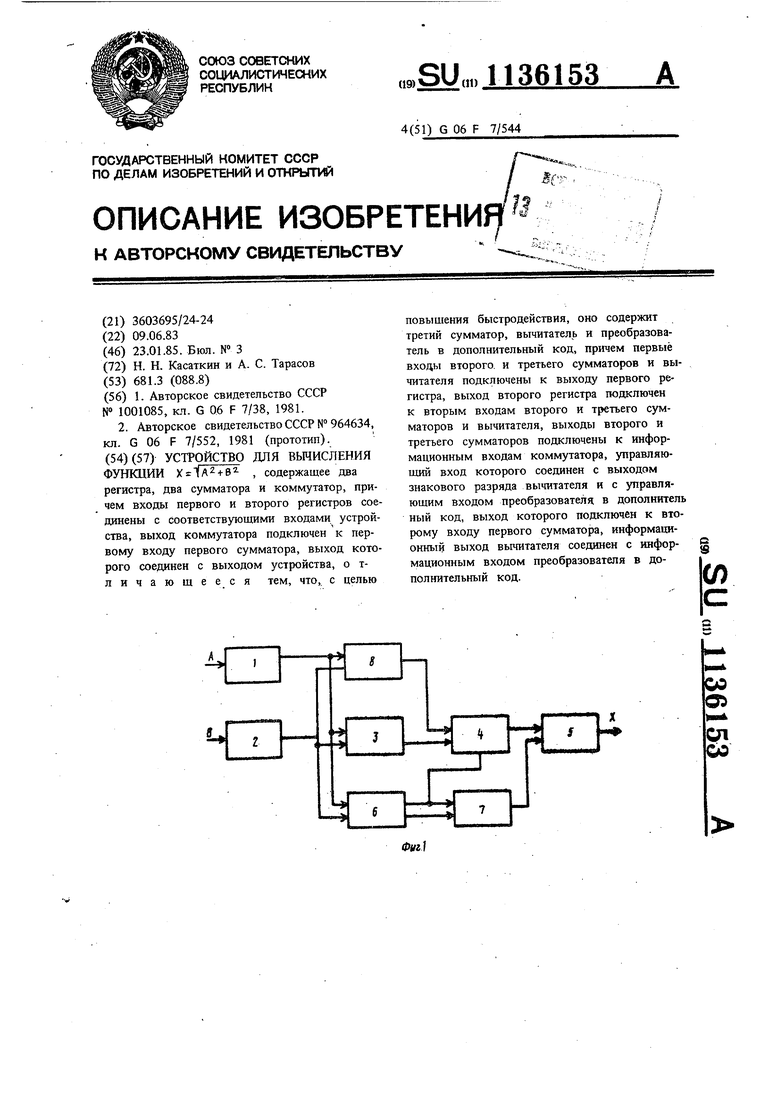

Поставленная цель достигается тем, что .. устройство для вьщисления функции содержащее два регистра, два сумматора и . коммутатор, причем входы первого и второго регистров соединены с соответствуюидами входами устройства, выход коммутатора подключен к первому входу первого сумматора, выход которого соединен с выходом устройства, содержит третий сумматор, вычитатель и преобразователь в дополнительный код, причем первые входы второго и третьего сумматоров и вычитателя подключены к выходу первого регистра, выход второго регистра подключен к вторым входам второго и третьего сумматоров и вычитателя, выхощ второго и третьего сумматоров подключены к информационным входам коммутатора, управляющий вход которого соединен с выходом знакового разряда вычитателя и с управляющим входом преобразователя в допо нительный код, выход которого подключен к второму входу первого сумматора, информационный выход вычитателя соединен с информационным входом преобразователя в дополнительный код.

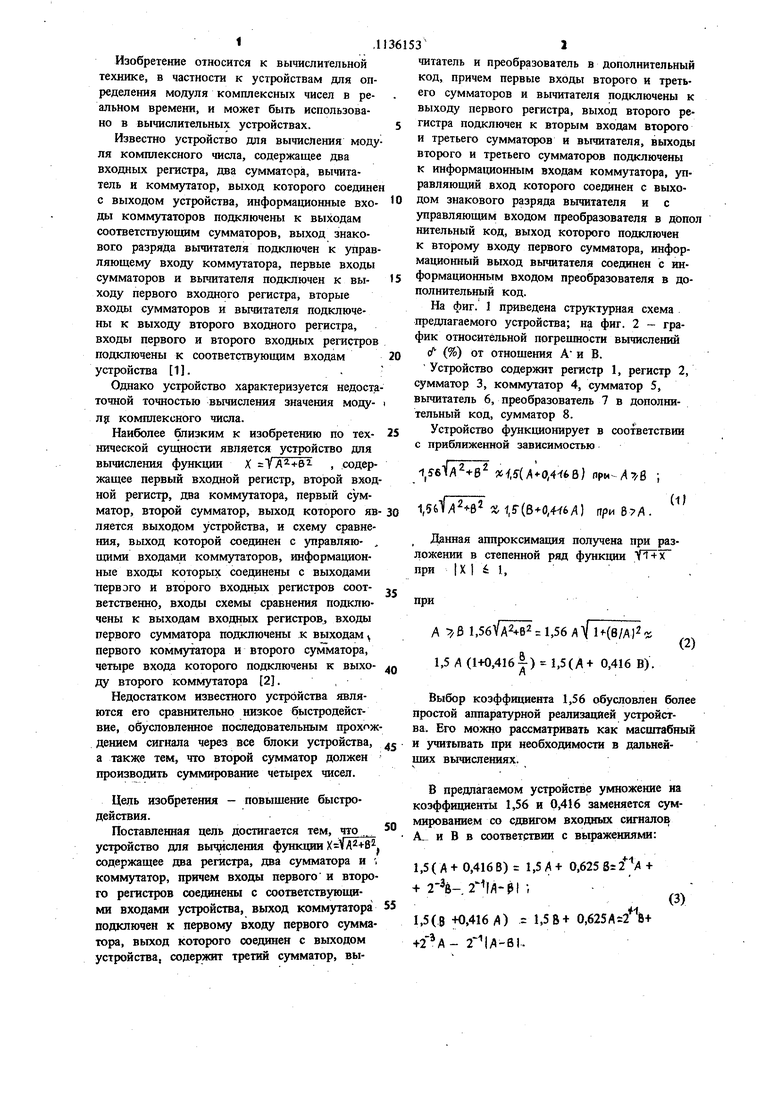

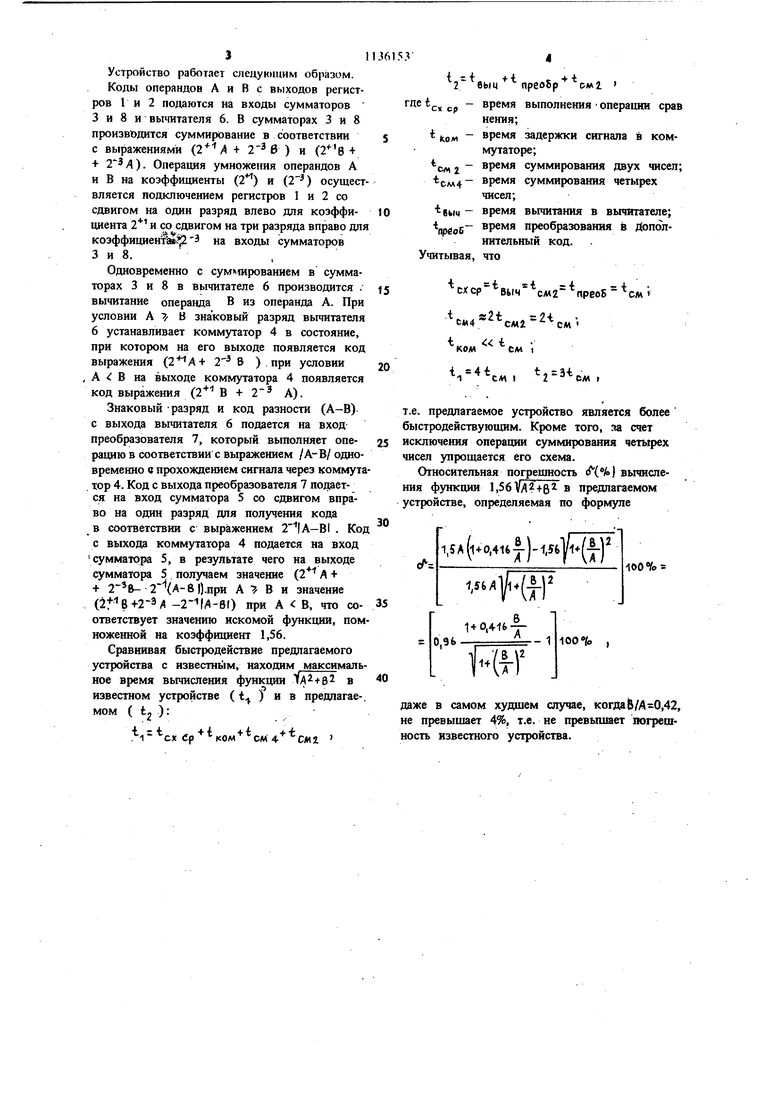

На фиг. 1 приведена структурная схема предлагаемого устройства; на фиг. 2 - график относительной погрешности вычислений

(f (%) от отношения А и В. Устройство содержит регистр 1, регистр 2, сумматор 3, коммутатор 4, сумматор 5, вычитатель 6, преобразователь 7 в дополнительный код, сумматор 8.

Устройство функционирует в соответствии с приближенной зависимостью

1,5-6lU -8 X-f,5-(,) ;

(1) 1,56lf7 1,5-(,4-Г6Л) гтри В7/Ч .

Данная аппроксимация получена при разложении в степенной ряд функции У 1 + X при |Х1 1,

при

А ,6 1, 1,5бЛ)|н(вМ)25;

(2)

1,5 А (1+0,416f) 1,5(А+ 0,416 В).

д

Выбор коэффициента 1,56 обусловлен более простой аппаратурной реализацией устройства. Его можно рассматривать как масштабный и учитывать при необходимости в дальнейших вычислениях.

В предлагаемом устройстве умножение иа козффшдаенты 1,56 и 0,416 заменяется суммированием со сдвигом входных сигналов А. и В в соответствии с вьфажениями:

-.-1;

1,5 ( А + 0,416 В) 1,5 А + 0,625 8 2 А + Ч- ;

1,5(8 +0.416 Л) 1,5 В+ 0,

2 lA-ei.. 311361 Устройство работает следующим образом. Коды операндов А и В с выходов регистров 1 и 2 подаются на входы сумматоров 3 и 8 и выштателя 6. В сумматорах 3 и 8 производится суммирование в соответствии s с выражениями ( + 2 6 ) и ( + 23А). Операция умножения операндов А и В на коэффициенты (2) и (2) осуществляется подключением регистров 1 и 2 со сдвигом на один разряд влево для коэффициента 2 и со сдвигом на три разряда вправо для коэффициент 3 на входы сумматоров 3 и 8. Одновременно с сум трованием в сумматорах 3 и 8 в вычитателе 6 производится . вычитание операнда В из операнда А. При условии А В знаковый разряд вычитателя 6 устанавливает коммутатор 4 в состояние, при котором на его выходе появляется код выражения ( 2 В ) при условии А В на выходе коммутатора 4 появляется код выражения ( В + А). Знаковый разряд и код разности (А-В) с выхода вычитателя 6 подается на вход преобразователя 7, который выполняет операцию в соответствии с выражением /А-В/одновременно в прохождением сигнапа через коммутатор 4. Код с выхода преобразователя 7 подается на вход сумматора 5 со сдвигом вправо на один разряд дпя получения кода в соответствии с выражением 2 |А-В1 . Код с выхода коммутатора 4 подается на вход сумматора 5, в результате чего на выходе сумматора 5 получаем значение ( А + + )).при А В и значение (2 В+2-3/ -2-М-в() при А В, что со- 35 ответствует значению искомой функции, помноженной на коэффициент 1,56. Сравнивая быстродействие предлагаемого устройства с известным, находим максимальное время вычисления функции в известном устройстве (t. ) ив предпагае-. мом ( t ): . ;p KOM cM4 c«z 5.V гд т.е бы ис чи ни ус да не но 4 2 выц прео5р с«Аг j. р - время выполнения операции срав нения; Ном время задержки сигнала в коммутаторе; время суммирования двух чисел; см4 время суммирования четырех чисел; ewM - время вычитания в вычитателе; поеоЧ преобразования в Дополнительный код. итывая, что «ср Biin см2 преоБ см Ctt4 2tcMZ 2ic -, ком см i . Ч«, , предлагаемое устройство является более родействующим. Кроме того, аа счет ючения операции суммирования четьфех упрощается его схема. носительная погрешность вычислефункции 1,5бУЛ2+6 в предлагаемом йстве, определяемая по формуле ,5A(,41t|-)-f, 100% VMf(|J 140.41Ь-дтегв самом худшем случае, когда 6/А 0,42, ревышает 4%, т.е. не превышает погрешизвестного устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функции @ | 1987 |

|

SU1481752A1 |

| Вычислительное устройство | 1984 |

|

SU1203513A1 |

| Устройство для одновременного вычисления двух многочленов | 1980 |

|

SU926650A1 |

| УСТРОЙСТВО ДЕЛЕНИЯ И ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ | 2012 |

|

RU2510072C1 |

| Устройство для вычисления функций Z @ = @ @ @ / @ и Z @ = @ @ @ / @ | 1988 |

|

SU1539771A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Устройство для вычисления модуля и аргумента вектора | 1986 |

|

SU1403063A1 |

| Устройство для вычисления функции | 1986 |

|

SU1348829A1 |

| Цифровой рекурсивный фильтр | 1985 |

|

SU1328925A1 |

| Устройство для вычисления функции арктангенса отношения | 1988 |

|

SU1615709A1 |

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИИ + в , содержащее два регистра, два сумматора и коммутатор, причем входы первого и второго регистров соединены с соответствующими входами устройства, выход коммутатора подключен к первому входу первого сумматора, выход которого соединен с выходом устройства, о тличающееся тем, что, с целью повышения быстродействия, оно содержит третий сумматор, вычитатель и преобразователь в дополнительный код, причем первые входы второго, и третьего сумматоров и вычитателя подключены к выходу первого регистра, выход второго регистра подключен к вторым входам второго и третьего сумматоров и вычитателя, выходы второго и третьего сумматоров подключены к информационным входам коммутатора, управляющий вход которого соединен с выходом знакового разряда вычитателя и с управляющим входом преобразователя в дополнитель ный код, выход которого подключен к второму входу первого сумматора, информационный выход вычитателя соединен с информационным входом преобразователя в до(Л полнительный код.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для вычисления модуля комплексного числа | 1981 |

|

SU1001085A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для вычисления функции х= @ + @ | 1981 |

|

SU964634A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-01-23—Публикация

1983-06-09—Подача