1

(21 ) 4417074/24-24

(22) 18.04.88 (46) 23.02.90. Бюл. № 7

(71)Киевский институт инженеров гражданской авиации им. 60-летия СССР

(72)И.А. Жуков, Л.Я. Нагорный (SU) , Ддай Сингх (IN) и Жозеф Бахендузн (ВТ.)

(53) 681.323(088.8)

(56) Авторское свидетельство СССР

fr 732863, кл. G 06 F 7/552, 1978.

Авторское свидетельство СССР № 1024914, кл. G 06 F 7/552, 1983.

(54) УСТРОЙСТВО ДЛЯ ИЗВЛЕЧЕНИЯ КВАДРАТНОГО кдрня и ЕГО ОБРАТНОЙ ВЕЛИЧИНЫ

(57) Изобретение относится к вычислительной технике и может быть использовано для аппаратного вычисления квадратного корня и его обратной величины в избыточной системе счисления в форме с фиксированной запятой. Целью изобретения является повышение быстродействия устройства. Устройство позволяет потактно обрабатывать данные по мере их поступления и осуществлять одновременно коррекцию полученных результатов после каждой итерации. 1 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Конвейерное устройство для вычисления функций синуса и косинуса | 1981 |

|

SU1003080A1 |

| Конвейерное вычислительное устройство | 1987 |

|

SU1432512A1 |

| Конвейерное устройство для вычисления логарифмической и экспоненциальной функций | 1982 |

|

SU1027722A1 |

| УСТРОЙСТВО ДЕЛЕНИЯ И ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ | 2012 |

|

RU2510072C1 |

| Вычислительное устройство | 1981 |

|

SU1136147A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1130861A1 |

| Устройство для вычисления квадратного корня | 2017 |

|

RU2638010C1 |

| Генератор функций Попенко-Турко | 1990 |

|

SU1753464A1 |

| Устройство для вычисления функции @ = @ | 1982 |

|

SU1034033A1 |

| Процессор для цифровой обработки сигналов | 1985 |

|

SU1257662A1 |

Изобретение относится к вычислительной технике и может быть использовано для аппаратного вычисления квадратного корня и его обратной величины в избыточной системе счисления в форме с фиксированной запятой. Целью изобретения является повышение быстродействия устройства. Устройство позволяет потактно обрабатывать данные по мере их поступления и осуществлять одновременно коррекцию полученных результатов после каждой итерации. 1 ил.

Изобретение относится к вычислительной технике и может быть использовано для аппаратного вычисления квадратного корня и его обратной величины.

Цель изобретения - повышение быстродействия устройства.

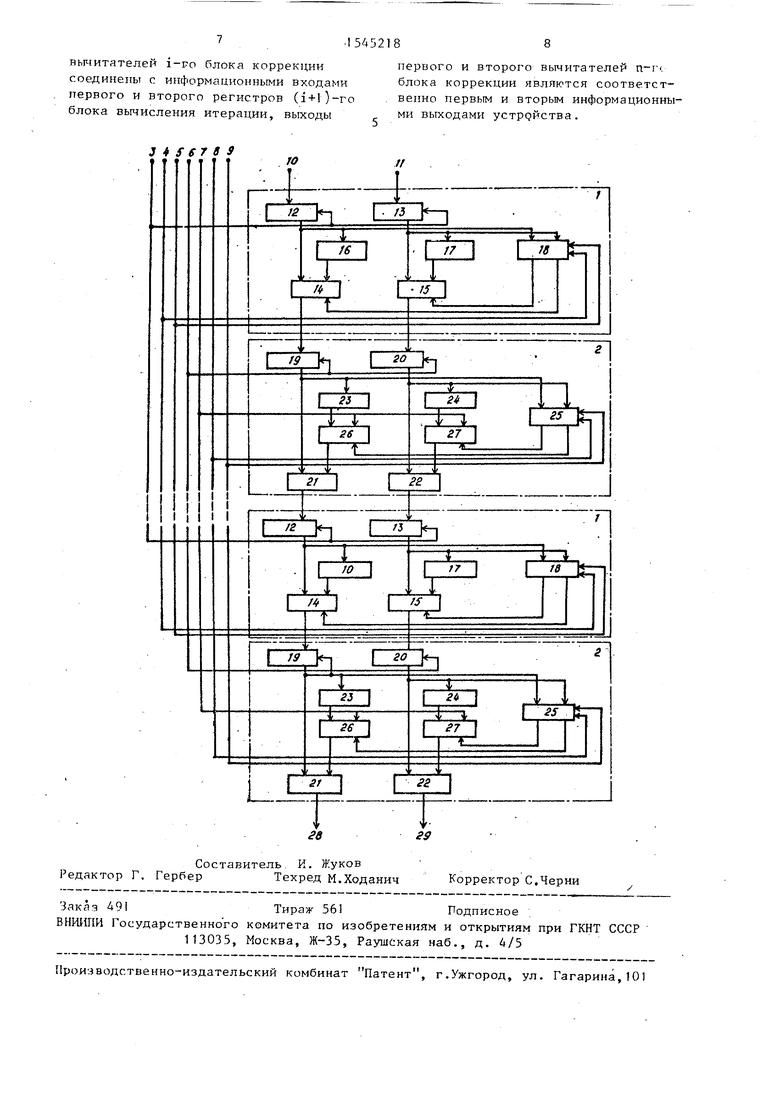

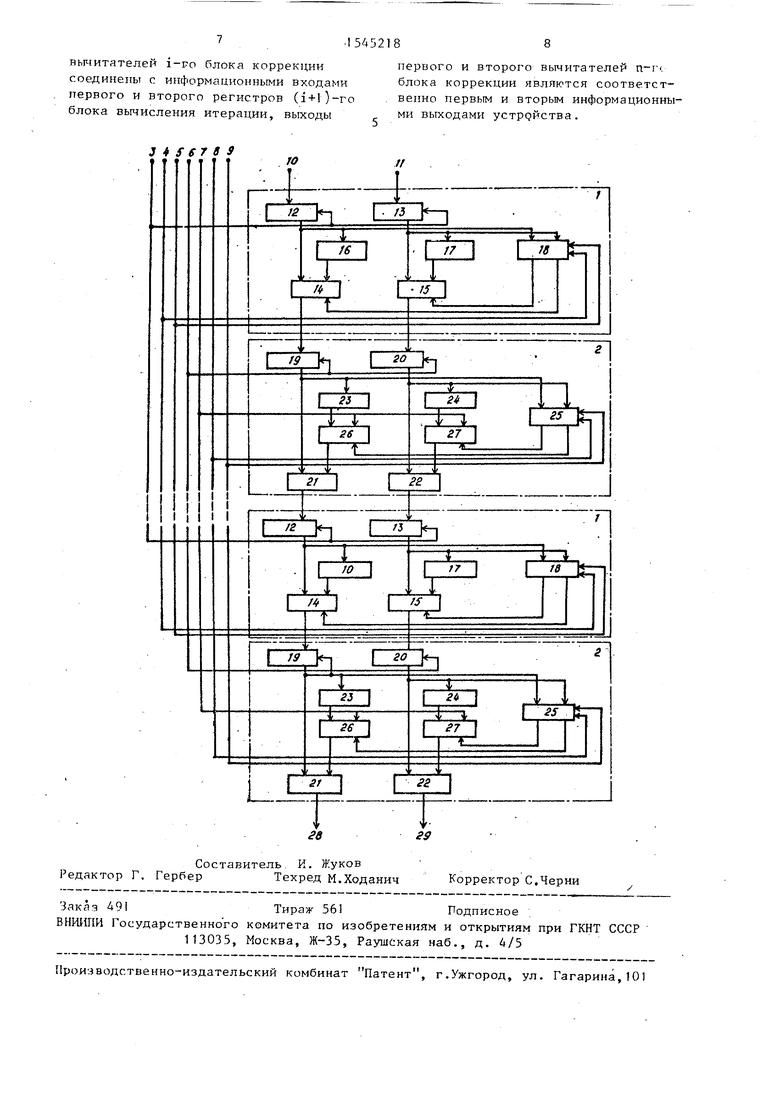

На чертеже представлена структурная схема устройства.

Устройство состоит из блоков 1 вычисления итерации, блоков 2 коррекции, синхровходов 3-8 устройства, входа 9 логического нуля, информационных входов 10 и 11 устройства-, блоки I вычисления итерации содержат регистры 12 и 13, сумматоры 14 и 15, регистры 16 и 17 сдвига, блок 18 анализа разности; блоки 2 коррекции содержат регистры 19 и 20, вычитатели

21 и 22, регистры 23 и 24 сдвига, блок 25 анализа разности, коммутаторы 26 и 27, информационные выходы 28 и 29 устройства.

Вычисление квадратного корня и его обратной величины производится по алгоритму, содержащему разностные рекуррентные соотношения

-( К)

х . х, + Ч,х,2

,-d + i) у у , + q , у, 2 ,

где х „

У, + Ч, У, 2 х, У0 I .

О)

СП

Јь

сл to

OP

х у - значение после первого

шага

1-й итерации

.,-{

I С

при х ( у, ,

О при у -1 х,

3154521

,2,...,n- порядковый номер

итерации;

n - число разрядов аргумента;

q , q . - прямой и обратный код сигнала сравнения значений

В результате получают

и у,

х Уп - .

Vx

Известно, что при вычислениях с помощью алгоритма (1) происходит уд- линение значений на величину К., определяемую соотношением

К; - П (1 + 2- У

Uo

Таким образом, полученные значе- ния х, у 1 в К. раз больше истинного значения длины вектора после поворота, поэтому необходима коррекция по- лучеиных результатов, т.е. необходим

i l i найти х .«- , у i Ь . i

-. При правильно К . i

организованной операции деления должно выполняться равенство 1

где число Z - частное от деления - может быть представлено в виде произведения, т.е. Z П (1- С-, ).

, 1-0

I 1 при у х1 .

Тогда алгоритм (2) для коррекции полученных результатов при реализации алгоритма (I)

Г

- I

х , G;X- 2 ;

V, - О, у 1-2-

(2)

у . - значение после первого шага i-й инте

0

5

0

5

0

5

0

45

50

5

84

рации в результате коррекции.

Устройство р Дотает следующим образом .

Рассматривают работу блока 1 вычисления итерации. В первом такте в регистр 12 заносится по входу 10 значение х0 х, в регистр 13 заносится по входу 11 значение у0 1, с приходом импульса на синхровход 1 в регистры 12 и 13 записываются значения Х)} х, у„ 1. Регистры 16 и 17 сдвига соединяются с соответствующими вторыми входами сумматоров 14 и 15 таким образом, что на входы поступают значения Хс и ус со сдвигом на один разряд вправо, кроме того, на первый вход сумматоров 14 и 15 поступают значения х0 и у0.

Полученные на выходах сумматоров 14 и 15 величины х и у 1 поступают в блок 2 коррекции, где осуществляется коррекция результата. Работа сумматоров 14 и 15 управляется по величинам q- и с(, которые за счет сравнения значений х . у. определяются в блоке 18, с приходом импульса на синхровход 2 в блок 18 анализа разности записываются значения х и у. , а с приходом импульса на синхровход 3 значения цифр о и о. передаются для управления сумматоров 14 и 15. Во втором такте производится запись результатов вычислений из первого блока 2 коррекции во второй блок 1, т.е. полученные значения У j+ f и у. после первого шага i-й итерации в результате коррекции из первого блока 2 записываются в регистры 12 и 13 второго блока 1 соответственно. Одновременно в регистры 12 и 13 первого блока 1 поступают коды второгооперанда. В первом блоке 1 производится выполнение первой итерации над вторым операндом, аналогично, как в первом такте, выполняется первая итерация над первым операндом, а во втором блоке 1 выполняется вторая итерация над первым операндом. В третьем такте производится запись результатов вычислений из первого и второго блоков 2 коррекции во второй и третий блок 1 соответственно, и одновременно в регистры 12 и 13 первого блока 1 вычисления итерации поступают коды третьего операнда. В первом блоке 1 выполняется первая итерация над треть5154

им операндом, РО втором - и горл и итерация над вторым операндом, в третьем - третья итерация над первым операндом. В дальнейшем результаты из предыдущих блоков поступают в

последующие блоки, я в первый блок поступают два операнда и т.д.

Рассматривают работу блока 2 кор- рекции.

Значения х и у1 на выходах сумi

маторов поступают соответственно в

регистры 19 и 20. С приходом импульса на синхровход 4 в регистры 19 и 20 записываются значения х и у. Ре- гистры 23 и 24 сдвига осуществляют сдвиг значений х } и у на один разряд вправо, т.е. их умножение на , а результаты (сдвинутые значения

х, ) поступают на первые входы коммутаторов 26 и 27 соответственно. На вторые входы коммутаторов 26 и 27 поступают сигналы логического нуля. С приходом импульса на синхровход 5 в блоке 25 анализа разности записываются значения xf и у1, ас приходом импульса на синхровход 6 значения цифр G( 0,1 передаются для управления коммутаторов 26 и 27. На первые входы вьгчи- тателей 21 и 22 поступают соответственно значения xl, у, а на вторые входы вычитателей 21 и 22 поступают соответственно значения С- (х 2 , . В каждом блоке 2 коррекции вычисляется алгоритм (2), В каждом i-м (i 1,2,...,п) итерационном блоке 1 и блоке 2 коррекции сдвиг н один разряд вправо осуществляется путем жесткого соединения выходов разрядов регистров с входами разрядов регистра сдвига со сдвигом на данное число разрядов.

Формула изобретения

Устройство для извлечения квадратного корня и его обратной величины, состоящее из п блоков вычисления (где п - число разрядов аргумента) итерации, каждый из которых содержит первый и второй регистры, первый и второй сумматоры, первый и второй регистры сдвига, блок анализа разности, причем входы разрешения записи пер- вого и второго регистров соединены с первым синхровходом устройства, в информационные входы подключены соответственно к первому и второму ин2

()

г

0

5 0 о

5

0 5

8А

формлционньгм в ход л м ч тройства, nw-vo- ды первого i-i второго регистров сое- динены с первыми входами соответственно первого и второго сумматоров, с входами первого и второго регистров сдвига и с первым и вторым информационными выходами блока анализа разности соответственно, первый и второй управляющие входы которого подключены к второму и третьему синхро- входам устройства соответственно, а первый и второй выходы соединены с вторым и третьим гинхровходами устройства соответственно, отличающееся тем, что, с целью повышения быстродействия, в неге дополнительно введены п блоков коррекции, каждый из которых содержит первый и г второй регистры, первый и второй регистры сдвига, первый и второй коммутаторы, первый и второй вычнтатели, блок анализа разности, причем выходы первого и второго сумматоров i-ro (i I,...,In) блока итерации соединены с информационными входами соответственно первого и второго регистров i-ro блока коррекции, входы разрешения записи которых соединены с четвертым синхровходом устройства, выход первого регистра 1-го блока коррекции соединен с первым входом первого вычитателя, с информационным входом первого регистра сдвига и первым информационным входом блока анализа разности :-го блока коррекции, выход второго регистра 1-го блока коррекции подключен к первому входу второго вычигателя, информационному входу второго регистра сдвига и второму информационному входу блока анализа разности 1-го блока коррекции, выходы первого и второго регистров сдвига 1-го блока коррекции соединены с первыми входами соответственно первого и второго коммутаторов того же блока коррекции, вторые входы которых подключены к пятому синхро- входу устройства, а выходы - к вторым входам соответственно первого и второго вычитателей i-ro блока коррекции, первый и второй управляющие входы блока анализа разности 1-го блока коррекции соединены соответственно с шестым и седьмым синхровхо- дами устройства, а первый и второй выходы - с третьими входами первого и второго коммутаторов того же блока коррекции, выходы первого и второго

вычитятелей i-го блока коррекции соединены с информационными входами первого и второго регистров (i+l)-ro блока вычисления итерации, выходы

J 4 S 6 7 в 9

первого и второго вычитателей n-i блока коррекции является соответственно первым и вторым информационными выходами устройства.

Авторы

Даты

1990-02-23—Публикация

1988-04-18—Подача