(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1984 |

|

SU1176383A1 |

| Ассоциативный параллельный процессор | 1980 |

|

SU955078A1 |

| Устройство для поиска информации в памяти | 1986 |

|

SU1392579A1 |

| Запоминающее устройство | 1981 |

|

SU1010653A1 |

| Запоминающее устройство | 1983 |

|

SU1117709A1 |

| Резервированное запоминающее устройство | 1985 |

|

SU1278984A1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| Запоминающее устройство | 1978 |

|

SU743031A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Запоминающее устройство | 1983 |

|

SU1115105A1 |

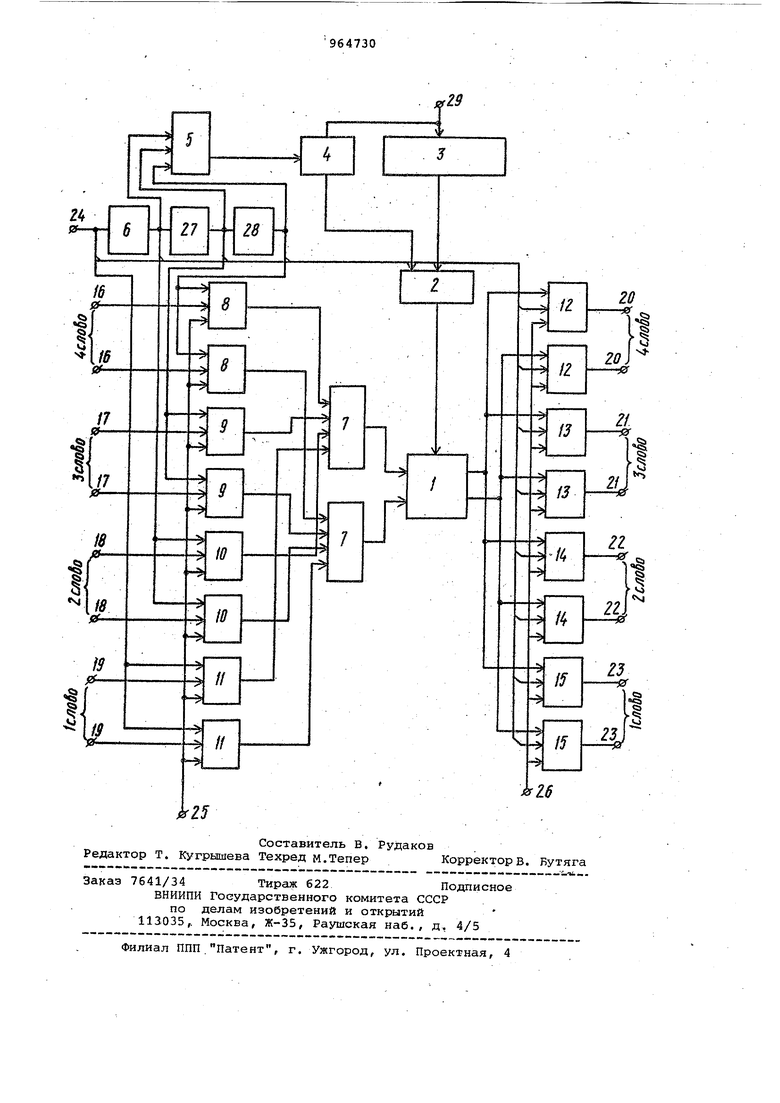

Изобретение относится к автоматике и вычислительной технике, а именно к запоминающим устройствам. Известно устройство, которое содержит накопитель датчики кода адре са, дешифраторы адреса, группы элементов И и ИЛИ, обеспечивающих подключение датчика кода адреса к дешиф ратору адреса, входных и выходных информационных шин - к соответствующим шинам устройства ClJ. Недостатком этого устройства явля ется то/ что для случая записи много разрядного кода требуется введение дополнительного оборудования в разря нук) часть ЗУ или снижение частоты обращения к ЗУ, которое.связано с дополнительными затратами времени на формирование кода адреса для записи (считывания) избыточных разрядов информационного кода. Наиболее близким техническим .решением к изобретению является запоминающее устройство, содержащее накопитель, одни из входов которого соединены с выходами элементов ИЛИ, другие - с выходами дешифратора адре са, входы которого подключены к выхо дам первых и вторых элементов И, первые входы которых соединены с выходами датчика кода адреса, выходы накопителя соединены с первыми входами третьих и четвертых эле1 1ентов И, вторые входы третьих элементов И соединены с шиной опроса и с вторыми входами первых элементов И, третьи входы третьих элементов И и вторые входы четвертых элементов И соединены с шиной разрешения считывания, выходы третьих и четвертых элементов И соединены с выходами устройства. Устройство также содержит амну разрешения записи и информационные шины, элемент задержки, пятые и шестые элементы И, выходы которых подключены к входам элементов ИЛИ, первые входы пятых и шестых элементов И.соединены с информационными шинами, вторые входы - с шиной разрешения записи, третьи входы пятых элементов И соединены с шиной опроса и входом элемента задержки, выход которого соединён с вторыми входами вторых элементов И, третьими входами четвертых и шестых элементов И. По сигналу Смена адреса, поступающему на вход датчика кода адреса, на его выходах вырабатывается прямой и инверсный коды адреса. Опрос накопителя осуществляется при поступлении сигнала Опрос на шину опроса. При этом накопитель сначала опра шивается по адресу, соответствующем прямому коду адреса, а затем тот же импульс опроса, задержанный элементом задержки, обеспечивает опрос на копителя по инверсному коду адреса. В режиме Запись (на шину разреше ния записи подается сигнал разрешения) одна половина информационного кода записывается по прямому коду адреса в накопитель, а вторая полови на информационного кода записывается в накопитель по инверсному коду адре са. В режиме Считывание на ишну разрешения считывания подается разре шение, и на выход устройства считывается одна половина информационного слова по прямому коду адреса, а другая - по инверсному 2. Недостатком такого устройства является ограниченная область применения устройства. Так, запись слова, имеющего разрядность в дв& раза боль ше, чем разрядность накопителя, в таком устройстве невозможна. Цель изобретения - расширение области применения устройства за счет увеличения разрядности входной информации. Поставленная цель достигается тем что в запоминающее устройство, содер жащее накопитель, дешифратор.адреса, формирователь кода адреса, элементы ИЛИ, группы входных и выходных элементов И и- первый элемент залеожки причем адресные входы накопителя под ключенй к выходам дещифратора адреса один из входов КОТОРОГО соединены с выходами Формирователя кода адоеса вход. КОТОРОГО является входом смены адреса, информационные входал накопителя подключены, к выходам элементов ИЛИ, входы КОТОРЫХ соединены с выходами соответствующих входных элементов И, первые входы которых объединены и являются входом разрешения записи, вторые входы входных элементов И являются информационными входами устройства, первые входы выходных элементов И объединены и являются входом разрешения считывания вторые входы подключены к соответствующим выходам накопителя, вход первог элемента згщержки и третьи входы входных и выходных элементов И первых ГРУПП объединены и являются входом опроса, третьи входы входных и выходных элементов И вторых ГРУПП соединены с выходом первого элемента задержки, введены счетчик адреса, дополнительный элемент ИЛИ и последовательно соединенные ВТОРОЙ и третий элементы задержки, причем входы входных и выходных элементов И третьих ГРУПП подключены к выходу второго элемента задержки вход которого соединен с выходом первого элемента задержки, третьи входы входных и выходных элементов И четвертых групп подключены к выходу третьего элемента задержки, выходы элементов, задержки соединены с входами дополнительного элемента ИЛИ, выход которого подключен к одному из входов счетчика адреса, другой вход которого соединен с входом формирователя кода адресов, а выходы - с другими входами дешифратора адреса. На чертеже изображена функциональ ная схема запоминающего устройства при длине входного слова, превышающей разрядность накопителя в четыре раза. Устройство содержит накопитель 1, дешифратор 2 адреса, формирователь 3 кода адреса, счетчик 4 адреса, дополнительный элемент ИЛИ 5, первый элемент б задержки, элементы ИЛИ 7, группы входных элементов И 8-11 и группы выходных элементовИ 12-15, имеющих входы 16-19 и выходы 20-23. соответственно. Устройство имеет вход 24 опроса, входы 25 и 26 разрешения записи и считывания соответственно. Устройство также содержит второй 27 и третий 28 элементы задержки и имеет вход 29 смены адреса. Устройство- работает в режимах Запись и Считывание. , В режиме Запись на вход 25 поступает сигнал разрешения. На входы 16-19 поступает входная информация, равная по количеству разрядов четырем словам накопителя 1. (На, группу входов 19 поступает первое слово, на группу входов 18 - второе слово, на группу входов 17 - третье слово, на группу входов 16 - четвертое слово) . На первом этапе по сигналу опроса с входа 24 через группу элементов И 11 и элементов ИЛИ 7 первое слово с группы входов 19 записывается в накопитель l по адресу, выбранному деишфратором 2(при этом содержимое счетчика 4 равно нулю, а с выходов формирователя 3 кода адреса снимается нужный адрес). На втором этапе цикла записи задержанный на элементе 6 задержки сигнал Опроса стробирует прохождение второго слова входной информации через элементы И 10 и ИЛИ 7 с группы входов 16 на входы накопителя 1. С выхода элемента 6 задержки через элемент ИЛИ 5 на счетный вход счетчика 4 поЬтупает задержанный сигнал опроса с входа 24, который переводит счетчик 4 в состояние /Сч/ + 1 (содер- . имое сч.етчика плюс единица) . Выходы счетчика 4 являются младшими разядами кода адреса, по которому производится обращение к памяти (в обем случае йто могут быть любые разряды адреса). Старшими разрядами адреса являются вьаходы формирователя 3 кода адреса. Таким образом, на Втором этапе производится запись второго слова входной информации по адресу содержимое формирователя 3 кода адреса +1.

На третьем этапе задержанный сигнал опроса с выхода элемента 27 задержки переводит счетчик 4 в следующее состояние .(//Сч А/ + 1/ + 1) и стробирует прохождение третьего ел ва с входов 17 чероз элементы И 9, ИЛИ 7 на входы накопителя 1. Третье слово входной информации записывается в ячейку по адресу (/содержимое кода формирователя .3 кода адреса/ + + 2) .

Аналогичньлм образом на четвертом этапе обращения к накопителю четвертое слово входной информации записывается в накопитель 1 по адресу (/содержимое Формирователя 3 кода адреса + 3). При этом стробирующий сигнал опроса берется с выхода элемента 28 задержки.

В режиме Считывание на вход 26 поступает .сигнал разрешения. Исполнительный адрес на входах дешифратора 2 формируется так же, как и в реж ме Запись. Сигналы опроса с-входа .24 на первом этапе цикла считывания стробируют прохождение:первого считываемого слова на выход устройства (группа выходов 23) через группу элементов И 15. На втором этапе с выхода элемента 6 задержки сигнал опроса стробирует элементы И 14 и разрешает поступление второго слова выходной информации и т.д.

Предлагаемое устройство позволяет значительно расширить область применения устройства в сравнении с известным, в котором имеется принципиальная возможность записи и считывания информации по разрядности, не превыгуающей разрядность накопителя более, чем в два раза. Предлагаемое Устройство в сравнении с известным не имеет такого ограничения. Разряд.ность входной и.выходной информации IB принципе в нем не ограничена. Устройство позволяет аппаратно производить упаковку входной информации в слове, длина разрядов которых равн длине слова ячейки накопителя. Это позволяет повысить быстродействие в сравнении с методом программной упаковки информациии. Кроме того, устройство позволяет приме,нить стандартные блоки накопителей в цировых устройствах,, обрабатываквдих слова повышенной разрядности.

С другой стороны, предлагаемое устройство можно применять в обычных режимах записи и считывания. В этом случае в счетчик 4, как в формирователе 3v кода.адреса, заносится кОд

адреса (соответствующие связи не указаны) , по которому производится обращение. При этом, если элементы 6, 27 и 28 задержки заблокированы, го первое слово информации записывается Или считывается по любому адресу накопителя 1. Это позволяет эффективно использовать емкость накопителя. Формула изобретения

0

Запоминагацее устройство, содержащее накопитель, дешифратор адреса, формирователь кода адреса, элементы ИЛИ, группы входных и выходных элементов И и первый элемент задержки,

5 причем адресные входы накопителя подключены к выходам дешифратора адреса, одни из входов которого соединены с выходами формирователя кода адреса, вход которого является входом смены адреса, информационные входы накопи0теля подключены к выходам элементов ИЛИ, входы которых соединены с выходами соответствующих входных элементов И, первые входы которых объединены и являются входом разрешения записи,

5 вторые входы входных элементов И являются информационными входами устройства, первые входы выходных элементов- И объединены и являются входами разрешения считывания, вторые вхо0ды подключены к соответствукндим выходам накопителя, вход первого элемента задержки и третьи входы входных и выходных элементов И первых групп объединены и являются входом опроса,

5 третьи входы входных и выходных элементов И вторых групп соединены с выходом первого элемента задержки, о тл и ч а ю щ е е c я тем, что, с целью расширения области примене1ния

0 устройства за счет увеличения разрядности входной информации, оно содержит счетчик адреса, дополнительный элемент ИЛИ и последовательно соединенные второй и третий элементыэа5держки, причем третьи входы входных и выходных элементов И третьих групп подключены к выходу второго элемента задержки, вход которого соединен с выходом первого элемента задержки, третьи входы входных и выходных элеOментов И четвертых групп подключены к выходу третьего элемента задержки, выходы элементов задержки соединены с входами дополнительного элемента ИЛИ, выход которого подключен к одно5му из входов счетчика адреса, другой вход которого соединен с входом формирователя кода адреса, а выходы с другими входами дешифратора адресаИсточники информации,

0 принятые во внимание при экспертизе

5 (прототип).

Авторы

Даты

1982-10-07—Публикация

1981-01-09—Подача