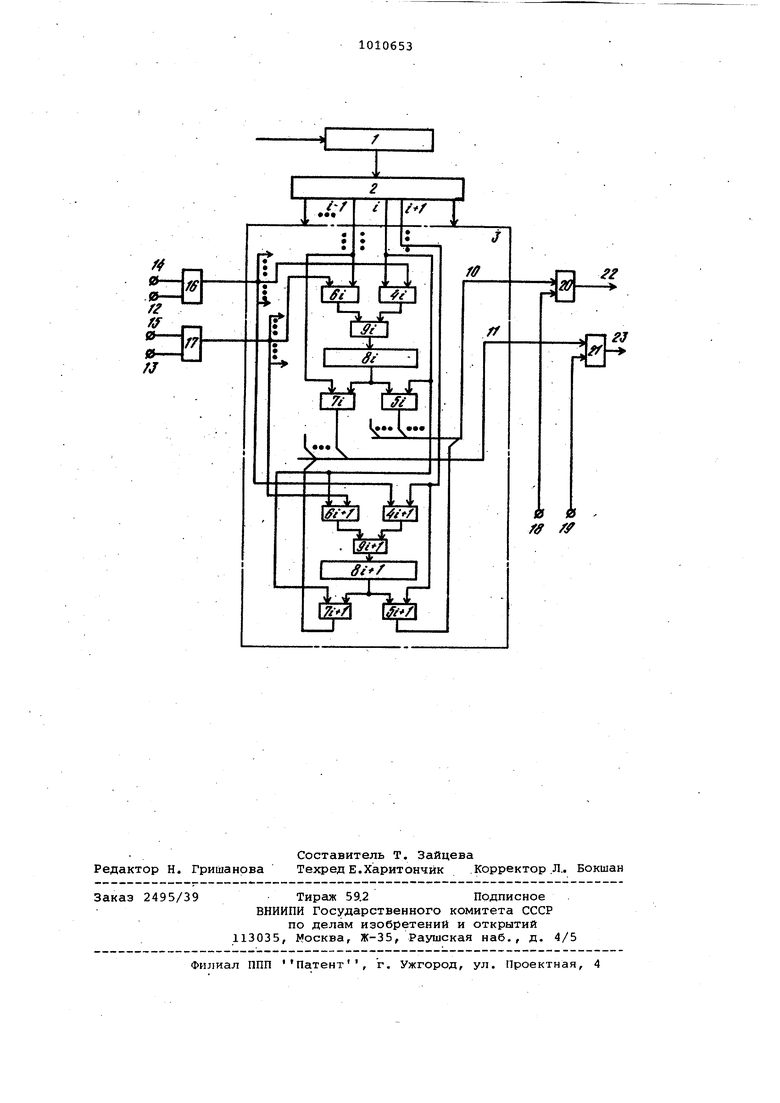

Изобретение относится к вычислительной технике и может быть исполь зовано в мультипроцессорных система в состав которых входят процессоры с различной физической разрядностью Известно запоминающее устройство содержащее накопитель, дешифратор адреса, датчик кода адреса, коммута тор, схемы выделения каналов, элеме ты ИЛИ, делители частоты, схемы фор мирования контрольных символов fl 1. Недостатком этого устройства явл ется ограниченность его возможностей для случая записи информационно го кода с числом разрядов, превышающим число разрядов накопителя. Наиболее близким техническим решением к предлагаемому является запо минающее устройство, содержащее нако питель, один из входов которого соединен с выходом блока элементов ИЛИ, другие входы накопителя соединены с выходами дешифратора адреса, входы которого подключены к выходам первого и второго блоков элементов И, первые входы которых соединены с выходами датчика кода адреса, выходы накопителя соединены с первыми входа tm третьего и четвертого блоков элементов и, вторые входы третьего блока элементов и соединены с шиной опроса и со вторыми входами первого блока элементов И, третий вход треть го блока элементов И и вторые входы четвертого блока элементов И соединены с шиной разрешения считывания, выходы третьего и четвертого блоков элементов И соединены с выходами уст ройства, шину разрешения записи, информационные шины, элемент задержки, пятый и шестой блоки элементов И . (пятые и шестые элементы И),выходы которых подключены к входам блока элементов ИЛИ, первые входы пятого и шэстого блоков элементов И соединены с информационными шинами, вторые входы - с шиной разрешения записи, третьи входы пятого блока элементов И соединены с шиной опроса и входом элемента задержки, выход которого соединен с вторым входом второго блока элементов И, третьими входами четвертого и шестого блоков элементов, И 23. Недостатками данного устройства являются низкое J5ыeтpoдeйcтвиe при работе с числами двойной разрядности, так как для записи или считывания необходимо два обращения к накопителю по прямому и инверсному адресу, и неэффективное использовавне накопителя при записи числа одинарной разрядности, так как по инверсным адресам будут записываться нули. Цель изобретения - повышение быст родействия и увеличение информационной емкости устрсзйства. Поставленная цель достигается тем, что в запоминающее устройство, содержащее формирователь адресных сигналов, выходы которого соединены со входами дешифратора адреса, элементы И, регистры и группы элементов И, причем первые входы первого и второго элементов И являются информационными входами устройства, второй вход первого элемента И является первым входом разрешения записи устройства, а выходы третьего и четвертого элементов И - выходами устройства, первые входы элементов И первой и второй групп подключены к выходам дешифратора адреса, вторые входы элементов И.первой группы соединены с выходом первого элемента И, вторые входы и выходы элементов И второй группы подключены соответственно чк выходам регистров и к одним из входов третьего элемента И, другой вход которого является первым входом разрешения считывания устройства, введены элементы ИЛИ, третья и четвертая группы элементов И, причем первый и второй входы и выходы элементов ИЛИ подключены соответственно к выходам элементов И третьей группы, к выходам элементов И первой группы и к входам регистров, первце входы и выходы элементов И четвертой группы соединены соответственно с выходами регистров и с одним из входов четвертого элемента И, первые входы элементов И третьей группы подключены к выхо- ду второго элемента И, вторые входы элементов И третьей и четвертой групп соединены с выходами дешифратора адреса, кроме последнего, второй вход второго элемента И и ДРУгой вход четвертого элемента И являются соответственно вторым входом разрешения записи и вторым входом разрешения считывания устройства. На чертеже изображена функциональная схема предлагаемого устройства. Устройство содержит рмирователь 1 адресных сигналов, дешифратор 2 адреса, накопитель 3, состоящий из элементов И 4 первой группы, элементов И 5 второй группы, элементов И б третьей группы, элементов И 7 четвертой группы, регистров 8 и элементов ИЛИ 9, выходы 10 и II накопителя, первый 12 и второй 13 входы разрешения записи устройства, информационные входы 14 и 15 устройства, первый 16 и второй 17 элементы И, первый 18 и второй 19 входы разрешения считывания устройства, третий 20 и четвертый 21 элементы И, выходы 22 и 23 устройства. Предлагаемое запоминающее устройство работает следующим образом.

Код адреса i-й ячейки с выхода формирователя 1 поступает на входы дешифратора 2, при этом появляется сигна.л на 1-м выходе дешифратора 2 и поступает на соответствующий вход накопителя 3, а именно: на первый и второй входы элементов И соответственно первой 4 и второй 5 групп i-й ячейки и на первые и в-юуые входы элементов И соответственно третьей 6 и четвертой 7 групп (i + 1)-й ячейки.

В режиме Запись двойного слова на первый 12 и второй 13 входы разрешения записи одновременно подаются сигналы, по которым старшая часть информации с входа 14 через элементы И-4 и элементы ИЛИ 9 записывается известн1 1 способом в регис в 1-й ячейки накопителя, а ..младшая часть информации с входа 15 проходи череэ элемент И 17, элемент И б и элемент ИЛИ 9 и записывается в регистр 8 (i +1)-й ячейки. В режиме Запись слова сигнал разрешения записи подается только по входу 12 и, следовательно, информация,поступанхцая по входу 14, записывается только в регистр 8 1-й ячейки накоптеля 3. В режиме Считывание двойного слова на входы 18 и 19 одновременно подаются сигналы, по которым одна часть информсщии, поступгиощая с регистра 8 i-й ячейки накопителя 3 через выход 10 на первый вход элемента И 20, выдается на выход 22, а другая часть информации, поступающая с регистра 8 (i + 1)-й ячейки через выход 11 накопителя на первый вход элемента И 21, выдается на выход 23. В режиме Считывание слова сигнал разрешения считывания подается только по входу 18 и информация на выход 22 выдается толко из регистра 8 i-й ячейки накопителя 3.

Таким образом, предлги аемое запоминающее устройство обеспечивает за один цикл обращения к памяти запись или считывание информации с числом разрядов, ргшным или превышающим -в 2 раза разгядностВ накопителя. При этом обеспечивается наиболее полное .использование емкости накопителя и отсутствуют .ограничения на размещение информации в ЗУ.

Технико-экономические првимущест ва предлагаемого устройства заключаются в его более высоком быстродействии и более высокой информационно емкости по сравнению с прототипом.

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1988 |

|

SU1583938A1 |

| Устройство для сопряжения ЦВМ и накопителя информации | 1985 |

|

SU1265780A1 |

| Ассоциативное запоминающее устройство | 1986 |

|

SU1388949A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1725261A1 |

| Запоминающее устройство | 1987 |

|

SU1443029A1 |

| Буферное оперативное запоминающее устройство | 1988 |

|

SU1559379A1 |

| Многоканальное буферное запоминающее устройство | 1980 |

|

SU903971A1 |

| Запоминающее устройство | 1984 |

|

SU1251175A1 |

| Запоминающее устройство | 1986 |

|

SU1336102A1 |

| Запоминающее устройство | 1983 |

|

SU1246137A1 |

ЗАПОМИНМОЦЕЕ УСТРОЙСТВО, содержащее формирователь адресных сигналов, выходы которого соедин&ны с входами дешифратора адреса, элементы И, регистрь и группы элементов И, причем первые входы первого и второго элементов И являются ниформационными входами устройства, второй вход первого элемента И является первым входом разрешения записи устройства, а выходы третьего и четвертого элементов И - выходами устройства, первые входы элементов И первой и второй групп подключены к выходам . « даиифратора адреса, вторые входы элементов И . группы соединены с выходом первого элемента И, вторые входы и выходы элементов. И вто1рой группы подключены соответственно к выходам регистров и к одним из входов третьего элемента .И, другой вход которого является первым входом разрешения считывания з стройбтва,. отличающееся тем, что, с целью повышения бЫстрсАействия и увеличения инфо1я«1ационной емкости устройства, в него введены элементы ИЛИ, третья и четвертая группы элементов И, причем первый и второй входы и выходы элементов ИЛИ подключены соответственно к выходам элементов И группы, к выходам элементов И первой rpynrai .и к входам регистров, первые входы и выходы элементов И четвертой группы соеди- , йены соответственно с жлсодами регис1 Si-Ul tffg - Tw ров и с одним из входов четвертого элемента И, первые входы элементов коду к: И третьей группы подключены к выходу второго элемента И, вторые входы элементов И третьей и четвертой rpyntn соединены с выходами дешифратора гщ- S реса, кроме последнего, второй вход второго эл леЪта И и дрУгой -вход четвертого элемента И являются соответственно вторым входом разрешения записи и вторым вводом разрешения i считывания устройства. .:

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Буферное запоминающее устройство | 1972 |

|

SU444240A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Запоминающее устройство | 1978 |

|

SU743031A1 |

| . | |||

Авторы

Даты

1983-04-07—Публикация

1981-12-11—Подача