Изобретение относится к запоминающим устройствам и может быть использовано при создании систем памяти на базе интегральных микросхем памяти (ИМП) со словарной организацией.

Известно запоминающее устройство с исправлением ошибок, в котором для автоматического исправления ошибок, возникаю дих из-за отказов HNm, подлежащие хранению данные кодируются с помощью кодов, исправляющих ошибки. Устройство содержит избыточные, разряда кодирующие и декодирующие блоки ,Г1.

Однако .в этом устройстве число избыточных разрядов, необходимых для исправления ошибок в слове, велико и высока сложность кодирующих и декодирующих блоков.

Наиболее близким по технической сущности к пре.алагаемому изобретению является запоминающее устройство, содержащее накопитель, первые входы которого соединены с выходами адресного блока, вторые входы накопителя соеди-нены с выходами блока записи, первые, вторые, третьи и четвертый входы блока записи соединены соответственно с шинами записи информации и входами блока кодирования, с выходами блока.

кодирования, с инверсными выходами первого регистра и с выходами элемента ИЛИ, входы первого регистра соединены с выходами накопителя, входами блока вычисления синдрома и первыми входами блока сравнения, вторые входы блока сравнения соединены с прямыми выходами первого регистра и с. первыми входами корректирующих суммато10ров по модулю два, выходы блока вычисления синдрома соединены с входами регистра) выходами соединенного с входами элемента ИЛИ. Устройство позволяет производить коррекцию з.авших разрядов при использовании помехоустойчивого кода С2.

Однако известное устройство требует большое число дополнительных разрядов элементов памяти при коррекции

20 четырех или восьми отказов в слове, а также требует сложных кодирующих и декодирующих схем

Целью изобретения является -повышение надежности устройства.

25

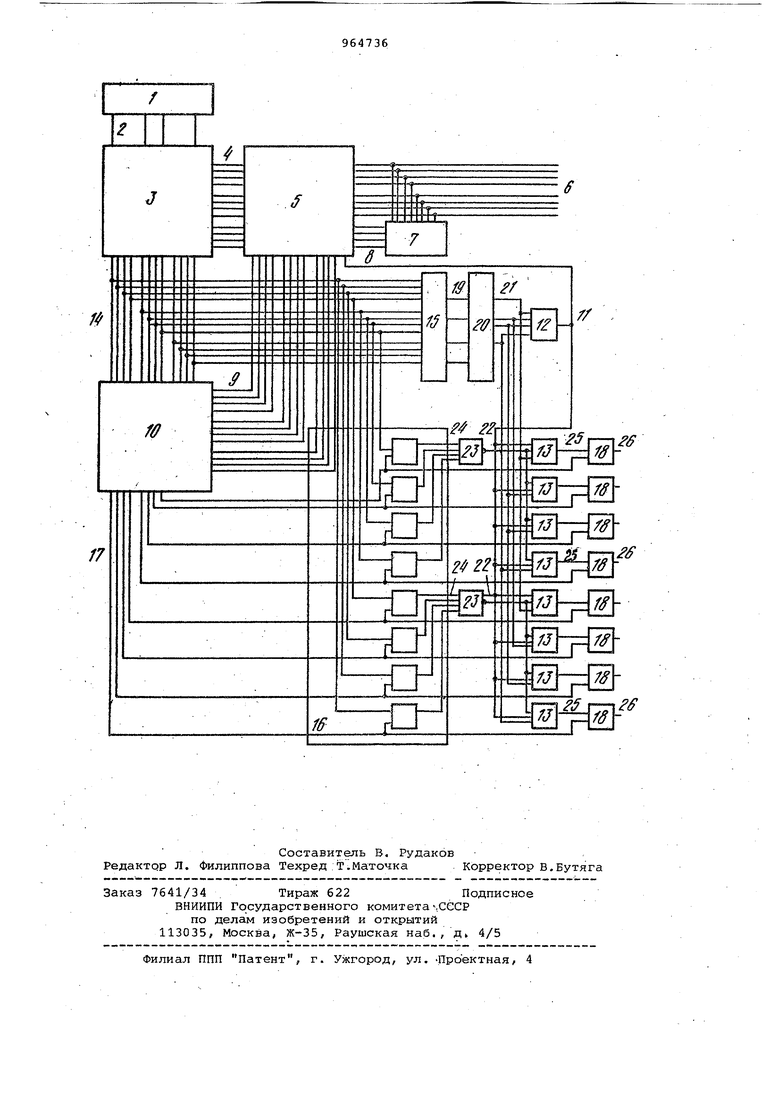

Поставленная цель достигается тем, что в запоминающее устройство с исправлением ошибок, содержащее адресный блок, накопитель, блок записи, первый и второй регистры числа, блок кодирования, схему сравнения, форми3Dрователь проверочных сигналов, сумматоры по модулю два и элемент ИЛИ, причем входы накопителя подключены к выходам адресного блока и блока за си, входов которого и входь блока к одирования объединены и являЮтся одними извходов устройства, а другие входы блока записи соединены сортветственно с выходами блока коди рования И- элементов ИЛИ и инверсными выходами первого регистра числа, пря мые выходы которого подключены к одним из входов схемы сравнения и к пе вым входам сумматоров по модулю два выходы накопителя соединены с входами первого регистра числа, другими входами схемы сравнения и входами формирователя проверочных сигналов, выходы которого подключены к входам второго регистра числа, выходы которого соединены с входами элемента ИЛИ, введены элементы И и элементы И-НЕ, входы которых подключены к выходам схемы сравнения, а выходы соединены с первьми входами элементов И, вторые входы которых подключены к выходам второго регистра числа, третьи входы - к ВЫХОДУ элемента ИЛИ а выходы элементов И соединены с вто рыми входами сумматоров по модулю два. На чертеже изображена структурная схема запоминающего устройства. Запоминающее устройство содержит адресный блок 1, соединенный адресными шинами 2- с первыми входами накопителя 3. Вторые входы накопителя соединены с выходами 4 блока 5 записи. Входы блока 5 записи соединены соответственно с -шинами б записи и входами блока 7 кодирования, с выходами 8 блока 7 кодирования, с инверс нымй выходами 9 первого регистра 10, числа с выходом 11 элемента ИЛИ 12 и входами элементов И 13. Входы реги ра 10 соединены с выходами -накопителя 14, входами формирователя 15 проверочных сигналов и одними из входов схемы 16 сравнения. Другие входы схемы 16 сравнения соединены с прямлми выходами 17 регистра 10 и с первыми входами корректирующих сумматоров 18 по модулю два. Выходы фор мирователя 15 соединены с входами 19 второго регистра 20 числа, выходами соединенного с входами 21 элемента ИЛИ 12 и одними из входов элементов И 13. Другие входы элементов И 13 соединены с выходами 22 элементов 23. Входы элементов И-НЕ соединены с выходами 24 схемы 16 сравнения. Выходы элементов И 13 соединены с вторыми входами 25 сумматоров 18 .по модулю два. Выходы 26 сумматоров 18 являются выходами устройства. Блоки 7 кодирования и формирователя 15 состоят из сумматоров по модулю два. Блок 5 записи разрешает запись ШГформации в накопитель 3 или с шин записи 6 или с инверсных выходов 9 регистра 10 и. может быть реализован на элементах 2-2И-2ИЛИ. . В режиме записи информации устройство работает следующим образом. Двоичное кодовое слово А длины k + Ь, первые k bn. разрядов которого являются информационными, а последние b разрядов контрольными, помещается.в накопитель 3 по адресу, поступающему из адресного блока 1. В блоке 7 кодирования происходит вычисление контрольных; символов- путем суммирования по модулю два блоков по Ь разрядов в каждом. П ри м е р 1. Пусть k 16, ,b 4 , тогда n т r т.е. при построении накопителя с длиной слова в 16 ,разрядов используется четыре ИМП с четырьмя шин-ами записи-считывания каждая и пусть в накопитель записывается инфо)рмация 10001100 О О 1 О 11 1 li Тогда в контрольные разряды записывается информация 100 1, т.е. в накопитель заносится слово 1 О О О 1100 .0010 1111 1001. В режиме считывания информации выходные данные подаются на формирователь 15 и одновременно записываются в регистр 10. Формирователем 15 вырабатывается признак (синдром), записываемый во второй регистр 20, которыйравен нулю, .если ошибок нет, и не равен нулю в противном случае. Если в считываемом слове ошибок нет, то на выходе элемента ИЛИ 12 будет нулевой сигнал, который устанавливает на выходах 25 элементов И 13 нулевые сигналы. Тогда на выходе 26 устройства поступят сигналы с прямых выходов 17 первого регистра 10 без изменения. .. Если же в считываемом слове, имеются ошибки в разрядах из-за отказа любой ОДНОЙ ИМП, тона выходе элемента ИЛИ 12 поя:вится единичный сигнал, который разрешит повторную запись инвертироваиной считанной информации с выходов 9 первого.регистра 10 в накопитель 3. После этого производится контрольное считывание хранимой инвертированной информации по тому же адресу и сравнение ее в схеме сравнения 16 с хранимой неинвертированной информацией в.регистре 10. Запись считанной инвертированной информации в регистр 10 и вычисленного формирователем 15 синдрома в регистр 20 не происходит, т.е. в регистрах 10 и 20 хранится информация, относящаяся к неинвертированному слову. Тогда как инимум на одном из выходов 24 схемы 16 сравнения- появится нулевой сигнал. если искаженным является один из k Ьп информационшлх разрядов. В этом случае на одном из выходов 22 одного из п элементов И-НЕ 23 появит ся единичный сигнал, который откроет одни из элементов И 13, относящиеся к искаженному блоку информации. Поскольку элементы И 13 открыты единич ньм сигналом с выхода элемента ИЛИ 12 то на выходе одних из элементов И 13 появятся сигналы, отображающие ненулевой синдром неинвертированного сло ва . При сложении н сумматорах 18 по модулю два этого синдрома с инфор мацией, относящейся к этому блоку, происходит коррекция считываемой информации из искаженного блока (отказавшей ИМП) . Если же искаженными являются конт рольные разряды, то на выходах 24 схемы 16 сравнения будут единичные сигналы, а на выходах 22 элементов И-НЕ 23 - нулевые .сигналы. Тем самым элементы И 13 будут закрыты и информация, считываемая с регистра 10, поступит на выходы 26 устройства без изменения. Пример 2. -Пусть в примере 1 информация искажена в первом блоке из-за отказа этой , т.е. в регистр 10 с выхода накопителя 3 запи саны число 1111 11000010 1111 1 О О 1. В регистр 20 запишется вычисленный формирователь 15 синдром О 1. При записи в накопитель 3 инвертированного слова 0000 0011 1101 0000 0110 с выходов 14 при контрольном считывании на схему 16 сравнения поступит слово 1111 00111101 О О О О О 1 1 О. Информация в первом блоке совпадает .в схеме 16 сравнения с информацией, считываемой с регистра 10 так как элементы памяти в данной И1Ш находятся постоянно в единичном состоянии. Тем самьн на выходе одного из элементов И-НЕ 23 появится единич ный сигнал. который откроет одни из элементов И 13. Тогда на сумматорах 18 произойдет суммирование синдрома из регистра 20 и .информации из искаженного блока, т.е. о 1 1 1 + +1111 iooo, что соответствует ИСХОДНОЙ подлежащей хранению информации в этом блоке. Таким образом, предлагаемое устройство выполняет те же функции, что и известное, но более эффективн-о с точки зрения числа дополните;.ьных вводимых контрольных разрядов и сложности Кодирующих и декодирующих схем. Формула изобретения Запоминающее устройство с исправлением ошибок, содержёиаее адресный блок, накопит€У1ь, блок записи, первый А второй регистры числа, блок кодирования, схему сравнения, формирователь проверочных сигналов, сумматоры по модулю два и элемент ИЛИ, причем вхо ды Накопителя подключены к выходам адресного блока и блока запи-.-и, одни, из входов которого и входы блока кодйрования объединены и являются одними из входов устройства, а другие входы блока записи соединены соответственно с выходами блока кодирования и элемента ИЛИ и инверсными выходами первого регистра числа, прямые выходы которого подключены к.одним из входов схемы сравнения и к первым входам сумматоров по. модулю два, выходы накопителя соединены с входами первого регистра числа, другими входами схемы сравнения и входами формирователя проверочных сигналов, выходы которого подключены к входам второго регистра числа, выводы которого соединены с входами элемента ИЛИ, о тл и ч а ю щ и -е с я тем, что, с целью повышения надежности устройства, оно содержит элементы И и элементы И-НЕ, входы которых подключены к выходам схемы сравнения, а выхода соединены с первыми входами элементов И, вторые входы которых подключены к выходам второго .регистра числа, третьи входы - к выходу элемента ИЛИ, а выходы элементов И соединены с вторыми входами сумматоров по модулю два. Источники информации, принятые во внимание при экспертизе , 1. Вычислительная техника. Экс . пресс-информация, 1978, 36, с.5-11. . 2. Самофалов К. Г., Корнейчук В. И., Городний А. В. Структурно-логические метода повышения надежности запоминающих устройств. М., Машиностроение, 1976, с. 101-106 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с исправлением ошибок | 1985 |

|

SU1297120A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1725261A1 |

| Запоминающее устройство с исправлением ошибок | 1981 |

|

SU982098A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1048520A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| КОДЕК ПОМЕХОУСТОЙЧИВОГО ЦИКЛИЧЕСКОГО КОДА | 2003 |

|

RU2251210C1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1043743A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1238163A1 |

| Запоминающее устройство с автономным контролем | 1991 |

|

SU1837363A1 |

| Запоминающее устройство | 1981 |

|

SU972590A1 |

Авторы

Даты

1982-10-07—Публикация

1981-03-06—Подача