Изобретение относится к вычислительной технике и может быть использовано при создании запоминающих устройств (ЗУ) повышенной надежности.

Цель изобретения - повышение надежности устройства.

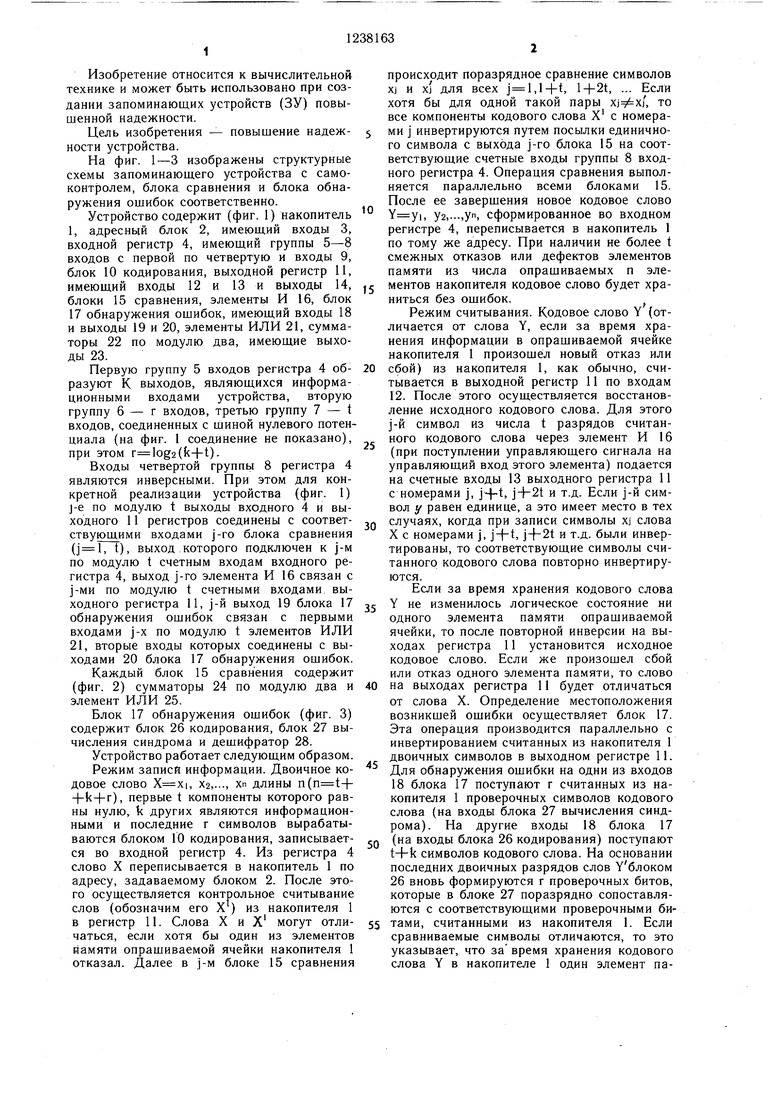

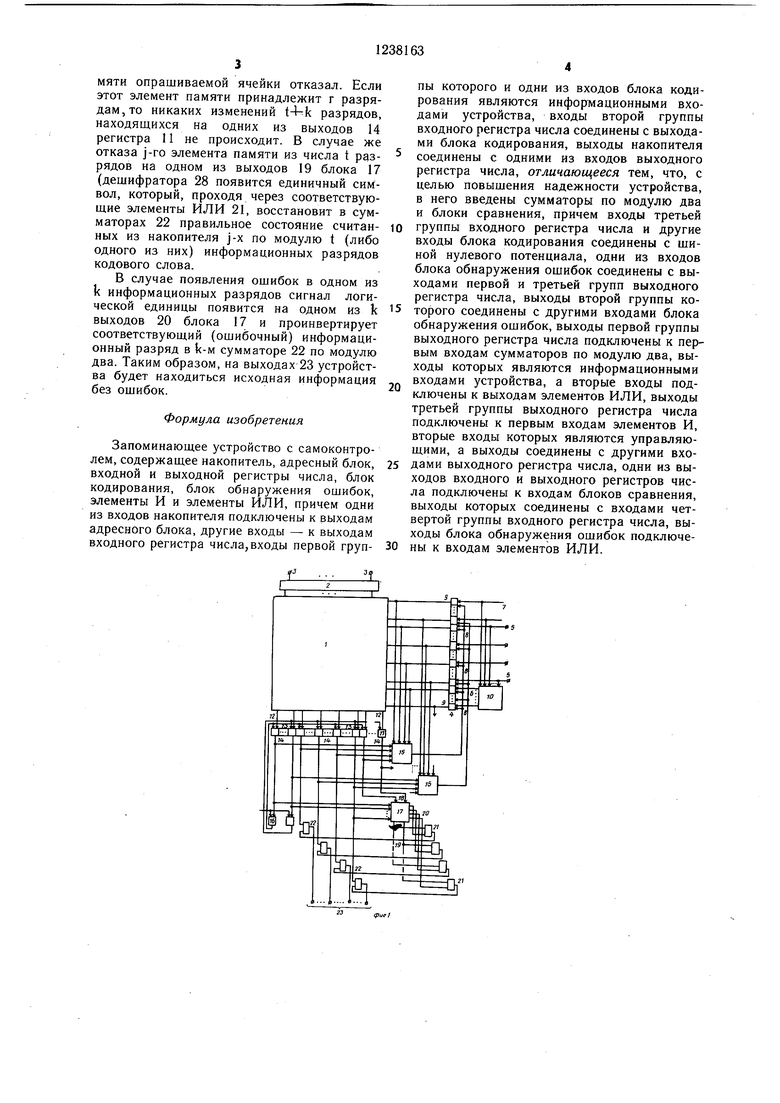

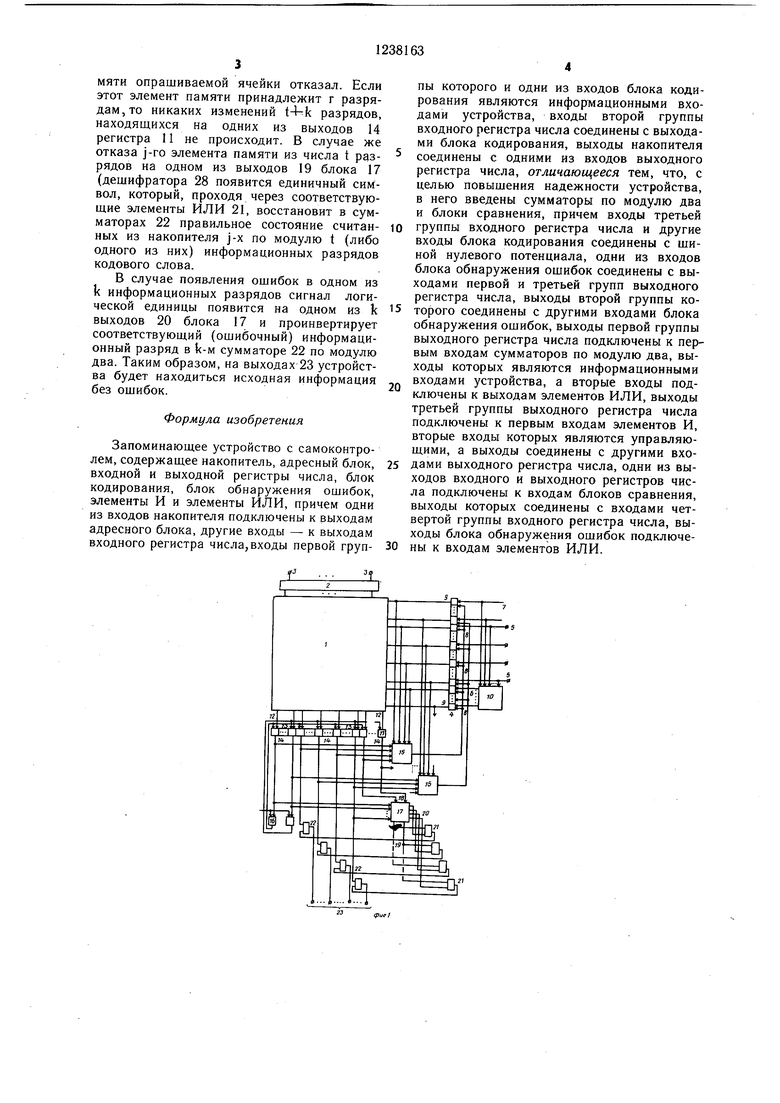

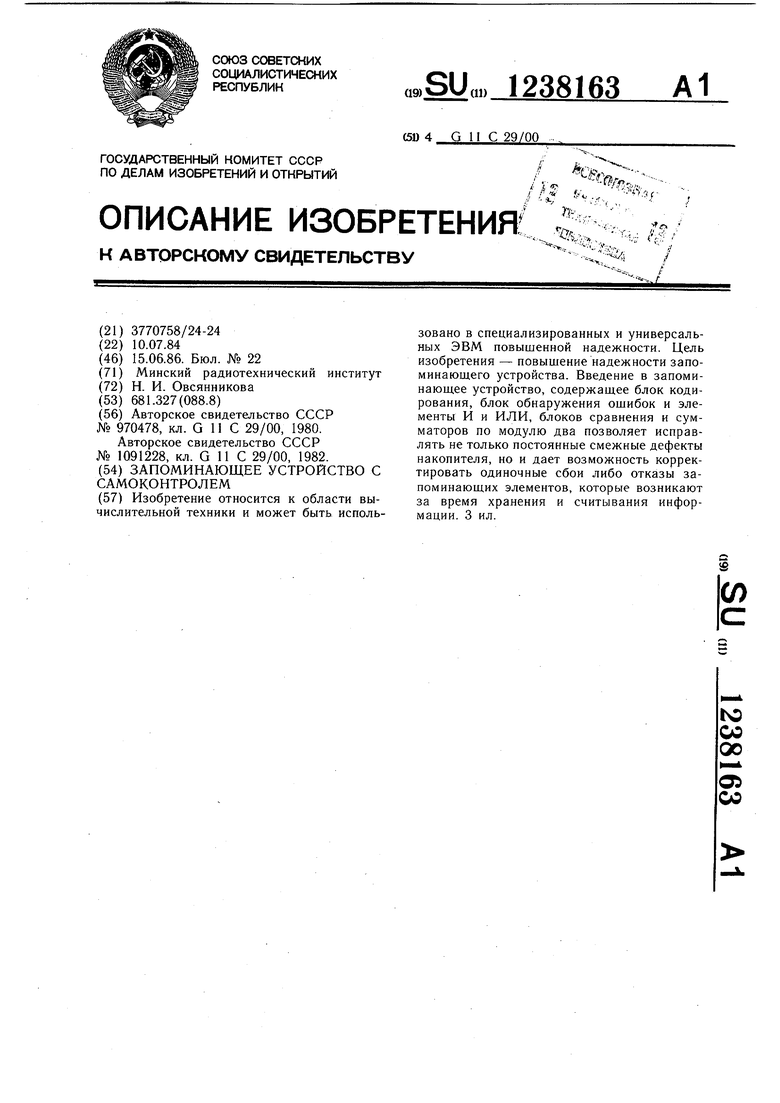

На фиг. 1-3 изображены структурные схемы запоминаюш.его устройства с само- конт эолем, блока сравнения и блока обнаружения ошибок соответственно.

Устройство содержит (фиг. 1) накопитель 1, адресный блок 2, имеющий входы 3, входной регистр 4, имеющий группы 5-8 входов с первой по четвертую и входы 9, блок 10 кодирования, выходной регистр 11, имеющий входы 12 и 13 и выходы 14, блоки 15 сравнения, элементы И 16, блок 17 обнаружения ошибок, имеющий входы 18 и выходы 19 и 20, элементы ИЛИ 21, сумматоры 22 по модулю два, имеющие выходы 23.

Первую группу 5 входов регистра 4 образуют К выходов, являющихся информационными входами устройства, вторую группу 6 - г входов, третью группу 7 - t входов, соединенных с шиной нулевого потенциала (на фиг. 1 соединение не показано), при этом (k+t).

Входы четвертой группы 8 регистра 4 являются инверсными. При этом для конкретной реализации устройства (фиг. 1) j-e по модулю t выходы входного 4 и выходного 11 регистров соединены с соответ- ствующими входами j-ro блока сравнения (j l, t), выход которого подключен к j-м по модулю t счетным входам входного регистра 4, выход j-ro элемента И 16 связан с j-ми по модулю t счетными входами выходного регистра И, j-й выход 19 блока 17 обнаружения ошибок связан с первыми входами J-X по модулю t элементов ИЛИ 21, вторые входы которых соединены с выходами 20 блока 17 обнаружения ошибок.

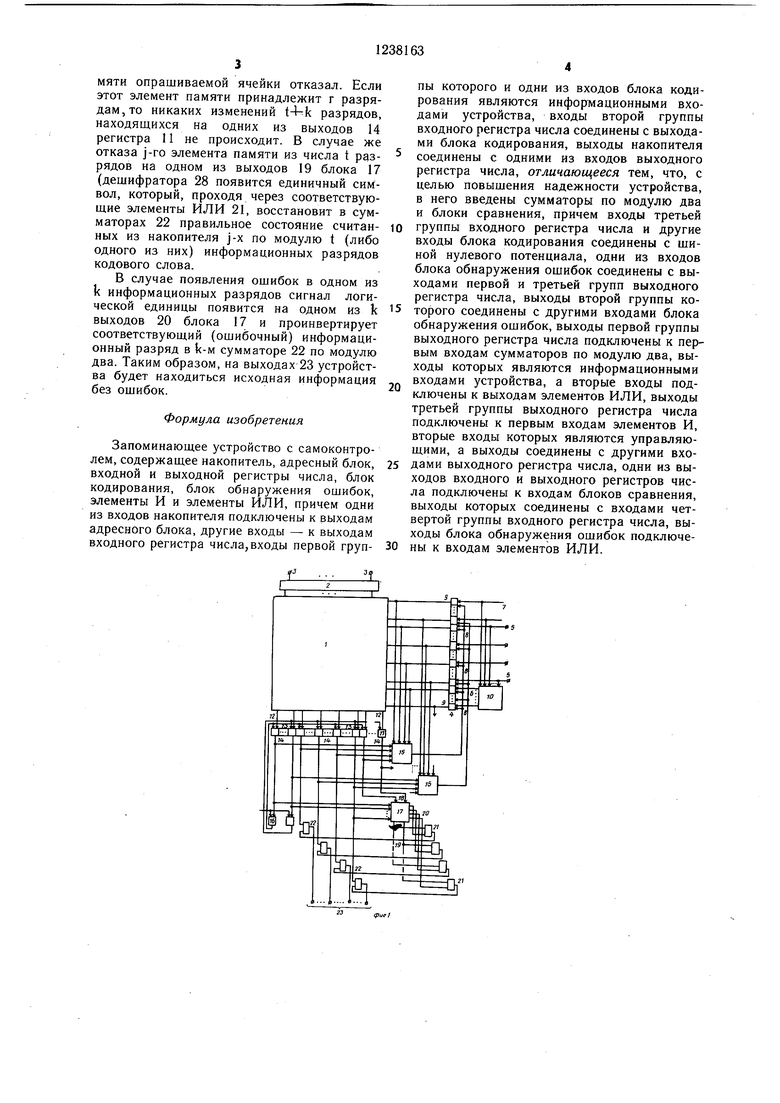

Каждый блок 15 сравнения содержит (фиг. 2) сумматоры 24 по модулю два и элемент ИЛИ 25.

Блок 17 обнаружения ошибок (фиг. 3) содержит блок 26 кодирования, блок 27 вычисления синдрома и дешифратор 28.

Устройство работает следующим образом.

Режим записи информации. Двоичное кодовое слово , Х2,..., хп длины n( -|-k+r), первые t компоненты которого равны нулю, k других являются информационными и последние г символов вырабатываются блоком 10 кодирования, записывается во входной регистр 4. Из регистра 4 слово X переписывается в накопитель 1 по адресу, задаваемому блоком 2. После этого осуществляется контрольное считывание слов (обозначим его X ) из накопителя 1 в регистр 11. Слова X и X могут отличаться, если хотя бы один из элементов памяти опрашиваемой ячейки накопителя 1 отказал. Далее в j-м блоке 15 сравнения

происходит поразрядное сравнение символов XJ и XJ для всех j 1,1+1, l+2t, ... Если хотя бы для одной такой пары , то все компоненты кодового слова X с номерами j инвертируются путем посылки единичного символа с выхода j-ro блока 15 на соответствующие счетные входы группы 8 входного регистра 4. Операция сравнения выполняется параллельно всеми блоками 15. После ее заверщения новое кодовое слово

У|, у2,...,уп, сформированное во входном регистре 4, переписывается в накопитель 1 по тому же адресу. При наличии не более t смежных отказов или дефектов элементов памяти из числа опращиваемых п эле5 ментов накопителя кодовое слово будет храниться без ошибок.

Режим считывания. Кодовое слово Y (отличается от слова Y, если за время хранения информации в опращиваемой ячейке накопителя 1 произошёл новый отказ или

0 сбой) из накопителя 1, как обычно, считывается в выходной регистр 11 по входам 12. После этого осуществляется восстановление исходного кодового слова. Для этого j-й символ из числа t разрядов считанного кодового слова через элемент И 16 (при поступлении управляющего сигнала на управляющий вход этого элемента) подается на счетные входы 13 выходного регистра 11 с номерами j, j-f-t, j-)-2t и т.д. Если j-й символ у равен единице, а это имеет место в тех

Q случаях, когда при записи символы xj слова X с номерами j, j+t, и т.д. были инвертированы, то соответствующие символы считанного кодового слова повторно инвертируются.

Если за время хранения кодового слова

5 Y не изменилось логическое состояние ни одного элемента памяти опрашиваемой ячейки, то после повторной инверсии на выходах регистра 11 установится исходное кодовое слово. Если же произошел сбой или отказ одного элемента памяти, то слово

0 на выходах регистра 11 будет отличаться от слова X. Определение местоположения возникшей ошибки осуществляет блок 17. Эта операция производится параллельно с инвертированием считанных из накопителя 1 двоичных символов в выходном регистре 11. Для обнаружения ощибки на одни из входов 18 блока 17 поступают г считанных из накопителя 1 проверочных символов кодового слова (на входы блока 27 вычисления синдрома). На другие входы 18 блока 17

Q (на входы блока 26 кодирования) поступают t+k символов кодового слова. На основании последних двоичных разрядов слов Y блoкoм 26 вновь формируются г проверочных битов, которые в блоке 27 поразрядно сопоставляются с соответствующими проверочными би5 тами, считанными из накопителя 1. Если сравниваемые символы отличаются, то это указывает, что за время хранения кодового слова Y в накопителе 1 один элемент па5

мяти опрашиваемой ячейки отказал. Если этот элемент памяти принадлежит г разрядам, то никаких изменений t-bk разрядов, находящихся на одних из выходов 14 регистра 11 не происходит. В случае же отказа j-ro элемента памяти из числа t разрядов на одном из выходов 19 блока 17 (дешифратора 28 появится единичный символ, который, проходя через соответствующие элементы ИЛИ 21, восстановит в сумматорах 22 правильное состояние считанных из накопителя j-x по модулю t (либо одного из них) информационных разрядов кодового слова.

В случае появления ошибок в одном из k информационных разрядов сигнал логической единицы появится на одном из k выходов 20 блока 17 и проинвертирует соответствующий (ошибочный) информационный разряд в k-M сумматоре 22 по модулю два. Таким образом, на выходах 23 устройства будет находиться исходная информация без ошибок.

Формула изобретения

Запоминающее устройство с самоконтролем, содержащее накопитель, адресный блок, входной и выходной регистры числа, блок кодирования, блок обнаружения ошибок, элементы И и элементы ИЛИ, причем одни из входов накопителя подключены к выходам адресного блока, другие входы - к выходам входного регистра числа, входы первой группы которого и одни из входов блока кодирования являются информационными входами устройства, входы второй группы входного регистра числа соединены с выходами блока кодирования, выходы накопителя

соединены с одними из входов выходного регистра числа, отличающееся тем, что, с целью повышения надежности устройства, в него введены сумматоры по модулю два и блоки сравнения, причем входы третьей

группы входного регистра числа и другие входы блока кодирования соединены с шиной нулевого потенциала, одни из входов блока обнаружения ошибок соединены с выходами первой и третьей групп выходного регистра числа, выходы второй группы которого соединены с другими входами блока обнаружения ошибок, выходы первой группы выходного регистра числа подключены к первым входам сумматоров по модулю два, выходы которых являются информационными входами устройства, а вторые входы подключены к выходам элементов ИЛИ, выходы третьей группы выходного регистра числа подключены к первым входам элементов И, вторые входы которых являются управляющими, а выходы соединены с другими входами выходного регистра числа, одни из выходов входного и выходного регистров числа подключены к входам блоков сравнения, выходы которых соединены с входами четвертой группы входного регистра числа, выходы блока обнаружения ошибок подключены к входам элементов ИЛИ.

ipuel

/4

фие.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с автономным контролем | 1980 |

|

SU926726A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1725261A1 |

| Устройство для обнаружения и исправления ошибок в непозиционном коде | 1983 |

|

SU1134941A1 |

| Запоминающее устройство с исправлением ошибок | 1985 |

|

SU1297120A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1805503A1 |

| КОДЕК ПОМЕХОУСТОЙЧИВОГО ЦИКЛИЧЕСКОГО КОДА | 2003 |

|

RU2251210C1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU970478A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1211811A1 |

| Устройство для обнаружения и исправления ошибок в блоках памяти | 1988 |

|

SU1525746A1 |

| Запоминающее устройство | 1975 |

|

SU556501A1 |

Изобретение относится к области вычислительной техники и может быть использовано в специализированных и универсальных ЭВМ повышенной надежности. Цель изобретения - повышение надежности запоминающего устройства. Введение в запоминающее устройство, содержащее блок кодирования, блок обнаружения ощибок и элементы И и ИЛИ, блоков сравнения и сумматоров по модулю два позволяет исправлять не только постоянные смежные дефекты накопителя, но и дает возможность корректировать одиночные сбои либо отказы запоминающих элементов, которые возникают за время хранения и считывания информации. 3 ил. ю со 00 Од со

фигЗ

| Запоминающее устройство с самоконтролем | 1981 |

|

SU970478A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1091228A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-06-15—Публикация

1984-07-10—Подача