со

О) О)

Изобретение относится к вьр1исли- тельной: технике и может быть использовано для построения оперативных запоминающих устройств с повышенной достоверностью функционирования.

Цель изобретения - повышение достоверности контроля.

На фиг. 1 представл€ На схема запоминающего устройства с тестовым самоконтролем, на фиг,2 - схема блока управления; на фиг.З - схема распределителя имоульсов

Устройство (фиг,1) содержит нако- питель 1, мультиплексоры данных 2 и адреса 3, группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 4, блок 5 управления, регистр 6 данных, блок 7 формирования сигна-- туры, регистр 8 сигнатуры, блок 9 сравнения, триггер 10, входы данных 11, адреса 12, записи 13, считывания 14, синхронизации 15 и режима 16, выходы данных 17 и ошибки 18, На фиг,1 также показаны связи 19-27,

БЛОК управления (фиг.2) содержит делитель 28 частоты, счетчик 29 адреса, счетчик-модификатор 30, счетчик 31 по модулю три, блок 32 постоянной памяти, мультиплексор 33, распредели тель 3.4 импульсов, элементы и 35,36, элемент НЕ 37. На фиг.2 показаны также связи 38-45,

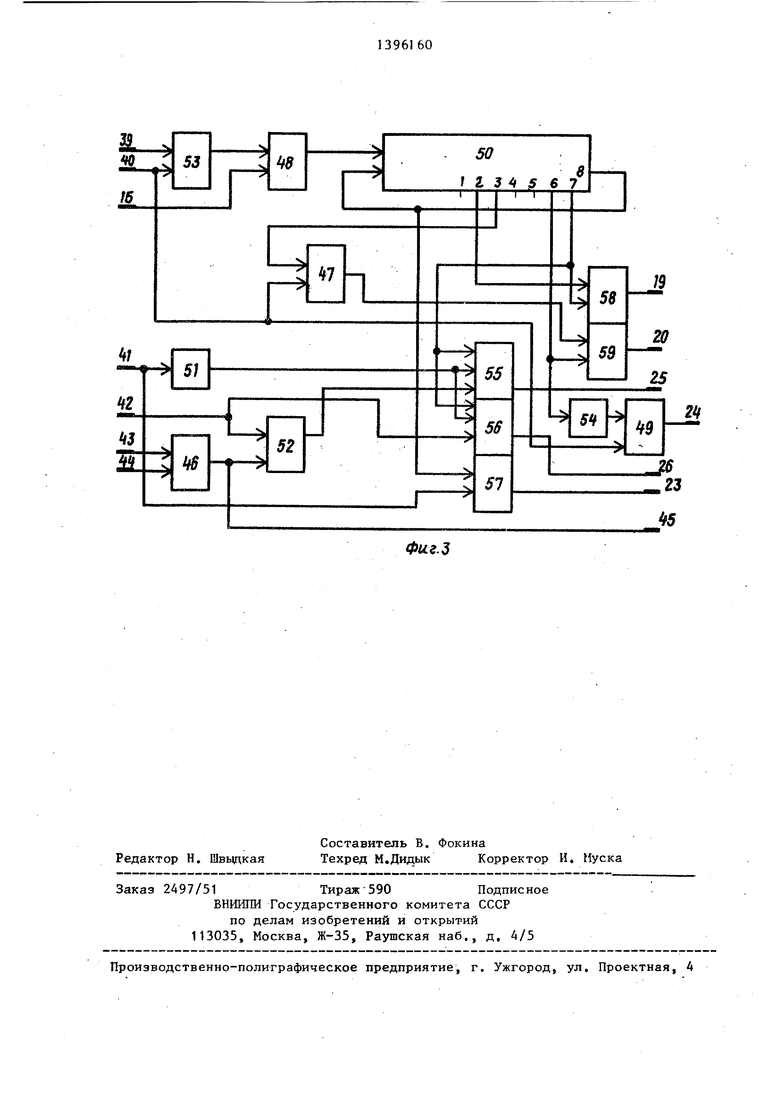

Распределитель импульсов (фиг,3) содержит элементы ИЛИ 46-47, элементы И 48,49, регистр 50 сдвига, элемент НЕ 51, элемент ИЛИ-НЕ 52, элемент ИЛИ 53, элемент НЕ 54, элементы И-НЕ 55,565 элемент ИЛИ 57, RS-триг- геры 58,59,

Блок 5 управлений формирует сигнал окончания контроля 38,

Запоминающее устройство работает в двух режимах: рабочем режиме и в режиме тестового самоконтроля без рарушения информации,

Перед началом работы устройстве: инверсные выходы триггеров 58,59 устанавливаются в единичное состояни а выходы регистра 50 сдвига с первого по восьмой - в состояние 01111111 (цепи установки не показаны),

В рабочем режиме на входе 16 присутствует логический нуль, обеспечивающий передачу данных и адреса с входов 11 и 12 устройства, через hp/л типлексоры 2,3 в накопитель 1, а также выработку сигналов выбора кристалла 19 и записи 20 (в цикле записи) распределителем 34 импульсов.

Q

5

0

5

В режиме тестового самоконтроля на пход 16 подается лог ическая единица, разрешая формирование теста блоком 5 управления и передачу адреса с выходов 21 через мультиплексор 3 и данных с регистра 6 через мультиплексор 2 в накопитель 1.

Принцип тестового самоконтроля запоминающего устройства (ЗУ) без разрушения информации основан на подсчете сигнатуры всего ЗУ с последую- наложением тестовых слон на информацию, записаршую в ЗУ, к ее восстановлением. Алгоритм работы устройства в режиме самоконтроля поясняется табл. 1,

При переводе входа 16 в состояние логической единицы разрешается работа делителя 28 частоты, старший разряд которого- используется для задания типа обращения к накопителю 1 - чтение/запись. Таким образом, в режиме самоконтроля по каждому адресу производится операция чтения и записи. Сигнал чтения (логический ноль) через элемент НЕ 37, мультиплексор 33 и элемент ИЛИ 53 (фиг.2,3) поступает на вход элемента И 48 и разрешает прохождение синхрои1мт1ульсов с входа 15 на вход сдвига регистра 50 (переключение счетчиков 29-31 и сдвиг в регистре 50 осуществляется по переднем фронту импульсов 15), Циклический сдвиг информации в регистре 50 (активный уровень выхода нулевой) обеспечивает формирование сигнала выбора кристалла 19, строба 24 приема считанных данных в регистр: 6, В блоке формирования сигнатуры 7 осуществляется сложение по модулю два каждого считанного из накопителя слова с предьщущим состоянием регистра и сдвиг на один разряд,

После выполнения операции чтения старший разряд делителя 28 частоты переходит в состояние единицы, зада-, вая операцию записи, которая блокируется в первом и втором циклах (см, табл,1) на элементе И 36 сигналом с выхода 45 элемента ИЖ 46, определяющего нулевое состояние двух старших разрядов 43,44 счетчика-модификатора 30,

Таким образом, в первом цикле работы устройства производится чтение по всем адресам ЗУ дпя формирования сигнатуры в регистре 6. По переполнению счетчика адреса 29 (нулевой СИ1- нал 41) формируется строб 25 приема в регистр сигнатуры 8 и импульс обнуления блока 7 формирования сигнатуры

Во втором цикле работы устройства аналогично подсчитывается сигнатура ЗУ, и по импульсу переполнения 41 формируется строб 26 триггера 10, Время подачи строба 26 выбирается достаточным для приема последнего считанного из ЗУ слова в блок 7 формирования сигнатуры и сравнения полученной сигнатуры с записанной в регистре 8, В случае несравнения блок 9 формирует сигнал логической единицы, и по сигналу 26 триггер 10 устанавливается в единицу, фиксируя ошибку.

При правильном формировании эта-i лонной сигнатуры осуществляется пере- ход собственно к тестированию ЗУ, заключающемуся в суммировании в циклах 3,5,7 по модулю два информации в ЗУ с тестовыми словами MTi в соответствии с табл,2 и в восстановлении в циклах 4,6,8 исходной информации в ЗУ путем повторного сложения с тестовыми словами MTi. Примеры тестовых слов MTi приведены в табл,3.

В качестве примера рассмотрим работу устройства в циклах 3,4. Считанная из накопителя 1 по нулевому адресу информация складывается по модулю два на элементах ИСКЛЮЧАЮЩЕЕ ИЛИ 4.с тестовым словом МГ1 (см.табл,2) и по стробу 24 записывается в регистр 6 данных. Далее по нулевому адресу производится запись модифицирова1 ного слова с регистра 6 через мультиплексор 2 в накопитель 1, Далее производится модификация слова по первому адресу и т,д. По импульсу 41 перепол- нения происходит формирование сигнала обнуления блока 7,

Работа ЗУ в четвертом цикле аналогична с той лишь разницей, что путем повторного сложения по модулю .два на элементах 4 происходит восстановление информации в ЗУ и формирование сигнатуры в блоке 7 сравнение полученной сигнатуры в блоке 9 сравнения и фиксация ошибки в триггере 10 по стробу 26, формируемому в 2,4,6,8 циклах.

Формирование последовательности тестовых слов в соответствии с табл,2 осуществляется в блоке 32 постоянной памяти, младшие разряды адреса которого подключены к выходам счетчика

5

5

0

5

0

5

0

5

31 по модулю три, а старшие разряды адреса - к выходам счетчика - модификатора 30, осуществляющего, подсчет числа циклов, В табл.4 приведено распределение тестовой информации в блоке 32 постоянной памяти,

В случае возникновения ошибки на выходе 18 устройства формируется сигнал ошябки, а нулевым сигналом 27 с инверсного выхода триггера 10 блокируется на элементе И 35 поступление синхроимпульсов на делитель 28 частоты и контроль прекращается.

В случае исправной работы устройства нулевым сигналом с инверсного выхода старшего разряда счетчика-модификатора 30 блокируется поступление синхроимпульсов через элемент И 35, а единичный сигнал с прямого выхода старшего разряда счетчика 30 nocTsmaeT на выход 38 ок.ончания контроля устройства.

Таким образом, в запоминающем устройстве обеспечивается полная тестовая проверка накопителя без разруще- ния записанной в накопитель информации.

Формула изобретения

Запоминающее устройство с тестовым самоконтролем, содержащее накопитель, вхзд записи которого соединен с одно- икенным выходом блока управления, входы синхронизации, записи и считывания которого являются одноименными входами устройства, мультиплексор адреса и мультиплексор данных, информационные входы первой- группы которых являются соответственно адресными и информационными входами устройства, регистр данных, отличающееся тем, что, с целью повьшения достоверности контроля, в устройство введены группа элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, блок формирования сигнатуры, регистр сигнатуры, блок сравнения и триггер, причем адресные и информационные входы накопителя подключены соответственно к входам мультиплексора адреса и мультиплексора данных, информационные входы второй группы которых соединены соответственно с адресными выходами блока управления и с выходами регистра данных, информационные входы которого подключены к выходам элементов ИСКЛЮЧ ХОДЕЕ 1ШИ

группы и к информационным входам блока формирования сигнатуры, выходы которого подключены к информационньтм входам регистра сигнатуры и к входам первой группы блока сравнения, входы второй группы которого соединены с выходами регистра сигнатуры, а выход подключен к информационному входу триггера, прямой выход которого явля- ется выходом ошибки ус тройства, инп-- версный выход триггера соединен с входом признака окончания контроля блока управления, выходы групп которого подключены к вторым входам эле- ментов ИСКЛЮЧАЩЕЕ 1ШИ группы, а вход задания режима устройства соединен с первым входом блока формирования сигнатуры, с первым входом триггера, с управляющим входом мультиплексора адреса и мультиплексора данных и с входом признака режима блока управления, первый, второй, третий и четвертый выходы блока управления соединены соответственно с управляющими входами регистра данных, блока формирования сигнатуры, регистра сигнатуры и триггера, выход окончания контроля блока управления является одноименным въг- ходом устройства, а выход выбора кристалла подключен к одноименному входу накопителя, выходы которого соединены с первыми входами элементов ИСКЛЮ ШОП ЕЕ ИНН группы и являются информационными выходами устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Сигнатурный анализатор | 1986 |

|

SU1386995A1 |

| Устройство для контроля цифровых узлов | 1985 |

|

SU1238085A2 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1287240A1 |

| Запоминающее устройство | 1985 |

|

SU1249594A1 |

| Устройство для исследования графов | 1984 |

|

SU1238099A1 |

| Устройство для формирования сигнала прерывания | 1987 |

|

SU1432522A1 |

| Сигнатурный анализатор | 1989 |

|

SU1756890A1 |

| Устройство для управления динамической памятью | 1987 |

|

SU1524089A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1539782A2 |

| Оперативное запоминающее устройство | 1982 |

|

SU1088066A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения оперативных запоминающих устройств с повьшенной достоверностью функционирования. Цель изобретения - повышение достоверности контроля. Устройство содержит накопитель 1, мультиплексоры адреса 2. и данных 3, регистр 6 данных. Повышение достоверности контроля достигается введением группы 4 элементов ИСКЛЮЧАЮЩЕЕ {ШИ, блока 7 формирования сигнатуры, регистра -8 сигнатуры, блока 9 сравнения, триггера, блока равления, служащих для обеспечения полной тестовой проверки накопителя без -разрушения записанной в нем информации, З.ил,, 4 табл. е

Чтение Подсчет сигнатуры

-Чтение Подсчет сигнатуры

Чтение- Наложение теста модификация--запись

Чтение- Восстановление -моди- информации и фика- подсчет сигна- ция-за- туры пись

То же То же

То же То же

Таблица 1

Т а б -л и ц а 2

Фиг.З

| Оперативное запоминающее устройство с самоконтролем | 1984 |

|

SU1156145A1 |

Авторы

Даты

1988-05-15—Публикация

1986-11-28—Подача