(54) УСТРОЙСТВО ЦИКЛОВОГО ФАЗИРОВАНИЯ АППАРАТУРЫ ПЕРЕДАЧИ ДВОИЧНЫХ СИГНАЛОВ

. .. 1

Изобретение ОТНОСИТСЯ к технике передачи дискретной информации, а именно к устройствам синхронизации по циклам передающей и приемной частей аппаратуры передачи двоичных сигналов при использовании распределенной ,синхрокомбинации.

Известно устройство циклового фазирования аппаратуры передачи двоичных сигналов, содержащее последовательно соединенные входной блок стробирования, блок коррекции, дешифратор и блок памяти, выход которого подсоединен к объединенным вторым входам блока коррекции и дешифратора, а также решающий блок 1.

В этом устройстве в процессе вхождения в синхронизм осуществляется параллельный поиск синхрокрмбинации (СК) на всех возможных местах ее размещения в цикле, но требуется запоминание значительно меньшего объема информации.

Такое устройство обеспечивает малое время вхождения в синхронизм, однако точность фазирования невелика.

Цель изобретения - повышение точности фазиров&ния.

Поставленная цель достигается тем, что устройство циклового фазирования

аппаратуры передачи двоичных сигналов, содержащее последовательно соединенные входной блок стробирования, блок коррекции, дешифратор и блок памяти, выход которого подсоединен к объединенным вторым входам блока коррекции и дешифратора, а также решающий блок,введены последовательно соединенные блок контроля син10хронизма, элемент И и сумматор,пер вый выход которого через решающий блок подсоединен к первому входу блока контроля синхронизма, ко второму входу которого, объединенному со вторым входом элемента И, подключен второй выход дешифратора,, первый вход которого подсоединен ко второму входу сумматора, к третьему входу которого подсоединен выход блока

20 контроля синхронизма, четвертый вход сумматора объединен со вторым входом дешифратора, а второй выход сумматора подсоединен ко второму входу бЯока памяти.

25

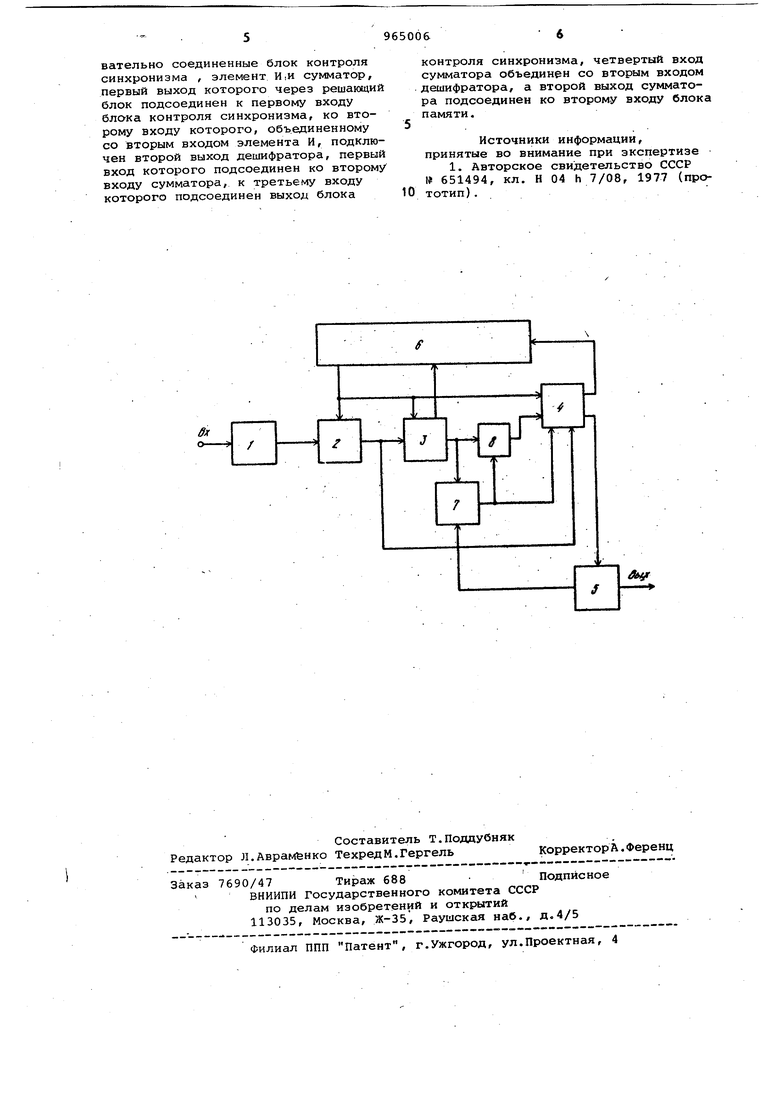

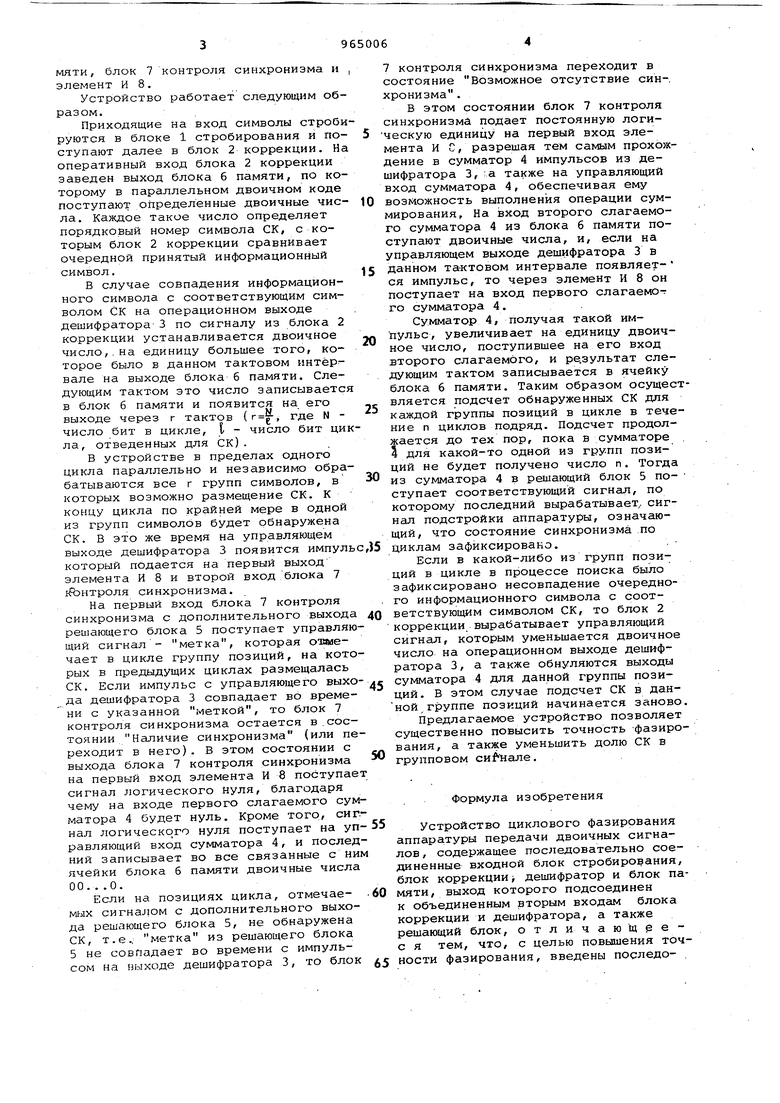

На чертеже изображена структурноэлектрическая схема устройства.

Устройство циклового фазирования содержит входной блок 1 стробирования,, блок 2 коррекции, дешифратор 3, сум30матор 4, решающий блок 5, блок 6 памяти, блок 7 контроля синхронизма н , элемент И 8.

Устройство работает следующим образом.

Приходящие на вход символы стробируются в блоке 1 стробирования и поступают далее в блок 2 коррекции. На оперативный вход блока 2 коррекции заведен выход блока 6 памяти, по которому в параллельном двоичном коде поступают определенные двоичные числа. Каждое такое число определяет порядковый номер символа СК, с которым блок 2 коррекции сравнивает очередной принятый информационный символ,

В случае совпадения информационного символа с соответствующим символом СК на операционном выходе дешифратора 3 по сигналу из блока 2 коррекции устанавливается двоичное число,-на единицу большее того, которое было в данном тактовом интервале на выходе блока 6 памяти. Следующим тактом это число записывается в блок 6 памяти и появится на его

ii

где N выходе через г тактов

р с

число бит в цикле, I - число бит цикла, отведенных для СК).

В устройстве в пределах одного цикла параллельно и независимо обрабатываются все г групп символов, в которых возможно размещение СК. К концу цикла по крайней мере в одной из групп символов будет обнаружена СК. В это же время на управляющем выходе дешифратора 3 появится импульс который подается на первый выход элемента И 8 и второй вход блока 7 1 нтроля синхронизма.

На первый вход блока 7 контроля синхронизма с дополнительного выхода решающего блока 5 поступает управляющий сигнал - метка, которая отяаечает в цикле группу позиций, на которых в предыдущих циклах размещалась СК. Если импульс с управляющего выхода дешифратора 3 совпадает во времени с указанной меткой, то блок 7 контроля синхронизма остается в.состоянии Наличие синхронизма (или переходит в него). В этом состоянии с выхода блока 7 контроля синхронизма на первый вход элемента И 8 поступает сигнал логического нуля, благодаря чему на входе первого слагаемого сумматора 4 будет нуль. Кроме того, сигнал логического нуля поступает на управляющий вход сумматора 4, и последний записывает во все связанные с ним ячейки блока 6 памяти двоичные числа 00...О.

Если на позициях цикла, отмечав- . мьлх сигналом с дополнительного выхода решающего блока 5, не обнаружена СК, т.е.. метка из решающего блока 5 не совпадает во времени с импульсом на выходе дешифратора 3, то блок

7 контроля синхронизма переходит в состояние Возможное отсутствие синхронизма.

В этом состоянии блок 7 контроля синхронизмй подает постоянную логическую единицу на первый вход элемента И С, разрешая тем самым прохождение в сумматор 4 импульсов из дешифратора 3,;а также на управляющий вход сумматора 4, обеспечивая ему возможность выполнения операции суммирования. На вход второго слагаемого сумматора 4 из блока 6 памяти поступают двоичные числа, и, если на управляющем выходе дешифратора 3 в данном тактовом интервале появляется импульс, то через элемент И 8 он поступает на вход первого слагаемо-г го сумматора 4.

Сумматор 4, получая такой импульс, увеличивает на единицу двоичное число, поступившее на его вход второго слагаемого, и ре.зультат следующим тактом записывается в ячейку блока 6 памяти. Таким образом осущесвляется подсчет обнаруженных СК для каждой группы позиций в цикле в течение п циклов подряд. Подсчет продолfaeTCH до тех пор, пока в сумматоре для какой-то одной из групп позиций не будет получено число п. Тогда из сумматора 4 в решающий блок 5 поступает соответствующий сигнал, по которому последний вырабатывает сигнал подстройки аппаратуры, означающий, что состояние синхронизма по циклам зафиксировано.

Если в какой-либо из групп позиций в цикле и процессе поиска было зафиксировано несовпадение очередного информационного символа с соответствующим символом СК, то блок 2 коррекции вырабатывает управляющий сигнал, которым уменьшается двоичное число на операционном выходе дешифратора 3, а также обнуляются выходы сумматора 4 для данной группы позиций. В этом случае подсчет СК в данной группе позиций начинается заново

Предлагаемое устройство позволяет существенно повысить точность фазирования, а также уменьшить долю СК в групповом си нале.

Формула изобретения

Устройство циклового фазирования аппаратуры передачи двоичных сигналов , содержащее последовательно соединенные входной блок стробирования, блок коррекции -, дешифратор и блок памяти, выход которого подсоединен к объединенным вторым входам блока коррекции и дешифратора, а также решающий блок, отличающеес я тем, что, с целью повышения точности фазирования, введены последо- .

вательно соединенные блок контроля синхронизма , элемент и.и сумматор, первый выход которого через решающий блок подсоединен к первому входу блока контроля синхронизма, ко второму входу которого, объединенному со вторым входом элемента И, подключен второй выход дешифратора, первый вход которого подсоединен ко второму входу сумматора, к третьему входу которого подсоединен выход блока

контроля синхронизма, четвертый вход сумматора объединен со вторым входом дешифратора, а второй выход сумматора подсоединен ко второму входу блока памяти.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 651494, кл. Н 04 h 7/08, 1977 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство циклового фазирования аппаратуры передачи двоичных сигналов | 1977 |

|

SU651494A1 |

| УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2021 |

|

RU2782473C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2003 |

|

RU2231228C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2284665C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2007 |

|

RU2348117C1 |

| Устройство цикловой синхронизации | 1985 |

|

SU1358104A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2810267C1 |

| СПОСОБ СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2812335C1 |

| Устройство циклового фазирования аппаратуры передачи двоичных сигналов | 1986 |

|

SU1415449A1 |

вх

Авторы

Даты

1982-10-07—Публикация

1981-03-16—Подача