(5) УСТРОЙСТВО для КОНТРОЛЯ ПЕЧАТИ ИНФОРМАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для редактирования | 1982 |

|

SU1117669A1 |

| Устройство для контроля печати информации | 1980 |

|

SU898462A1 |

| Устройство для задания программы | 1979 |

|

SU849148A1 |

| Устройство для приема и обнаружения комбинации двоичных сигналов | 1987 |

|

SU1429148A2 |

| Устройство для сопряжения вычислительной машины с каналом связи | 1985 |

|

SU1291994A1 |

| Генератор псевдослучайной последовательности импульсов | 1979 |

|

SU866716A1 |

| Устройство для приема и обнаружения комбинации двоичных сигналов | 1987 |

|

SU1413656A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| Устройство для ввода информации | 1986 |

|

SU1383330A1 |

| Устройство для отображения информации | 1990 |

|

SU1737499A1 |

1

Изобретение относится к вычислительной технике, в частности к устройствам вывода информации из ЭВМ.

По основному авт. св. № известно устройство, содержащее первый блок, памяти, выход которого соединен с входом матричной печатающей головки, и матричный оптический считывающий блок, сдвиговый регистр, сумматор, распределитель и второй блок памяти, вход которого соединен с входом первого блока памяти, выходы матричного оптического считывающего блока соединены с входами сдвигового регистра, первый выход которого соединен с входами распределителя, выходы которого соединены с другими выходами сдвигового регистра и с первыми входами сумматора, вторые входы которого соединены с выходом второго блока памяти. Основное устройство содержит также входной и выходной коммутаторы.

Работа устройства осуществляется по следующему алгоритму.

Каждой колонке геометрии знака

присваивается двоичный разряд. В сумматоре накапливается сумма кодов геометрии знака последовательно по строкам разложения. Информация с матричного оптического считывающего блока поступает в сдвиговый регистр

IQ и с помощью распределителя подается на сумматор. Заранее рассчитанный для каждого знака дополнительный код, хранящийся в блоке памяти, после распечатки всех строк разложения

t5 подается на сумматор.- Сумма, получаемая при суммировании всех строк разложения знаковой дополнительный дают первона.чал)ный код знака 0 младших (до 7 разряда) и старших

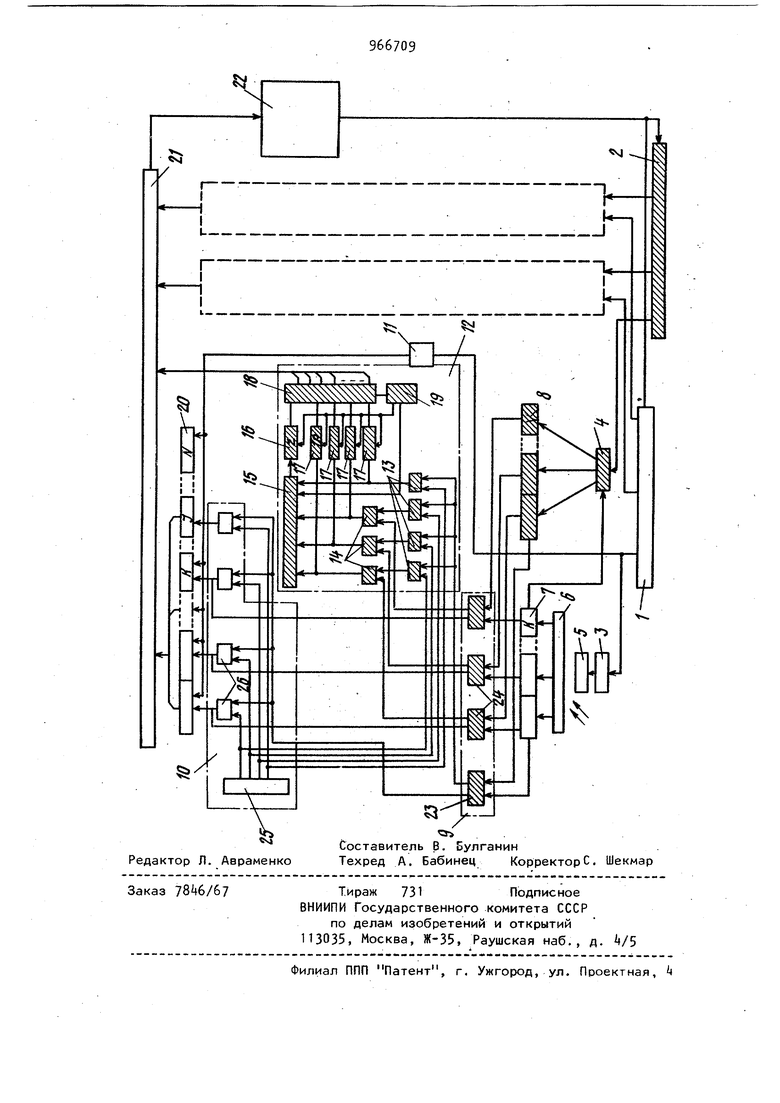

20 разрядах, которые можно отбросить или использовать для контроля остатка, так как остаток суммы одинаков для всех знаков. Таким образом, на выходе сумматора получается код зна ка в двоичной форме, который через выходной коммутатор поступает в ЭВМ для сравнения информации с эталоном Однако замкнутый цикл контроля буквенно-цифровой информации предъявляет чрезвычайно жесткие требова ния к качеству распечатываемой информации, геометрии знаков, лентопротяжному или любому другому подаю щему механизму, а также к носителю информации. Это приводит к большому количеству брака, резко снижает производительность устройства печати, требуют ся большие материальные и временные ресурсы для изготовления заданной продукции. В известном устройстве принят за основу абсолютный контроль каждого знакоместа в контролиру емом символе, так как нераспечатка одной условной точки в знаке либо ее несчитывание автоматически приводит к браку, а следовательно, к ,по торению информации, так как при несовпадении полученного и эталонного кодов не имеется никакого критерия по их несовпадению. Цель изобретения - увеличение быс родействия устройства. Благодаря введению дополнительного критерия признака брака символа и в зависимос ти от требований к контролируемому тексту можно программным путем устанавливать требуемый уровень контроля каждого символа и применять уст ройство для контроля текстов различного качества печати и различного на начения. Поставленная цель достигается тем, что в устройство введены второй входной коммутатор, третий блок памя ти, элемент И-НЕ, группа элементов И-НЕ, второй сдвиговый регистр и бло формирования контрольной суммы, выход которого соединен с дополнительными входами выходного коммутатора, вход первого сдвигового регистра соединен с входом второго сдвигового регистра, выход которого соединен с первым входом третьего блока памяти , выход которого соединен с входо второго сдвигового регистра, выходы которого соединены с первым входом элемента И-НЕ и с первыми входами элементов И-НЕ группы, вторые входы которых соединены с выходамигруппы первого сдвигового регистра, выход которого соединен с вторым входом элемента И-НЕ, первый выход которо-г го соединен с входом первого распределителя импульсов, выходы второй группы которого соединены с входами первой группы блока формирования контрольной суммы, входы второй группы которого соединены с первыми выходами элементов Н-НЕ группы, вторые выходы которых соединены со входами, первого распределителя импульсов, второй выход элемента И-НЕ соединен с входом блока формирования контрольной суммы. Кроме того, первый распределитель импульсов содержит формирователь импульсов, выходы которого являются выходами первого- распределителя импульсов и соединены с первыми входами элементов И, вторые входы которых объединены и являются входом первого распределителя импульсов, выходы элементов И являются входами первого рас;пределителя импульсов. Блок формирования контрольной суммы содержит группы элементов И, первые входы которых являются входами первой группы блока формирования контрольной суммы, вторые входы элементов И группы объединены и являются входом блока формирования контрольной суммы, выходы элементов И группы соединены с первыми входами элементов ИЛИ, вторые входы которых являются входами второй группы блока формирования контрольной суммы, выходы сэлементов ИЛИ соединены с входами « оуппы-преобразователя кодов и с первыми Входами счетчиков группы, выходы которых соединены с входами группы третьего регистра, выход которого является выходом блока формирования контрольной суммы, генератор импульсов, первый, второй и третий выходы которого соединены соответственно с первым входом третьего регистра , с объединенными вторыми входами счетчиков группы и с входом преобразования кодов, выход которого соединен с первым входом счетчика, второй вход которого соединен со вторым ыходом генератора импульсов, выход четчика соединен со вторым входом ретьего регистра. На чертеже представлена структурая схема устройства. Устройство содержит первый и втоой входные коммутаторы 1 и 2, первый блок 3 памяти, второй блок 4 па мяти, матричную печатающую головку 5, матричный оптический считывающий блок 6, первый сдвиговый регистр 7, второй сдвиговый регистр 8, второй распределитель 9 импульсов, первый распределитель 10 импульсов, третий блок 11 памяти, блок 12 формировани контрольной суммы, группу элементов И 13, элементы ИЛИ 1, преобразователь 15 кодов, счетчик 16, группу счетчиков 17, третий регистр 18, ге нератор 19 импульсов, сумматор 20, выходной коммутатор 21, ЭВМ 22, эле мент И-НЕ 23, группу элементов ИНЕ 2, формирователь 25 импульсов, элементы И 26. Устройство работает следующим об разом. Из ЭВМ 22 двоичная кодовая последовательность знаков строки текст поступает на первый входной коммут тор 1. С рассчитанным временным сдв гом, который определяется взаимным расположением линии печати и линии считывания, та же двоичная кодовая последовательность знаков строки те ста поступает на второй входной ком татор 2. Входные коммутаторы 1 и 2 распределяют поступающие знаки последовательно в первый блок 3 памяти и втррой блок k памяти каждого канала« в ёоответствии с числом символов в строке. В первом и втором блоках памяти 3 и 4 хранится информация о пространственной геометрии знаков. Отсюда знаки в виде пространственновременной последовательности сигналов поступают на матричную печатающ ю головку J eчaтaющeгo устройства ;5 и во второй сдвиговый регистр 8 со второго блока памяти. Отпечатан ный знак считывается матричным оптическим считывающим блоком 6, после чего полученное двоичное кодовое чис ло, соответствующее строчке разложения, поступает на первый регистр сдвига 7 и далее на второй распределитель импульсов 9, выполненный на логических элементах И-НЕ 23 и 2А,. На входы распределителя 9 синхронно со считанной информацией поступает также эталонное двОичное кодовое чис ло. Второй распределитель импульсов 9 выполнен таким образо, что, при совпадении информации по каждому разряду, она направляется первым рас пределителем 10 импульсовJ содержащим формирователь 25 импульсов и 9 элементы И 2б в сумматор 20 параллельным двоичным кодом, В случае же отсутствия информации по какомулибо разряду, с первого сдвигового регистра 7 информация направляется вторым распределителем 9 импульсов через группу элементов И 13 и элементы ИЛИ И на вход преобразователя 15 кодов, а также в соответствующий разрядный счетчик 17 группы блока 12 формирования контрольной суммы. После каждого построчного сложения информация из преобразователя 15 кодов переносится в счетчик 16. Аналогичным образом проводится суммирование и контроль по столбцам разложения с использованием второго распределителя 9 импульсов, выполненного на логических элементах И-НЕ 23 и 2 и группы элементов И 13 и элементов ИЛИ , которые работают по сигналам первого распределителя 10 импульсов. Таким образом, в сумматоре 20 накапливается сумма кодов о геометрии знака последовательно по строкам разложения, в сметчике 16 накапливается информация об общем количестве ошибок, а разрядные счетчики 17 группы хранят информацию о месте ошибки в геометрии контролируемого символа. После считывания всего знака в сумматоре 20 записывается сумма двоичных чисел, соответствующая геометрическому разложению знака по строкам и столбцам, Далее к полученной в сумматоре 20 сумме добавляется дополнительный код из третьего блока 11 памяти, рассчитанный для каждого знака. Полученный двоичный код (действительнь1Й или искаженный) т|эанс лируется в ЭВМ 22 с последующей передачей информация из блока 12 формирования контрольной суммы, для чего информация со счетчиков 17 группы по сигналам генератора 19 импульсов пос . и ледовательно переносится в третий регистр 18 и через выходной коммутатор 21 в виде служебной информации передается в ЭВМ 22, Технико-экономическая эффективность предлагаемого изобретения по сравнению с основным устройством заключается в расщи|Ьении функциональных возможностей устройства, увеличении выпуска готовой продукции, резком снижении требований к печатной продукции в зависимости от ее назначения и использования, экономии нос.итёля за счет уменьшения бракованных Текстов. Формула изобретения 1-. Устройство для контроля печати информации по авт. св. № , о т личающееся тем, что, с целью увеличения быстродействия устройства, в него введены второй входной коммутатор, третий блок памяти,, элемент И-НЕ, группа элементов И-НЕ, второй сдвиговый регистр и блок формирования контрольной суммы, выход которого соединен с дополнительными входами выходного коммутатора, вход первого сдвигового регистра соединен- с входом второго сдвигового регистра, выход которого соединен с Iпервым входом третьего блока , выход которогосоединен с входом второго сдвигового регистра, выходы которого Соединены с .первым входом элемента ИгНЕ И с первыми входами элементов И-НЕ группы, вторы входы которых соединены с выходами группы первого сдвигового регистра, выход которого соединен с вторым( входом элемента И-НЕ, первый выход которого соединен с входом первого распределителя импульсов, выхода второй группы которого соединены со входами первой группы блока формиро вания контрольной суммы, входы -.второй группы которого соединены с пер выми выходами элементов И-НЕ группы, вторые выходы которых соединены с входами первого распределителя импульсов, второй выход элемента И-НЕ соединен с входом блока формировании контрольной суммы. 2. Устройство по п. 1, о т л ичающееся тем, что первый распределитель импульсов содержит формирователь импульсов, выходы которого являются выходами первого распределителя импульсов и соединены с первыми входами элементов И, вторые входы которых объединены и являются входом первого распределителя импульсов, выходы элементов И являются входами, первого распределителя импульсов. 3. Устройство по п. 1. о т л ич а ю 1Д е е с я тем, что блок формирования контрольной суммы содержит группу элементов И, первые входы которых являются входами первой группы блока формирования контрольной суммы, вторые входы элементов И Группы объединены и являются входом блока формирования контрольной суммы, выходы элементов И группы соединены с первыми входами элементов ИЛИ, вторые входы которых являются входами второй группы блока формирования контрольной суммы, выходы элементов ИЛИ соединены с входами группы преобразователя и с первыми входами счетчиков группы, выходы которых соединены с входами группы третьего регистра, выход которого является выходом блока Формирования контрольной суммы, генератор импульсов, первый, второй и третий выходы которого соединены соответственно с первым входомтретьего регистра, с объединенными вторыми входами счетчиков группы и со входом преобразователя кодов, выход которого соединен с первым входом счетчика, второй вход которого соединен со вторым выходом генератора импульоов, выход счетчика соединен свторым входом третьего регистраГ

Авторы

Даты

1982-10-15—Публикация

1981-03-31—Подача