(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ СХЕМ УПРАВЛЕНИЯ ТИРИСТОРНЫМИ ПРЕОБРАЗОВАТЕЛЯМИ

1

Изобретение относится к эпектроизмеритепьной технике и может быть использовано при диагностике тиристорных преобразоватепей частоты.

Известно устройство дпя контроля поспедоватепьности импульсов, которое содержит триггеры контроля и памяти и три схемы совпадения, соединенные таким образом, что позволяет в серии последовательных импульсов, идущих непрерывао, контролировать появление в определенный момент времени каждого импульса и, при отсутствии хотя бы одного из них, выдавать сигналы неисправности .

Недостатком данного устройства является небольшие функциональные возможности, заключающиеся в том, что контроль импульсов некоторого одноканапьног-о устройства требует дополнительных импульсов синхронизации.

Наибопее близким по технической сущности к предлагаемому является устройство Дпя контроля последоватепьности импульсов, состоящее из триггеров, образу- ЧАСТОТЫ

ющих регистр сдвига, входных логических эпементов, соединяющих триггеры между собой и управляемых сигнапами контролируемой последоватегшности, и блока сравнения 2J.

Недостаток известного устройства закшочается в том, что оно обнару:«ивает только одиночные ошибки в контролируемой последовательности импульсов, появ10ление кратных ошибок им не обнаруживается.

Цепь изобретения - повышение достоверности контроля.

Поставленная цепь достигается тем,

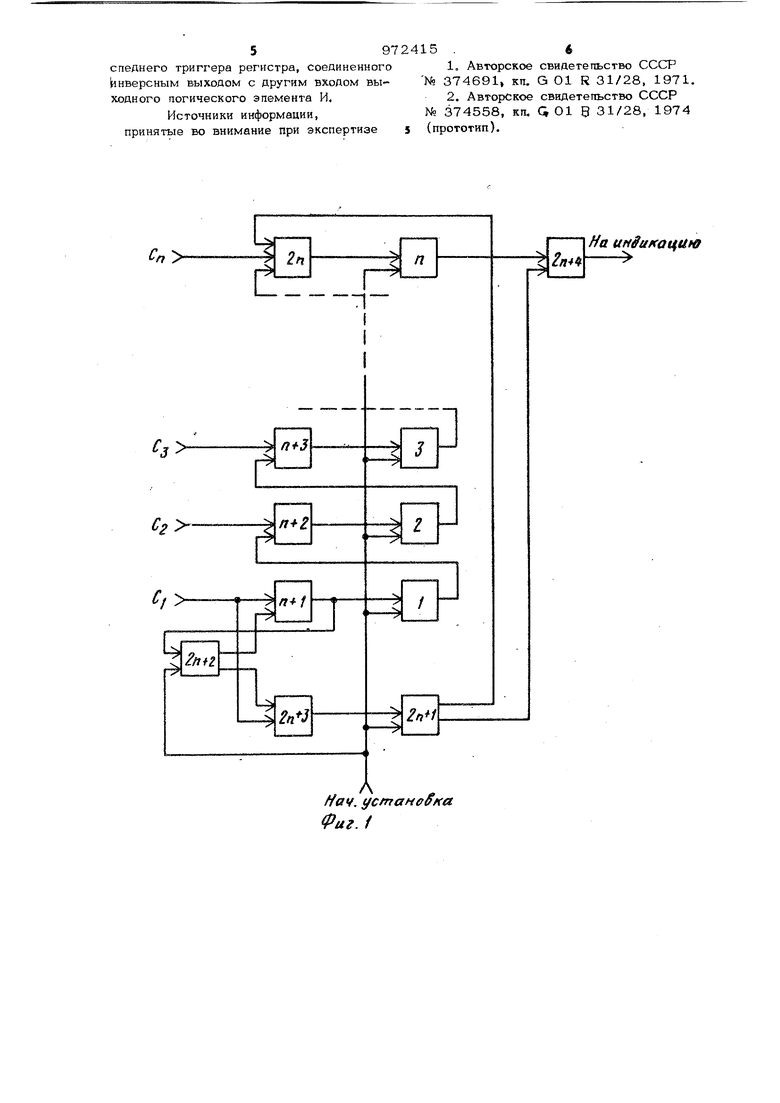

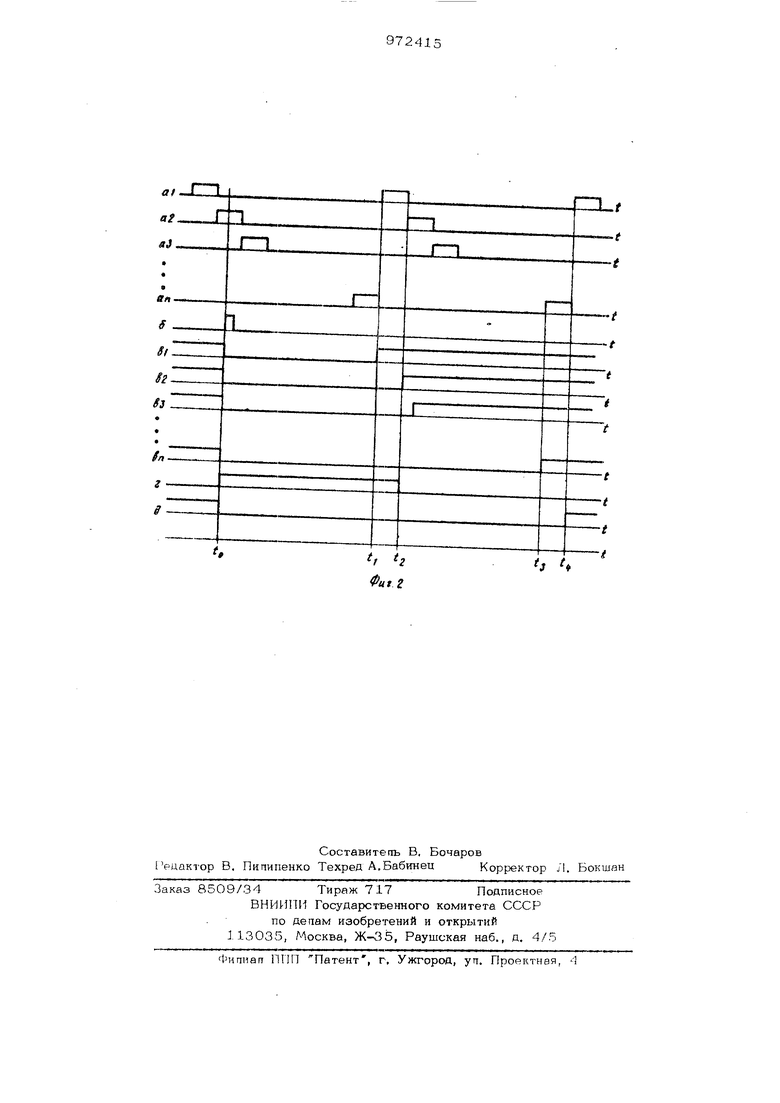

15 что в устройстве, содержащем триггеры, соединенныеМежду собой через входные логические элементы И в блок регистров сдвига, и выходной элемент И, число триггеров блока регистров сдвига уве20личено До числа колтролируемых каналов и в устройство введены триггер пере- кшочения, дополнительный логический элемент И и дополнительный триггер, причем вход триггера перекточения соединен с аыходом первого входного погичвского эпемеита И, а его выходы соединены с управпяюшими входами первого входного логического элемента И и дополнительного входного погического элемента И, основные входы которых подключены к первому входу бпока контроля, выход послед него соединен с входами дополнительного триггера, выходы которого соединены с входами выходного логического элемента И и входного логического элемента И посггеднего триггера регистра, соединенно го инверсным выходом с другим выходом выходного логического элемента И. На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - временнь е диаграммы. Устройство содержит триггеры 1, 3, .., у, образующие регистр сдвига, входные логические элементы И И+1, , ..,, 2к| на которые поступают вход ,цые сигнапы С, , допопнитепь 1ГЫЙ триггер 2ю + 1, триггер переключения 2ц+2, дополнительный входной логический эпемент И 2И+3, выходной логический элемент И 2п+4. Устройство работает следующим образом. Сигнал начальной установки (фиг. 26) устанавливает все триггеры в исходное положение, это происходит в произволь11ЫЙ момент времении -Ьд. В момент времени -Ьх| I когда появляется импульс С (фиг, 2,а) на первом входе устройства триггера 1 (фиг. 2,в.) переходит в сост яние 1, разрешая тем самым прохождение импульса С-х через входной логичес кий элемент И И+2 на вход триггера 2 По заднему фронту импульса С триггер переключения 2У1 + 2 переходит в состояние О (фиг. 2г). В момент времени -Ьл появляется сигнал С (фиг. 2,а.2) на втором входе уст ройства и переводит триггер 2 в состояние (фиг. 2,Вл), что разрешит прохоящение импульса С, через входной логический элемент И И+3 на вход триггера 3 и так далее (входные сигналы С, ..., С j показаны на фиг. 2,а,..., flj, а состояние триггеров 3, ..., i - на фиг. 2в 3, ..., вп). Если в контролируемой последовательности импупьсов не было пропусков или 1 зменения в порядке следования, то к моменту времени -t когда появится очередной импупьс С на первом входе устройстшэ, последний триггер регистра У) будет находиться в состоянии 1, а дополнительный триггер в момент, времени t перейдет в состояние 1° (фиг. 2(:, так как триггер переключения 2|а+2 пропустит импульс через дополнительный входной логический элемент И 2h+3 на вход дошэгшительного триггера 2п+1. Последний сигналом со своего инверсного выхода закроет входной логический элемент И 2j последнего триггера и регистра, а также подает сигнал логической на один из входов выходного эпемента И 2.+4, ко второму входу которого подключен инверсный выход триггера И. Отсутствие сигнала логической 1 на выходе выходного элемента И 2vi+4 свидетепьствует об отсутствии нарушений в контролируемой последовательности импульсов. После момента времени -Ь. входные сигналы уже не смогут изменить состояние триггера у которое и определяет результат контроля. Таким образом, контроль выполняется в течение только одного периода контролируемой последовательности импульсов (с момента времени -Ь- по -Ь ). Предлагаемое устройство позволяет быстро обнаружить неисправный блок системы управления преобразователем. Формула изобретения Устройство Для контроля схем управления тиристорными преобразователями частоты, содержащее триггеры, соединенные между собой через входные логические элементы И в блок регистров сдвига, и выходной элемент И, отличающее с я тем, что, с целью повышения достоверности контроля, число триггеров блока регистров сдвига увеличено До числа контролируемых каналов,в устройство введены триггер переключения, дополнительный входной логический эпемент И и дополнительный триггер, причем вход триггера переключения соединен с выходом первого входного логического элемента И, а его выходы соединены с управляющими входами первого входного логического элемента И и допогтннтепьного входного логического элемента Н, основные входы которых подключены к первому входу блока контроля, выход поспеднего соединен с входом дополнитепьного триггера, выходы которого соединены с входами выходного погического элемента :И и входного логического эпеменга И по-

спеднего триггера регистра, соединенного |инверсным выходом с другим входом выходного погического элемента И.

Источники информации, принятые во внимание при экспертизе

1„ Авторское свидетельство СССР № 374691, кп. G 01 R 31/28, 1971.

2. Авторское свидетельство СССР № 374558, кп. Q О1 5 31/28, 1974 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования дискретного радиоканала | 1980 |

|

SU962999A1 |

| Устройство для сопряжения | 1982 |

|

SU1051526A1 |

| Устройство для контроля регистра сдвига | 1980 |

|

SU911530A1 |

| Устройство для контроля многоканальных систем управления тиристорными преобразователями | 1984 |

|

SU1177799A1 |

| Устройство для контроля логических схем | 1986 |

|

SU1365087A2 |

| Устройство контроля группы цифровых блоков | 1990 |

|

SU1798786A1 |

| СПОСОБ УПРАВЛЕНИЯ ЧАСТОТНЫМ АСИНХРОННЫМ ЭЛЕКТРОПРИВОДОМ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2081503C1 |

| Устройство для контроля лоических блоков | 1986 |

|

SU1453409A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1983 |

|

SU1157544A1 |

| Устройство для диагностирования систем импульсно-фазового управления тиристорным преобразователем | 1988 |

|

SU1598031A1 |

Нач, (/cmaHff /fa Фиг.1

Авторы

Даты

1982-11-07—Публикация

1980-10-03—Подача