А$сг

со

О5 О1

о

00

)

моследоиательнпсть гР(1рачивается в сигнатуру. В iipcMiecr.e контроля автоматически осуществляется пос.педова- те.г1Ы1ое уменьшение длительности измерительного импульса с одновременным сравнением сигнатур,сформированных в каждых двух соседних окнах

измерения. Значение дли гсчц. и измерительного импулы-я при несовпадении сигнатур дпух соседних окон измерения является временем задержки сигнала контролируемой логической схемы (измеренным динамическим параметром). 1 з.п. ф-лы, 5 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Сигнатурный анализатор | 1986 |

|

SU1388869A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1982 |

|

SU1140065A1 |

| Сигнатурный анализатор (его варианты) | 1984 |

|

SU1252784A1 |

| Устройство для контроля логических блоков | 1982 |

|

SU1105897A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1985 |

|

SU1302220A2 |

| Устройство для контроля однотипных логических узлов | 1984 |

|

SU1223233A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1987 |

|

SU1562864A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1120338A1 |

| Сигнатурный анализатор | 1985 |

|

SU1312576A2 |

| Сигнатурный анализатор | 1986 |

|

SU1383358A1 |

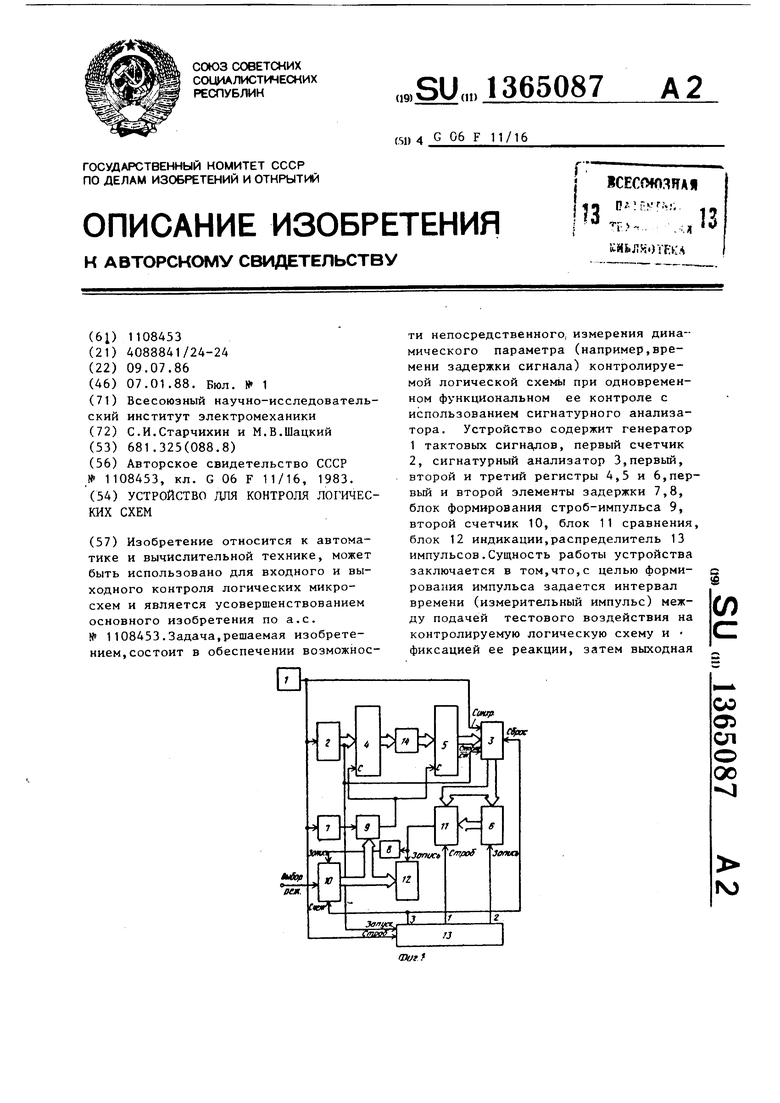

Изобретение относится к автоматике и вычислительной технике, может быть использовано для входного и выходного контроля логических микросхем и является усовершенствованием основного изобретения по а.с. № 1108453.Задача,решаемая изобретением, состоит в обеспечении возможности непосредственного, измерения динамического параметра (например,времени задержки сигнала) контролируемой логической схемь при одновременном функциональном ее контроле с использованием сигнатурного анализатора. Устройство содержит генератор 1 тактовых сигна юв, первый счетчик 2, сигнатурный анализатор 3,первый, второй и третий регистры 4,5 и 6,первый и второй злементы задержки 7,8, блок формирования строб-импульса 9, второй счетчик 10, блок 11 сравнения, блок 12 индикации,распределитель 13 импульсов.Сущность работы устройства заключается в том,что,с целью формирования импульса задается интервал времени (измерительный импульс) между подачей тестового воздействия на контролируемую логическую схему и фиксацией ее реакции, затем выходная сл

1

Изобретение относится к автоматике и вычислительной технике, может быть использовано,например, для входного и выходного контроля логических микросхем и является усовершенствованием известного устройства по авт.св. № 1108453.

Цель изобретения - повышение достоверности контроля за счет обеспечения измерения динамических параметров контролируемых логических схем.

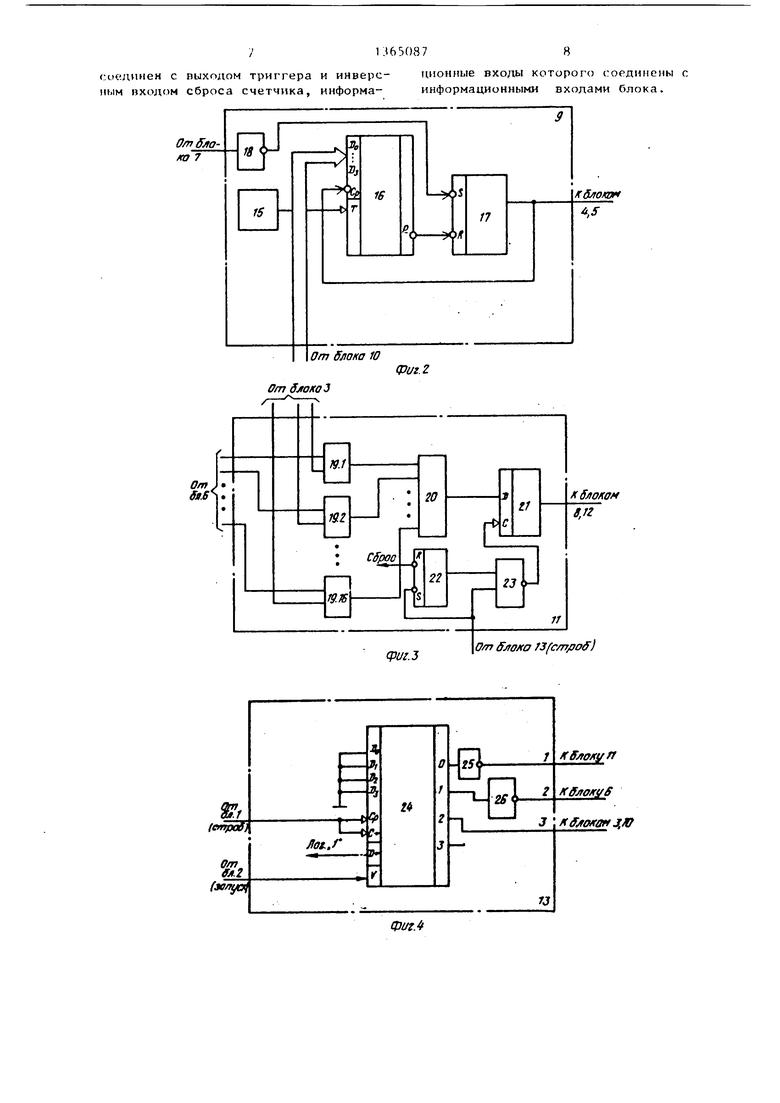

На фиг. 1 приведена функциональная схема устройства;на фиг. 2 - функциональная схема блока формирования стробирующего импульса; на фиг. 3 и А - блок сравнения и распределитель импульсов соответственно; на фиг. 5 - временные диаграммы, поясняющие работу устройства.

Устройство для контроля логических схем (фиг. 1) содержит генератор 1 тактовых сигналов (генератор тактов), первый счетчик 2, сигнатурный анализатор 3 первый А, второй 5 и третий 6 регистры первый 7 и второй 8 элементы задержки,блок 9 формирования стробирующего импульса,второй счетчик 10, блок 11 сравнения,блок 12 индикации, распределитель 13 импульсов. Также обозначена контролируемая схема 1А.

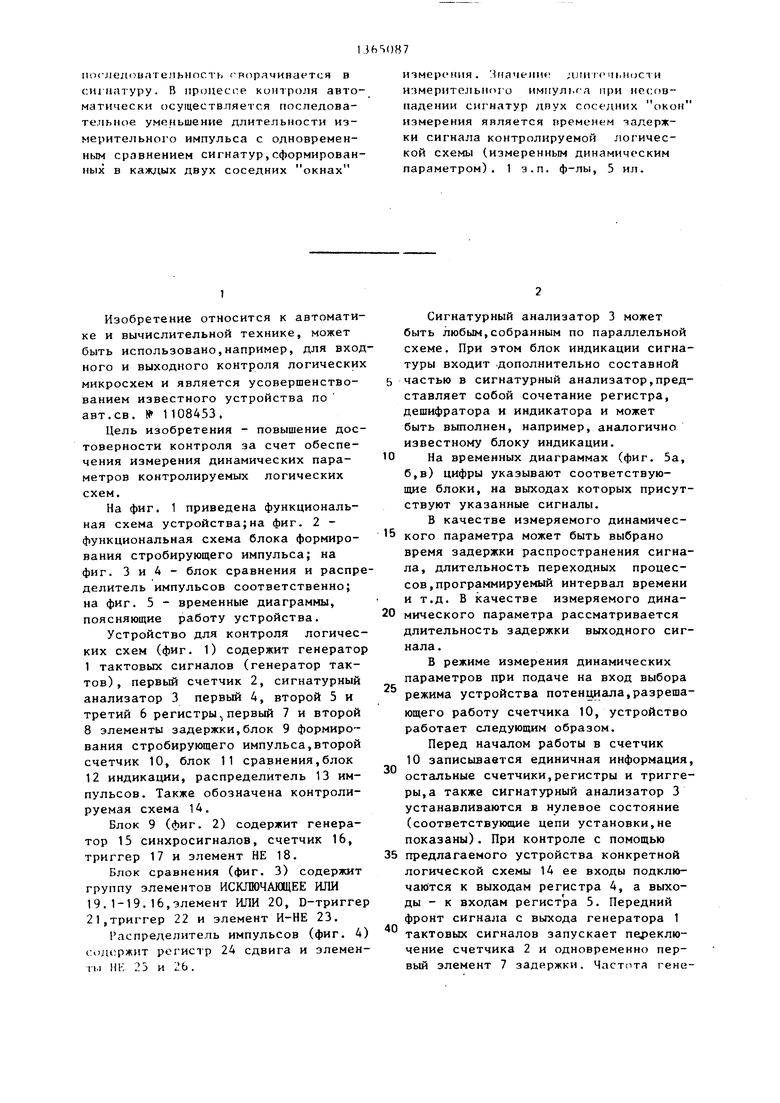

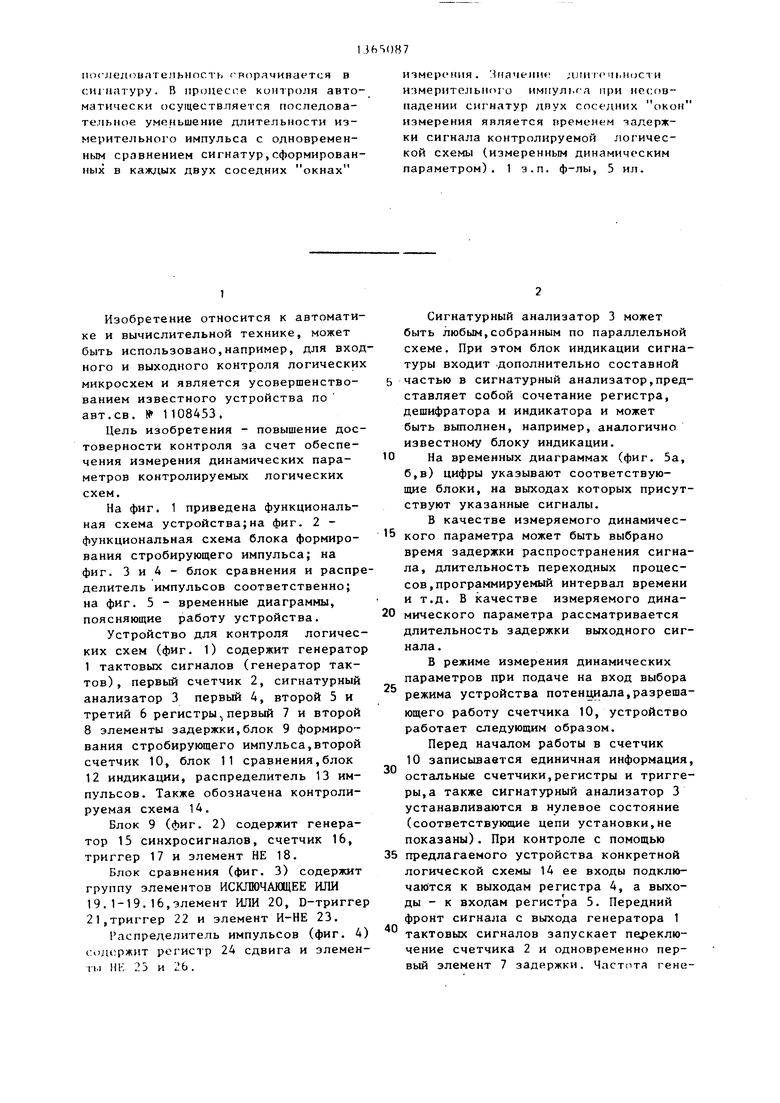

Блок 9 (фиг. 2) содержит генератор 15 синхросигналов, счетчик 16, триггер 17 и элемент НЕ 18.

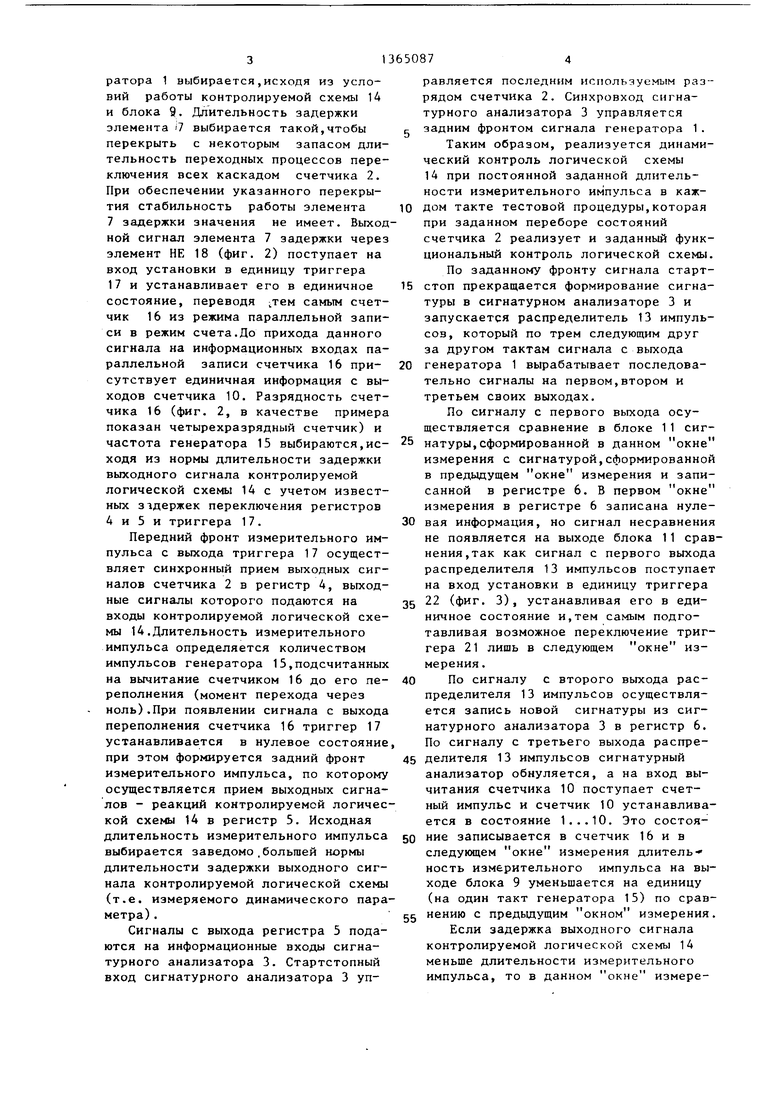

Блок сравнения (фиг. 3) содержит группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 19.1-19.16,элемент ИЛИ 20, D-триггер 21,триггер 22 и элемент И-НЕ 23.

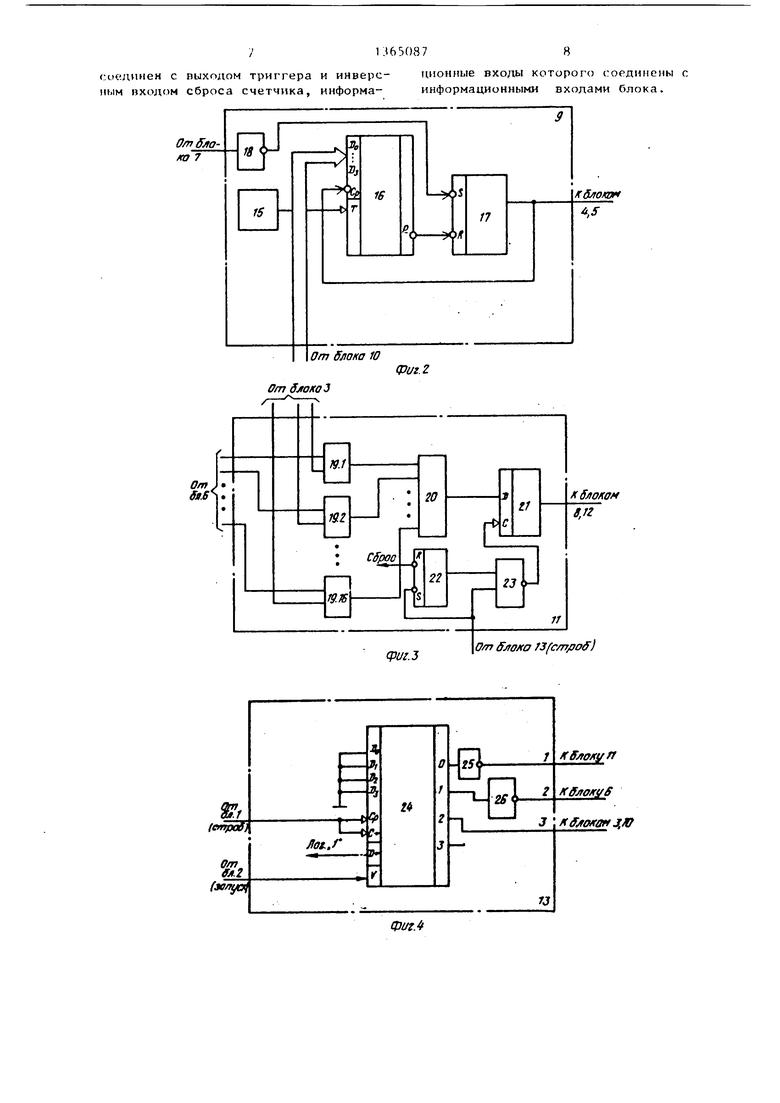

Распределитель импульсов (фиг. 4) счдсфжит регистр 24 сдвига и элемен- rt.i ПК 25 и 26.

Сигнатурный анализатор 3 может быть любым,собранным по параллельной схеме. При этом блок индикации сигнатуры входит |Дополнительно составной частью в сигнатурный анализатор,представляет собой сочетание регистра, дешифратора и индикатора и может быть вьтолнен, например, аналогично известному блоку индикации. 0 На временных диаграммах (фиг. 5а, б,в) цифры указывают соответствующие блоки, на выходах которых присутствуют указанные сигналы.

В качестве измеряемого динамичес- 5 кого параметра может быть выбрано время задержки распространения сигнала, длительность переходных процессов, программируемый интервал времени и т.д. В качестве измеряемого дина- 0 мического параметра рассматривается длительность задержки выходного сигнала .

В режиме измерения динамических параметров при подаче на вход выбора режима устройства потенциала,разрешающего работу счетчика 10, устройство работает следующим образом.

Перед началом работы в счетчик 10 записывается единичная информация, остальные счетчики,регистры и триггеры, а также сигнатурный ангшизатор 3 устанавливаются в нулевое состояние (соответствующие цепи установки,не показаны). При контроле с помощью 5 предлагаемого устройства конкретной логической схемы 14 ее входы подключаются к выходам регистра 4, а выходы - к входам регистра 5. Передний фронт сигнала с выхода генератора 1 тактовых сигналов запускает переключение счетчика 2 и одновременно первый элемент 7 задержки. Частота гене5

0

0

ратора 1 выбирается,исходя из условий работы контролируемой схемы 14 и блока 9. Длительность задержки элемента П выбирается такой,чтобы перекрыть с некоторым запасом длительность переходных процессов переключения всех каскадом счетчика 2. При обеспечении указанного перекрытия стабильность работы элемента 7 задержки значения не имеет. Выходной сигнал элемента 7 задержки через элемент НЕ 18 (фиг. 2) поступает на вход установки в единицу триггера 17 и устанавливает его в единичное состояние, переводя тем самым счетчик 16 из режима параллельной записи в режим счета.До прихода данного сигнала на информационных входах параллельной записи счетчика 16 присутствует единичная информация с выходов счетчика 10. Разрядность счетчика 16 (фиг. 2, в качестве примера показан четырехразрядный счетчик) и частота генератора 15 выбираются,исходя из нормы длительности задержки выходного сигнала контролируемой логической схемы 14 с учетом известных задержек переключения регистров 4 и 5 и триггера 17.

Передний фронт измерительного импульса с выхода триггера 17 осуществляет синхронный прием выходных сигналов счетчика 2 в регистр 4, выходные сигналы которого подаются на входы контролируемой логической схемы 14.Длительность измерительного импульса определяется количеством импульсов генератора 15,подсчитанных на вычитание счетчиком 16 до его переполнения (момент перехода через ноль).При появлении сигнала с выхода переполнения счетчика 16 триггер 17 устанавливается в нулевое состояние при этом формируется задний фронт измерительного импульса, по которому осуществляется прием выходных сигналов - реакций контролируемой логической схемы 14 в регистр 5. Исходная длительность измерительного импульса выбирается заведомо .большей нормы длительности задержки выходного сигнала контролируемой логической схемы (т.е. измеряемого динамического параметра) .

Сигналы с выхода регистра 5 подаются на информационные входы сигнатурного анализатора 3. Стартстопный вход сигнатурного анализатора 3 управляется последним используемым раз-рядом счетчика 2. Синхровход сигнатурного анализатора 3 управляется

задним фронтом сигнала генератора 1.

Таким образом, реализуется динамический контроль логической схемы 14 при постоянной заданно длительности измерительного импульса в каж- дом такте тестовой процедуры,которая при заданном переборе состояний счетчика 2 реализует и заданный функциональный контроль логической схемы. По заданному фронту сигнала стартстоп прекращается формирование сигнатуры в сигнатурном анализаторе 3 и запускается распределитель 13 импульсов, который по трем следующим друг за другом тактам сигнала с выхода генератора 1 вырабатывает последовательно сигналы на первом,втором и третьем своих выходах.

По сигналу с первого выхода осуществляется сравнение в блоке 11 сигнатуры,сформированной в данном окне измерения с сигнатурой,сформированной в предыдущем окне измерения и записанной в регистре 6. В первом окне измерения в регистре 6 записана нулевая информация, но сигнал несравнения не появляется на выходе блока 11 сравнения, так как сигнал с первого выхода распределителя 13 импульсов поступает на вход установки в единицу триггера

22 (фиг. 3), устанавливая его в единичное состояние и,тем самым подготавливая возможное переключение триггера 21 лишь в следующем окне измерения.

По сигналу с второго выхода распределителя 13 импульсов осуществляется запись новой сигнатуры из сигнатурного анализатора 3 в регистр 6. По сигналу с третьего выхода распределителя 13 импульсов сигнатурный анализатор обнуляется, а на вход вычитания счетчика 10 поступает счетный импульс и счетчик 10 устанавливается в состояние 1...10. Это состояние записывается в счетчик 16 и в следующем окне измерения длитель- ность измерительного импульса на выходе блока 9 уменьшается на единицу (на один такт генератора 15) по сравнению с предыдущим окном измерения.

Если задержка выходного сигнала контролируемой логической схемы 14 меньше длительности измерительного импульса, то в данном окне измерения формируется правильная сигнатура, совпадающая с сигнатурой,сформированной в предыдущем окне измерения, и весь процесс повторяется.

Таким образом, в следующих друг за другом окнах измерения осуществляется постепенное уменьшение длительности измерительного импульса, пока в одном из окон измерения зта длительность не оказывается меньшей фактического значения задержки выходного сигнала контролируемой логической схемы 14. В этом случае в регистр 5 с выхода схемы 14 принята неверная выходная реакция и в результате в сигнатурном анализаторе формируется неверная сигнатура, отличная от той, которая записана в регистре 6. На одном или нескольких выходах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 19.1-19.16 (фиг. 3) при этом появляется единичный сигнал, который вызывает появление единичного сигна- ла на выходе элемента ИЛИ 20. По сигналу с первого выхода распределителя 13 импульсов после окончания окна измерения потенциал логической 1 записывается в триггер 21, с выхода которого поступает на вход записи блока 12 индикации. В блок индикации при этом записывается текущее состояние счетчика 10, которое однозначно определяет измеренную величину задержки выходного сигнала схемы 14.

Сигнал о несовпадении сигнатур с выхода блока 11 сравнения, кроме того,через элемент 8 задержки поступает на вход параллельной записи счетчика 10 и устанавливает его в единичное состояние, после чего весь цикл контроля и измерения повторяется вновь.

Для обеспечения только функционального контроля логических схем на вход выбора режима устройства поается запрещающий потенциал. При этом длительность измерительного импульса в соседних окнах измерения не изменяется.

Таким образом, введение указанных элементов и связей обеспечивает по сравнению с известным устройством возможность не только допускового контроля, но и непосредственного измерения динамических параметров, благодаря чему увеличивается полнота контроля. При этом функциональный

0

5

0

5

0

контроль логических схем осуществляется, как и в известном устройстве, путем сравнения сигнатуры контролируемой схемы с эталонной сигнатурой.

Формула изобретения

I

с входом управления вычитания счетчика, инверсный выход заема которого с соединен с инверсным входом сброса триггера, инверсный вход установки которого соединен с выходом элемента НЕ, вход которого соединен с входом разрешения блока, выход которого

5

0

0

0/nffjfo- т 7

7}J

От блока Ю

От длокаЗ

16

K&noKOft

,f

к блока ft

риг.З

Ofn f/rOAO fSfC/npOff)

S)

Фиг.

| Устройство для функционально-динамического контроля логических схем | 1983 |

|

SU1108453A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-01-07—Публикация

1986-07-09—Подача