(54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ЗАПИСЬЮ ИНФОРМАЦИИ В БЛОК ПАМЯТИ

Изобретение относится к вычислительной технике, в частности к устройствам управления записью информации в запоминающие блоки.

Известно устройство для управления записью информации в запоминающие блоки, содержащее буферные накопители, оперативные запоминающие устройства (ЗУ), процессор, блок анализа информации 1.

Недостатком этого устройства управления является то, что оно не позволяет осуществлять ввод в систему информации на накопитель на магнитной ленте (НМЛ) процессора и оперативных ( ЗУ, входящих в состав ЭВМ, что снижает производительность системы. -

Наиболее близким к изобретению является устройство управления, содержащее, блок анализа информации, два буферных накопителя, каждый из которых состоит из вентиля отсчетов, синхронного ЗУ, мультивибратора, триггер, стартстопный накопитель, блок вентилей записи и считывания, синхронизатор, при этом выходы блока анализа информации соединены с входами двух буферных накопителей через вентили записи, а выходы буферных накопи

2

телей соединены с входами вентилей считывания, выходы которых соединены с входом стартстопного накопителя, другой вход которого подключен к выходу мультивибратора 2.

Недостатком известного устройства является то, что око не обеспечивает запись информации, поступающей от двух источников. При необхо10ДИ.МОСТИ записи информации от двух независимых источников требуется использовать два подобных устройства. В этом случае значительно усложняется время обработки за счет необходимости совмещения двух информационных массивов в порядке поступления групп (сообщений).

Целью изобретения является сокра-; щение оборудования при записи :инфор20мации и повышение быстродействия устройства.

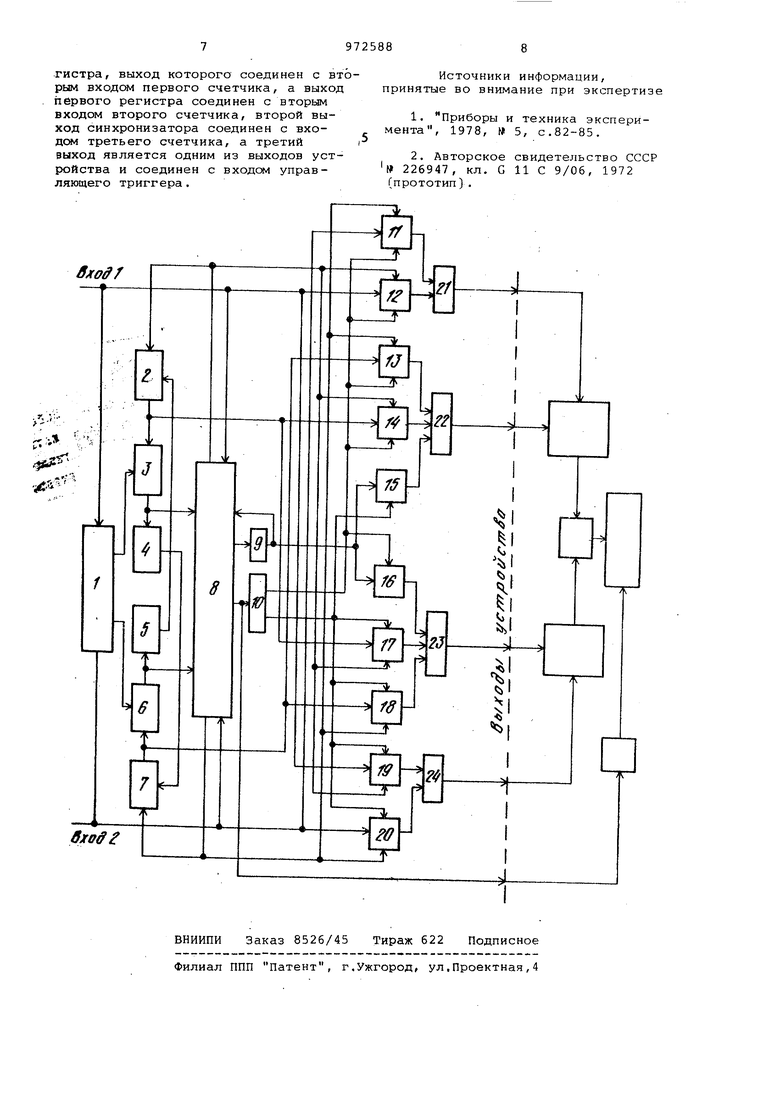

Поставленная цель достигается тем, что устройство для управления записью информации в блок памяти, содержащее 25 блок анализа входной информации, синхронизатор, управлямщий триггер, содержит три счетчика, два сумматора, два регистра, десять элементов И, четыре элемента ИЛИ, при этом выходы 30 четырех элементов ИЛИ являются выходами устройства, а первые и вторые входы первого и четвертого элементов ИЛИ соответственно соединены о выходами первого и второго, девятог и десятого элементов И, а первые вторые и третьи входы второго и тре его элемента ИЛИ соответственно сое динены с выходами третьего- четверто го и пятого элементов И и с выходами шестого, седьмого и восьмого эле ментов И, первый вход первого элемента И соединен с первым входом третьего, с третьим входом восьмого и с третьим входом десятого элементов И, второй вход .- с вторым входом десятого элемента И, являющегося вторым входом устройства, с третьим входом синхронизатора и с вторым входом блока анализа входной информации, а,, третий вход - с треть ми входами второго третьего и че,твертого элемента И, с первым входом блока режима, первый вход второго элемента И соединен с первым входом первого счетчика, первым выходом синхронизатора, первым входом четве того,третьими входами седьмого и девятого элементов И, второй вход является вторым вхйдсм устройства и соединен с первым входом блока анализа входной информации, первым входом синхронизатора с вторым входом девятого элемента И, второй вход третьего элемента И соединен с выходом второго счетчика, с первы входом второго сумматора и вторым входом восьмого элемента И, второй вход четвертого элемента И соединен с выходом первого счетчика, первым входом первого сумматора и с вторым входом седьмого элемента И, первый вход пятого элемента И соединен с выходом третьего счетчика, с вторым входом синхронизатора и вторым входом шестого элемента И, а второй вход - с вторым выходом упра ляющего триггера и с первыми входами седьмого, восьмого, девятого и д сятого элементов И, первый и второй выходы блока анализа входной информации соединены соответственно с вторыми входами первого и второго сумматоров, выход первого сумматора соединен с пятым входом син ронизатора и входсм первого регистра, а выход второго сумматора с/ четвертым входсм синхронизатора и1 входом второго регистра, выход которого соединен с вторым входом первого счетчика, а выход первого регистра соединен с вторым входом второго счетчика, второй выход синхронизатора соединен с входсм тр тьего счетчика, а третий выход явля ется одним из.выходов устройства и соединен с входом управляющего триг гера. На чертеже представлена структурная схема устройства. Устройств содержит блок 1 анализа входной информации, первый счетчик 2, первый (Сумматор 3, первый регистр 4, второй регистр 5, второй сумматор б, второй счетчик 7, синхронизатор 8, третий счетчик 9, управляющий триггер 10, десять элементов и 11-20, четыре элемента ИЛИ 21-24. Устройство работает следующим образом . При поступлении информационного сообщения на первый вход блока 1 анализа входной информации из первого слова сообщения выделяется код количества слов, который поступает на второй вход первого cyMiviaTopa 3. На первый вход этого сумматора поступает код последнего адреса записи предыдущего сообщения, находящийся в первом счетчике 2. Результат суммирования записывается в первый регистр 4. Таким образом, в первом регистре 4 хранится последний адрес записи данного сообщения. В синхронизаторе 8 из импульсов сообщения фор- ируются синхроимпульсы, поступающие на второй четвертый, седьмой и девятый элементы И 12,14,17 и 19. В зависимости от состояния управляющего триггера 10 открывается второй элемент И 12 и информация через первый элемент ИЛИ 21 поступает на соответствующий выход устройства, или девятый элемент И 19 и информация через четвертый элемент ИЛИ 24 поступает на соответствующий выход устройства. Адрес для записи информации поступает с выхода первого счетчика 2 на второй вход четвертого элемента И 14 и через второй элемент ИЛИ 22 на соответствующий выход устройства или через седьмой элемент И 17, третий элемент ИЛИ 23 на соответствукадий выход устройства. После записи инфор 1ационного сжэва содержимое первого счетчика 2 увеличи;вается на единицу. При поступлении .информации на вто- рой вход, код количества слов, выделенный из сообщения, поступает на второй вход второго сумматора б, а код последнего адреса записи предыдущего сообщения, поступившего с первого входа, из первого регистра 4 переписывается во второй счетчик 7, затем на втором сумматоре 6 суммируется с кодсм количества слов. Полученный, таким образом последний ад- рее записи, записывается во второй регистр 5.Из синхронизатора 8 сформированные синхроимпульсы поступают на соответствующие входы первого, ,третьего, восьмого и десятого элетлентов И,11, 13,18 и 20. в зависимости от состояния управ ляющего триггера 10 информация поступает через первый элемент И 11, первы1Й элемент ИЛИ 21 на соответств 1ДИЙ выход устройства, а адрес с вык да второго счетчика 7 через третий элемент И 13, второй элемент ИЛИ 22 поступает также на соответствующий выход устройства. Если информация в зависимости от -состояния управлянхцего триггера 10 поступает на вход десятого элемента И 20, то через четвертый элэпент ИЛИ 24 она выдается на соот ветствующий выход устройства, а адрес в этом случае с выхода второго счетчика 7 через восьмой элемент И 18, третий элемент ИЛИ 23 выдается на соответствующий выход устройства. После записи каждого информационного слова содержимое второго счетчика 7 также увеличивается на единицу. При одновременном поступлении информации по входам 1 и 2 в синхро низаторе формируются две серии импульсов, сдвинутых относительно друг друга на половину перио;, а запись информации производится поочередно от каждого входа, соответственно происходит и переключение первого и второго 2 и 7 адресов записи. Коды суммы с выходов первог и второго сумматоров 3 и 6 поступаю на входы синхронизатора 1 для определения окончания записи в ЗУ .Если результат на выходе первого или вто рого сумматоров 3 и 6 окажется боль ше объема ЗУ, то синхронизатор 1 вырабатываем импульс для запуска соответствующего ЗУ, который также поступает и.на вход управляницего тр гера 10, обеспечивающего подключени свободного ЗУ, на запись, а заполненного ЗУ -1на считывание. При считывании информации из синхронизатора 8 на вход третьего счетчика 9 подаются импульсы считывания. С выхода третьего счетчика 9 адрес считывания или через пятый элемент И 15, второй элемент ИЛИ 22 или через шестой элемент И 16, третий элемент ИЛИ 23 поступает на соответствующий выход устройства Одновременно сигнал с выхода третье го счетчика 9 поступает на второй вход синхронизатора 8 для определения окончания считывания. Предлагаемое устройство позволяе производить запись информации, пост пающей от двух независимых источников информации, при этом резко сокращается объем оборудования и увели чивается его быстродействие. Формула изобретения Устройство для управления записью информации в блок- памяти, содержащее блок анализа входной информации, синхронизатор, управляющий триггер, отличающееся тем, что, с целью сокращения оборудования при записи информации и повышения быстродействия устройства, оно содержит три счетчика, два сумматора,два регистра, десять элементов И, четыре элемента ИЛИ, при зтсм выходы четырех элементов ИЛИ являются выходами устройства, а первые и вторые входы первого и четвертого элементов ИЛИ соответственно соединены с выходами первого и второго, девятого и десятого элементов И, а первые, вторые и третьи входы второго и третьего элементов ИЛИ соответственно соединены с выходами третьего, четвертого и пятого элементов И и с выходами шестого, седьмого и восьмого элементов И, первый вход первого элемента Н соединен с первым входом третьего, с третьи: 1 входом восьмого и с третьим входсм десятого элементов И, второй вход - с вторым входо 1 десятого элемента И, являющегося вторым входом устройства, с третьим входомсинхронизатора и с вторым входом блока анализа входной информации, а третий вход - с третьими входами второго, третьего и четвертого элементов И, с первым выходом блока режима, первый вход второго эле;- ента И соединен с первым входом первого счетчика, первым выходом синхронизатора, первым входся четвертого, третьими входами седьмого и девятого элементов И, второй вход является первым входсм устройства и соединен с первым входом блока анализа входной информации, первым входом синхронизатора и с вторым входом девятого элемента И, второй вход третьего элемента И соединен с выходом второго счетчика, с первьом входом второго сумматора и вторым входом восьмого элемента и, второй вход четвертого элемента И соединен с выходом первого счетчика, первым входом первого ciTviMaTopa и с вторым входся седьмого элемента И, первый вход пятого элемента И соединен с выходом третьего счетчика, с вторым входом синхроннзатор а и с вторь шестого элемента И, а второй вход с вторы 1 выходам управляющего триГ гера и с первыми входами седьмого, восьмого, девятого и десятого элементой И, первый и второй выходы блока анализа входной информации соединены соответственно с вторгл и входа,ми первого и второго сумматоров, выход первого сумматора соединен с пятым входом синхронизатора и входом первого регистра, а выход второго сумматора . с четвертьрл входом синхронизатора и входом второго ре

| название | год | авторы | номер документа |

|---|---|---|---|

| Система записи и воспроизведения видеосигнала | 1990 |

|

SU1783635A1 |

| Устройство для формирования информации на телевизионном индикаторе | 1981 |

|

SU1075298A1 |

| Устройство для отображения информации | 1986 |

|

SU1367037A1 |

| Вычислительное устройство для диагностики состояния больных | 1990 |

|

SU1725229A1 |

| Процессор быстрого преобразования Фурье | 1982 |

|

SU1086438A1 |

| УСТРОЙСТВО ДЛЯ ВЫЗОВА ПОДПРОГРАММ | 1990 |

|

RU2009538C1 |

| Устройство для контроля и регулирования параметров | 1984 |

|

SU1249491A1 |

| Подсистема определения дальности доплеровского радиопеленгатора | 1990 |

|

SU1797083A1 |

| Устройство для деления в системе остаточных классов | 1983 |

|

SU1141400A1 |

| Запоминающее устройство | 1978 |

|

SU898502A1 |

Авторы

Даты

1982-11-07—Публикация

1980-11-24—Подача