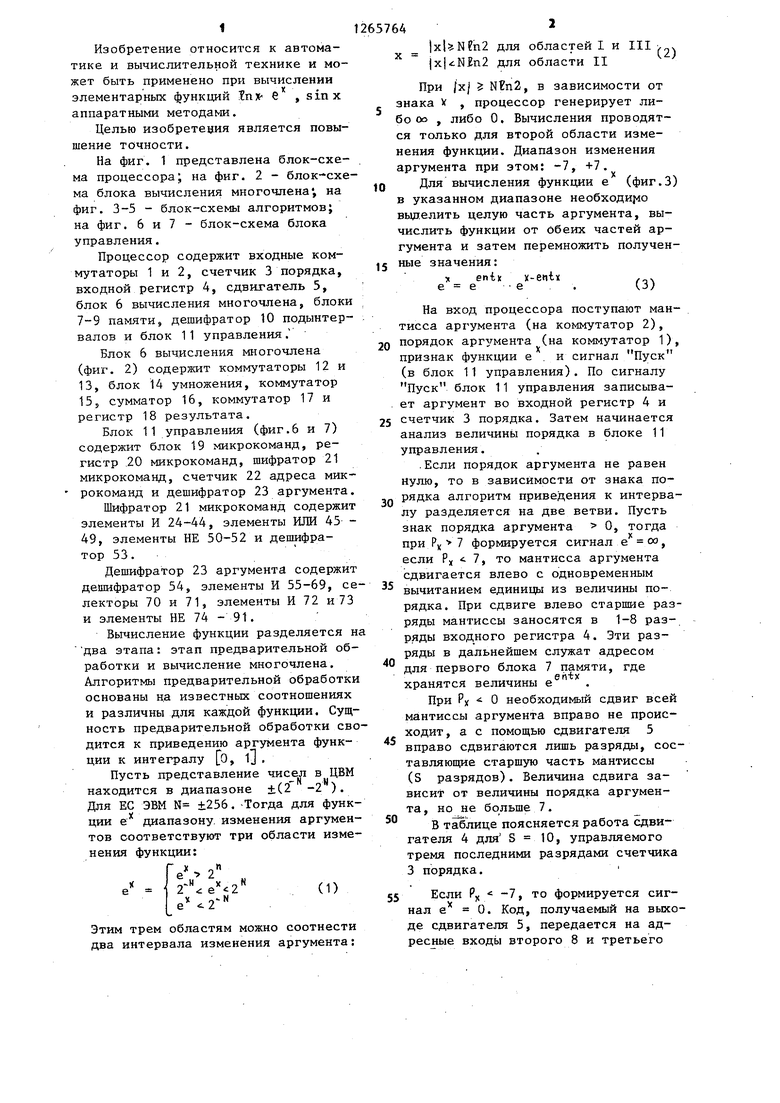

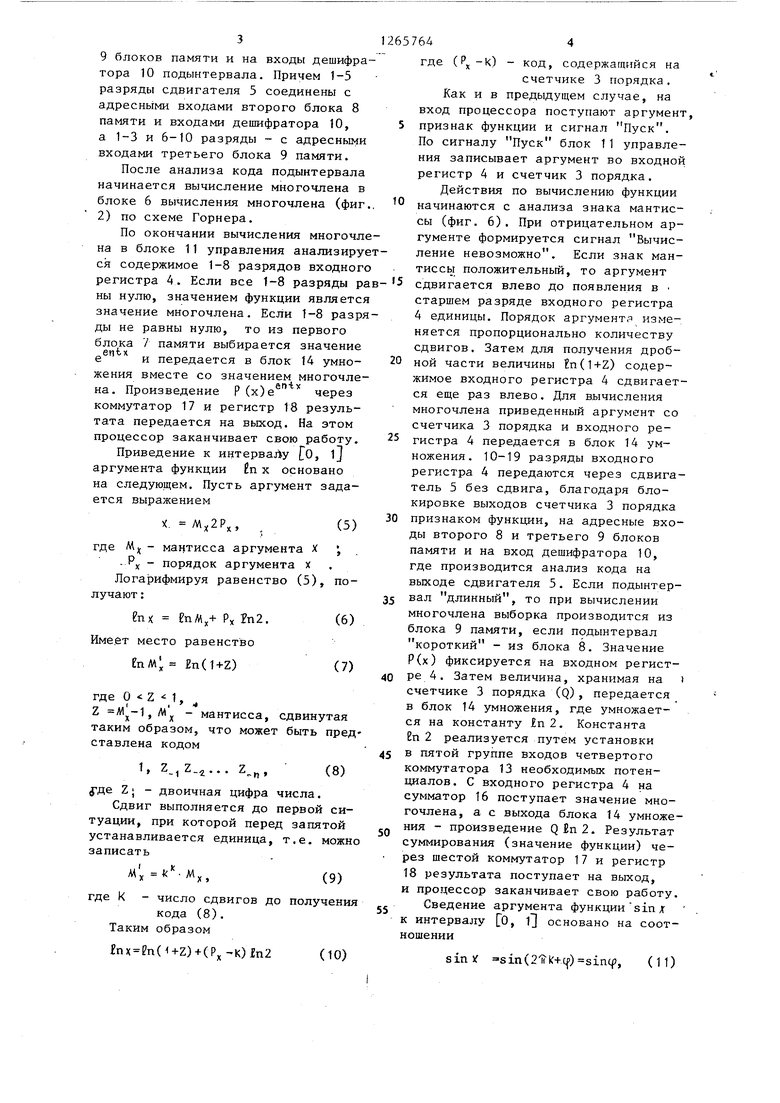

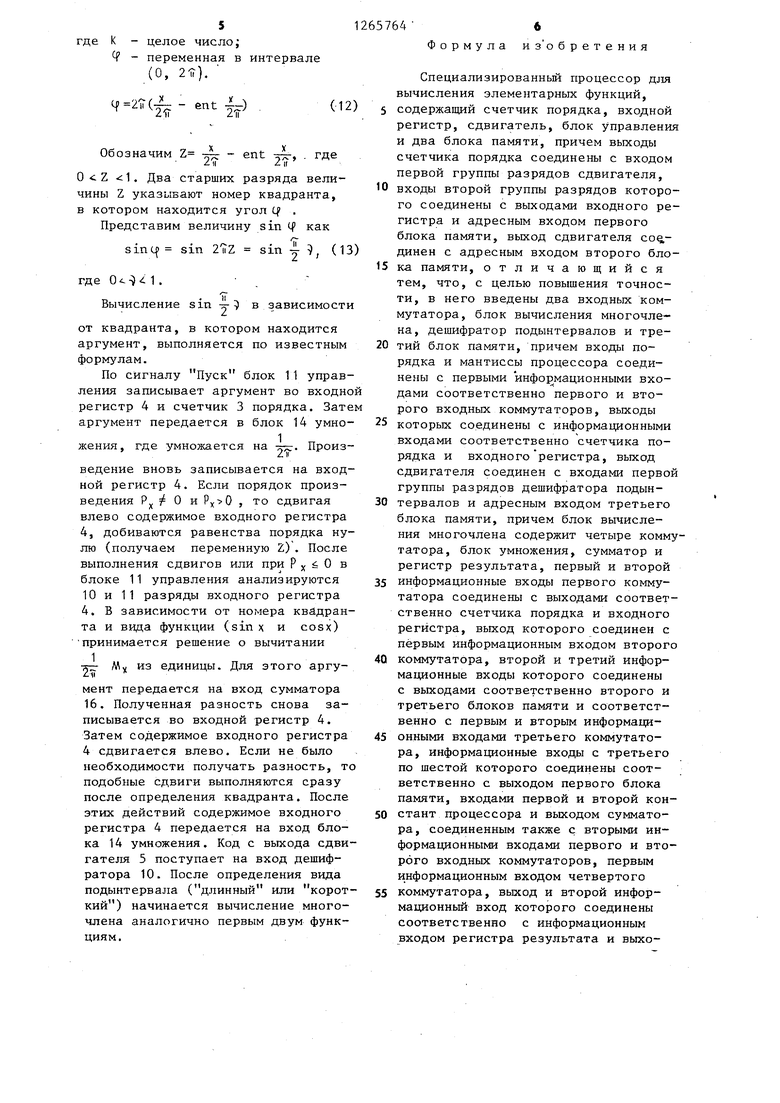

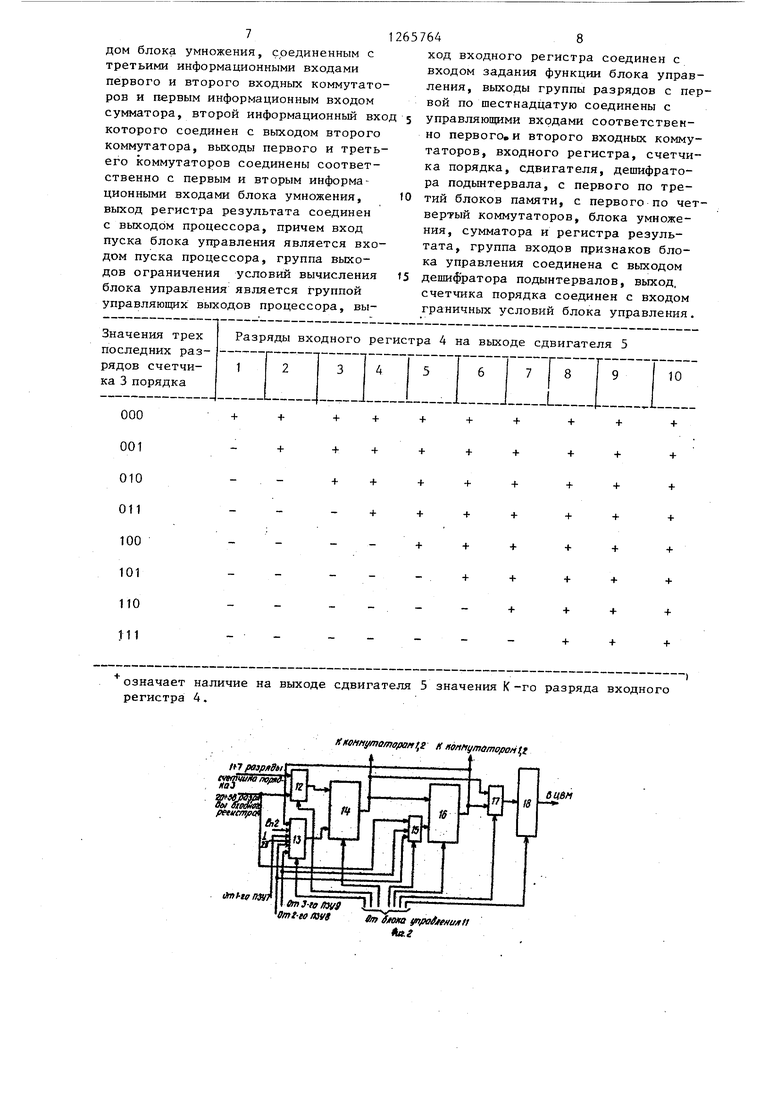

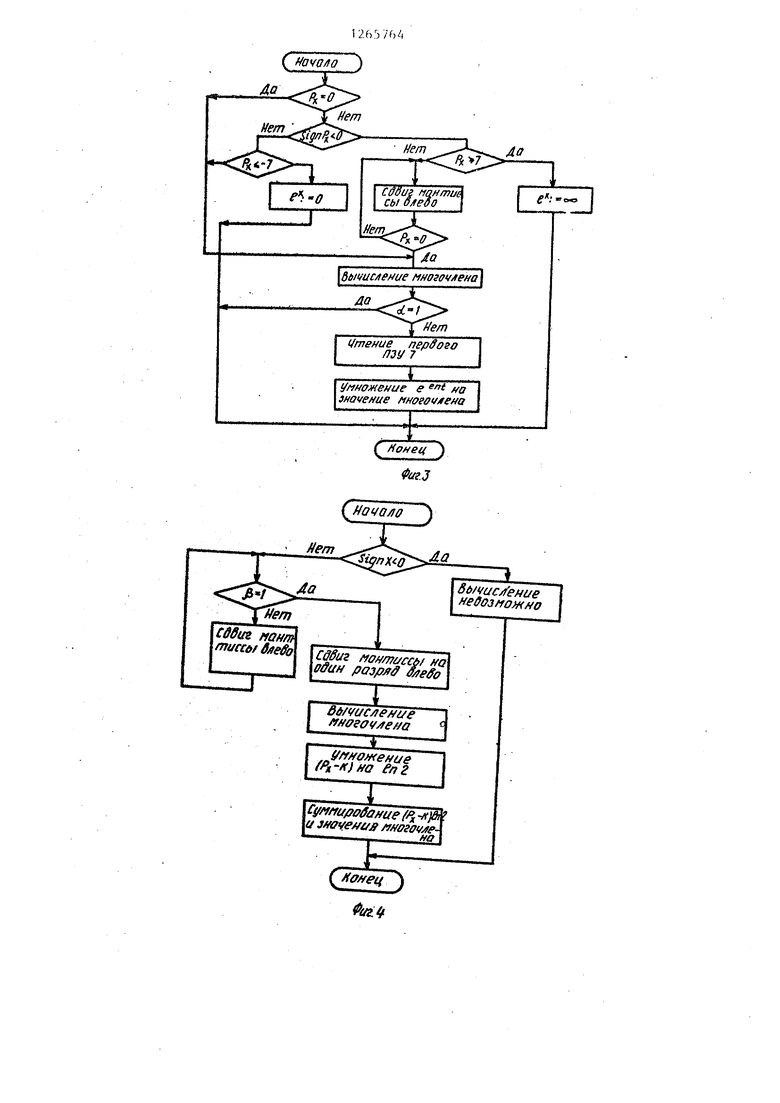

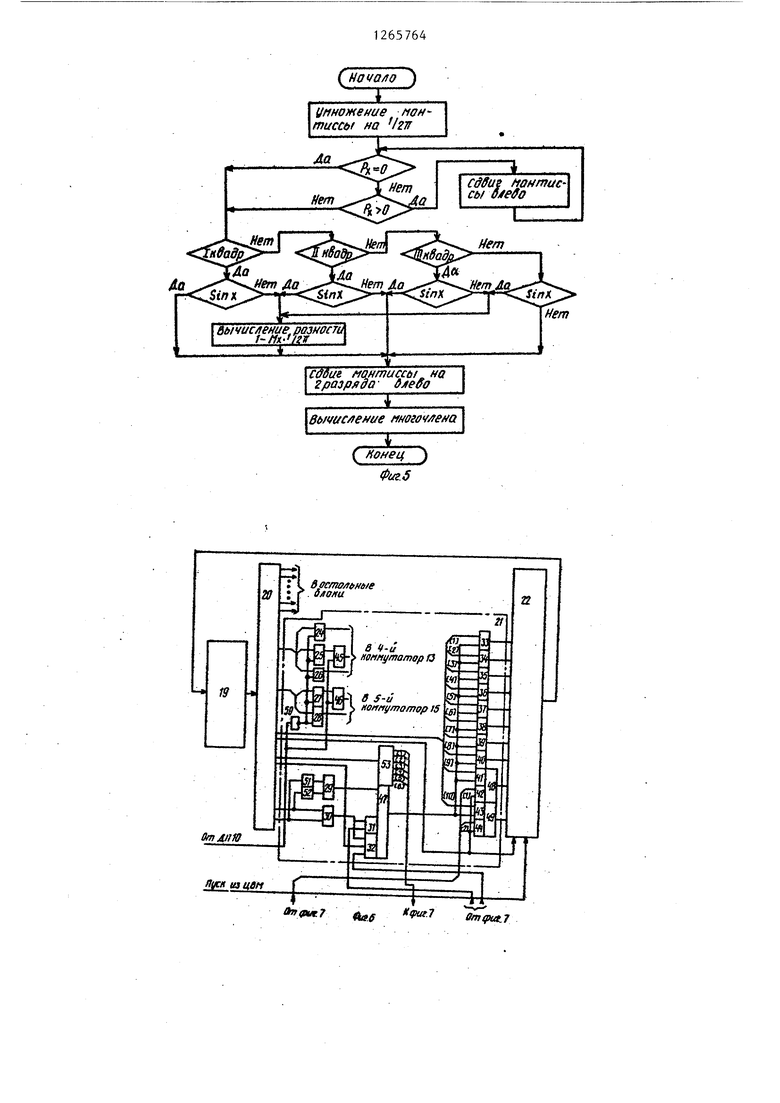

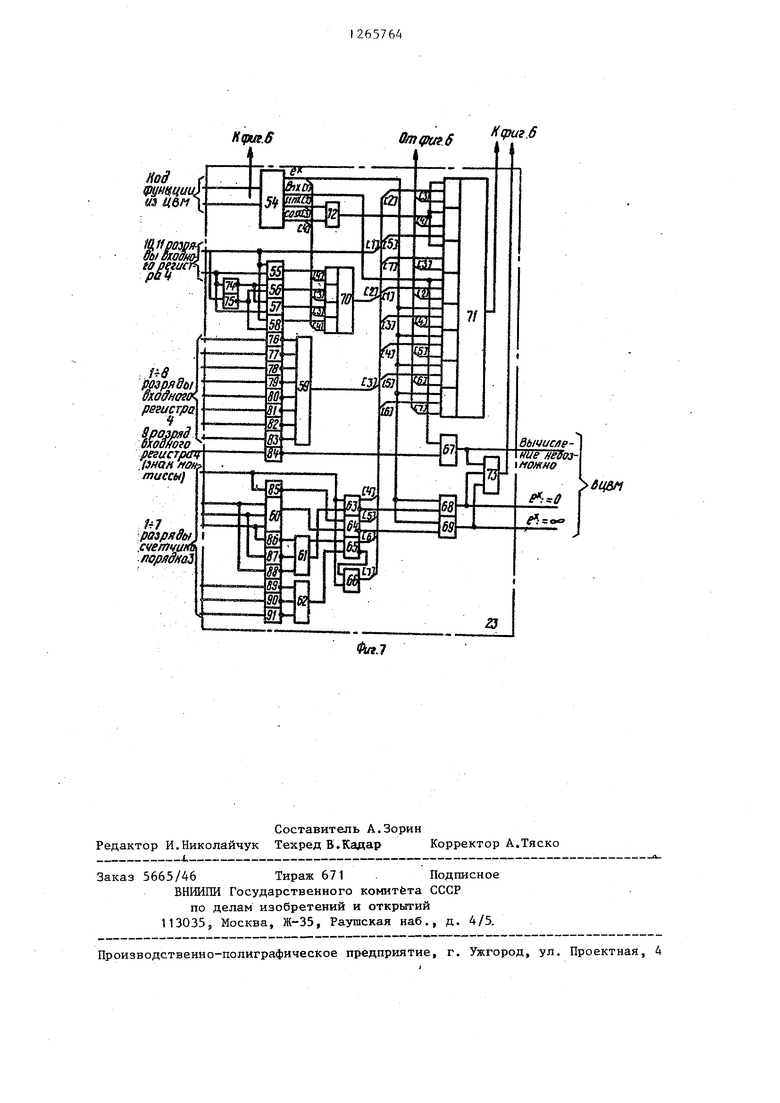

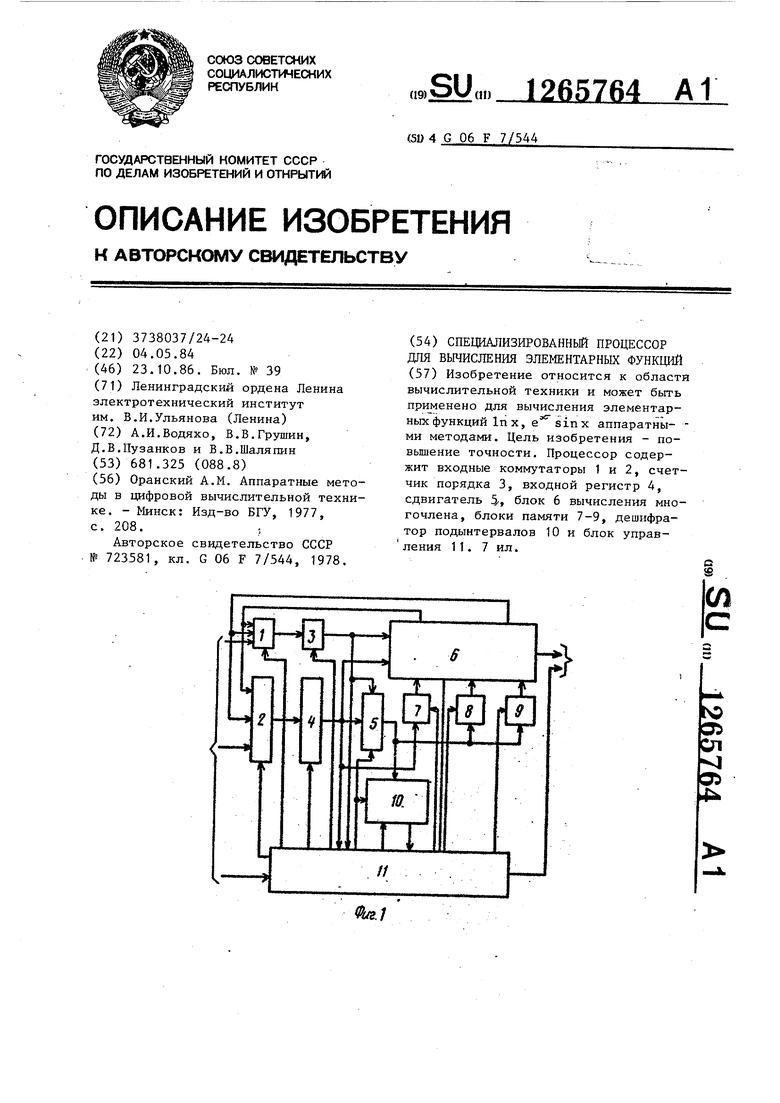

1 Изобретение относится к автоматике и вычислительной технике и может быть применено при вычислении элементарных функций njt- б , sinx аппаратными методами. Целью изобретения является повышение точности. На фиг. 1 представлена блок-схема процессора; на фиг. 2 - блок-схе ма блока вычисления многочлена; на фиг. 3-5 - блок-схемы алгоритмов; на фиг. 6 и 7 - блок-схема блока управления. Процессор содержит входные коммутаторы 1 и 2, счетчик 3 порядка, входной регистр 4, сдвигатель 5, блок 6 вычисления многочлена, блоки 7-9 памяти, дешифратор 10 подынтервалов и блок 1 1 управления. Блок 6 вычисления многочлена (фиг. 2) содержит коммутаторы 12 и 13, блок 14 умножения, коммутатор 155 сумматор 16, коммутатор 17 и регистр 18 результата. Блок 11 управления (фиг.6 и 7) содержит блок 19 микрокоманд, регистр 20 микрокоманд, шифратор 21 микрокоманд, счетчик 22 адреса микрокоманд и дешифратор 23 аргумента Шифратор 21 микрокоманд содержит элементы И 24-44, элементы ИЛИ 45 49, элементы НЕ 50-52 и дешифратор 53. Дешифратор 23 аргумента содержит дешифратор 54, элементы И 55-69, с лекторы 70 и 71, элементы И 72 и 73 и элементы НЕ 74 - 91. Вычисление функции разделяется два этапа: этап предварительной об работки и вычисление многочлена. Алгоритмы предварительной обработк основаны на известных соотношениях и различны для каждой функции. Сущ ность предварительной обработки св дится к приведению аргумента функции к интегралу о, 1J , Пусть представление чисел в ЦВМ находится в диапазоне ±(2 -2 ). Для ЕС ЭВМ N +256. -Тогда для функ ции е диапазону, изменения аргумен тов соответствуют три области изме нения функции: е.Г Этим трем областям можно соотнести два интервала изменения аргумента: 4 для областей I и III . для области II При /х| г , в зависимости от знака V , процессор генерирует либо оо , либо 0. Вычисления проводятся только для второй области изменения функции. Диапазон изменения аргумента при этом: -7, +7. Для вычисления функции е (фиг.З) в указанном диапазоне необходи14о выделить целую часть аргумента, вычислить функции от обеих частей аргумента и затем перемножить полученные значения: entx x-entu На вход процессора поступают мантисса аргумента (на коммутатор 2), порядок аргзшента (на коммутатор 1), признак функции е . и сигнал Пуск (в блок 11 управления). По сигналу Пуск блок 11 управления записывает аргумент во входной регистр 4 и счетчик 3 порядка. Затем начинается анализ величины порядка в блоке 11 управления. .Если порядок аргумента не равен Нулю, то в зависимости от знака порядка алгоритм приведения к интервалу разделяется на две ветви. Пусть знак порядка аргумента О, тогда при РК 7 формируется сигнал е оо, если РХ - 7, то мантисса аргумента сдвигается влево с одновременным вычитанием единицы из величины порядка. При сдвиге влево старшие разряды мантиссы заносятся в 1-8 разряды регистра 4. Эти разряды в дальнейшем служат адресом для первого блока 7 памяти, где хранятся величины е . При РХ - О необходимый сдвиг всей мантиссы аргумента вправо не происходит, а с помощью сдвигателя 5 вправо сдвигаются лишь разряды, составляюшде старшую часть мантиссы (S разрядов). Величина сдвига зависит от величины порядка аргумента, но не больше 7. В таблице поясняется работа сдвигателя 4 для S 10, управляемого тремя последними разрядами счетчика 3 порядка. Если РХ 7, то формируется сигнал е 0. Код, получаемый на выходе сдвигателя 5, передается на адресные входы второго 8 и третьего 9 блоков памяти и на входы дешифратора 10 подынтервала. Причем 1-5 разряды сдвигателя 5 соединены с адресными входами второго блока 8 памяти и входами дешифратора 10, а 1-3 и 6-10 разряды - с адресными входами третьего блока 9 памяти. После анализа кода подынтервала начинается вычисление многочлена в блоке 6 вычисления многочлена (фиг. 2) по схеме Горнера. По окончании вычисления многочле на в блоке 11 управления анализируе ся содержимое 1-8 разрядов входного регистра 4. Если все 1-8 разряды ра ны нулю, значением функции является значение многочлена. Если 1-8 разря ды не равны нулю, то из первого блока У памяти выбирается значение и передается в блок 14 умножения вместе со значением многочлена. Произведение Р(х)е через

коммутатор 17 и регистр 18 результата передается на выход. На этом процессор заканчивает свою работу.

Приведение к интервалу 10, lj аргумента функции Еп х основано на следующем. Пусть аргумент задается выражением

(5)

X. М,2Р,,

где М;( - мантисса аргумента X ; - РХ порядок аргумента х Логарифмируя равенство (5), получают :

Епх епМ,+ РХ Гп2. Име.ет место равенство ЕпМ n(1+Z)

где О Z ,

Z )( мантисса, сдвинутая таким образом, что может быть представлена кодом

(8)

U z.,z.,

--1 -2 Г)

fде Z; - двоичная цифра числа.

Сдвиг выполняется до первой ситуации, при которой перед запятой устанавливается единица, т.е. можно записать

MX -MX,

(9)

где К - число сдвигов до получения

кода (8). Таким образом

fnx Pn(l+Z)+(P,-K)fn2

(10)

многочлена приведенный аргумент со счетчика 3 порядка и входного регистра 4 передается в блок 14 умножения. 10-19 разряды входного регистра 4 передаются через сдвигатель 5 без сдвига, благодаря блокировке выходов счетчика 3 порядка признаком функции, на адресные входы второго 8 и третьего 9 блоков памяти и на вход дешифратора 10, где производится анализ кода на выходе сдвигателя 5. Если подынтервал длинный, то при вычислении многочлена выборка производится из блока 9 памяти, если подынтервал короткий - из блока 8. Значение Р(х) фиксируется на входном регистре 4 . Затем величина, хранимая на i счетчике 3 порядка (Q), передается в блок 14 умножения, где умножается на константу in 2. Константа En 2 реализуется путем установки 5 в пятой группе входов четвертого коммутатора 13 необходимых потенциалов. С входного регистра 4 на сумматор 16 поступает значение многочлена, а с выхода блока 14 умножения - произведение . Результат суммирования (значение функции) через шестой коммутатор 17 и регистр 18 результата поступает на выход, и процессор заканчивает свою работу.

Сведение аргумента функцииsin л к интервалу О, 1j основано на соотношении

sinif sin(2iik+cc)sin(f, (11) где (Р -к) - код, содержащийся на счетчике 3 порядка. Как и в предыдущем случае, на вход процессора поступают аргумент, признак функции и сигнал Пуск. По сигналу Пуск блок 11 управления записывает аргумент во входной регистр 4 и счетчик 3 порядка. Действия по вычислению функции начинаются с анализа знака мантиссы (фиг. 6). При отрицательном аргументе формируется сигнал Вычисление невозможно. Если знак мантиссы положительный, то аргумент сдвигается влево до появления в старшем разряде входного регистра 4 единицы. Порядок аргумента изменяется пропорционально количеству сдвигов. Затем для получения дробной части величины n(1+Z) содержимое входного регистра 4 сдвигает ся еще раз влево. Для вычисления

К - целое число;

Ч - переменная в интервале (О, 2).

(- ent 4;г)

(12)

2- Обозначим Z

- ent

где

21Г -

О . Z . Два старших разряда величины Z указывают номер квадранта, в котором находится угол Ц .

Представим величину sin Ч как

f

sinq sin 2uZ sin у 9, (13

где О ) i 1 . ,

Вычисление sin в зависимости /

от квадранта, в котором находится аргумент, выполняется по известным формулам.

По сигналу Пуск блок 11 управления записывает аргумент во входно регистр 4 и счетчик 3 порядка. Зате аргумент передается в блок 14 умножения, где умножается на -т. Произ )

ведение вновь записывается на входной регистр 4. Если порядок произведения Pj( 5 О и , то сдвигая влево содержимое входного регистра 4, добиваются равенства порядка нулю (получаем переменную Z). После выполнения сдвигов или при Р Q в блоке 11 управления анализируются 10 и 11 разряды входного регистра 4. В зависимости от номера квадранта и вида функции (sin х и cosx) принимается решение о вычитании

TT- Mv из единицы. Для этого аргу2ii

мент передается на вход сумматора 16. Полученная разность снова записывается во входной регистр 4. Затем содержимое входного регистра 4 сдвигается влево. Если не было необходимости получать разность, т подобные сдвиги выполняются сразу после определения квадранта. После этих действий содержимое входного регистра 4 передается на вход блока 14 умножения. Код с выхода сдвигате;ш 5 поступает на вход дешифратора 10. После определения вида подынтервала (длинный или короткий) начинается вычисление многочлена аналогично первым двум функциям.

Формула и зо бретения

Специализированньй процессор для вычисления элементарных функций, содержащий счетчик порядка, входной регистр, сдвигатель, блок управления и два блока памяти, причем выходы счетчика порядка соединены с входом первой группы разрядов сдвигателя.

входы второй группы разрядов которого соединены с выходами входного регистра и адресным входом первого блока памяти, выход сдвигателя COQ,динен с адресным входом второго блока памяти, отличающийся тем, что, с целью повышения точности, в него введены два входных коммутатора, блок вычисления многочлена, дешифратор подынтервалов и третий блок памяти, причем входы порядка и мантиссы процессора соединены с первыми инфор мационными входами соответственно первого и второго входных коммутаторов, выходы

которых соединены с информационными входами соответственно счетчика порядка и входногорегистра, выход сдвигателя соединен с входами первой группы разрядов дешифратора подынтервалов и адресным входом третьего блока памяти, причем блок вычисления многочлена содержит четыре коммутатора, блок умножения, сумматор и регистр результата, первый и второй

информационные входы первого коммутатора соединены с выходами соответственно счетчика порядка и входного регистра, выход которого соединен с первым информационным входом второго

коммутатора, второй и третий информационные входы которого соединены с выходами соответственно второго и третьего блоков памяти и соответственно с первым и вторым информационными входами третьего коммутатора, информационные входы с третьего по шестой которого соединены соответственно с выходом первого блока памяти, входами первой и второй констант процессора и выходом сумматора, соединенным также с вторыми информационными входами первого и второго входных коммутаторов, первым информационным входом четвертого

коммутатора, выход и второй информационный вход которого соединены соответственно с информационным входом регистра результата и выходом блока умножения, соединенным с третьими информационными входами первого и второго входных коммутаторов и первым информационным входом сумматора, второй информационный вхо которого соединен с выходом второго коммутатора, выходы первого и третьего коммутаторов соединены соответственно с первым и вторым информационными входами блока умножения, выход регистра результата соединен с выходом процессора, причем вход пуска блока управления является входом пуска процессора, группа выходов ограничения условий вычисления блока управления является группой управляющих выходов процессора, выход входного регистра соединен с входом задания функции блока управления, выходы группы разрядов с первой по шестнадцатую соединены с управляющими входами соответственно первого.и второго входных коммутаторов, входного регистра, счетчика порядка, сдвигателя, дешифратора подьштервала, с первого по третий блоков памяти, с первого по четвертый коммутаторов, блока умножения, сумматора и регистра результата, группа входов признаков блока управления соединена с выходом дешифратора подынтервалов, выход, счетчика порядка соединен с входом граничных условий блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления элементарных функций | 1984 |

|

SU1185329A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| Специализированный процессор | 1977 |

|

SU734705A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Специализированный процессор | 1977 |

|

SU723581A1 |

| Специализированный процессор для вычисления элементарных функций | 1985 |

|

SU1330627A1 |

| Устройство для вычисления функции @ =2 @ | 1981 |

|

SU1057942A1 |

| Специализированный процессор | 1981 |

|

SU1023339A1 |

| Устройство для вычисления тригонометрических функций с плавающей запятой | 1986 |

|

SU1425661A1 |

Изобретение относится к области вычислительной техники и может быть применено для вычисления элементарных функций 1пх, аппаратны- ми методами. Цель изобретения - повышение точности. Процессор содержит входные коммутаторы 1 и 2, счетчик порядка 3, входной регистр 4, сдвигатель 5- блок 6 вычисления многочлена, блоки памяти 7-9, дешифратор подынтервалов 10 и блок управления 11. 7 ил.

означает наличие на выходе сдвигателя регистра 4.

1 трвзря9ы

ortn-tf ал/г

Имнн поторонГ,г К wnMymomopotit t

бцвм 5 значения К-го разряда входного

d6i4uc/ief ue многоулена значение fiHoeffv eaa да

Нет

(Чтение первого ПЗУ 7

У/1но ение е ма

fioHeif Фиг.З

i Sf fruflofa/fue // м-Ji « лмтулул ffffosovjfe -- ,un

I

(Hava/io

/пнотение мантиссы на /гж

Сдвиг мантиссдг на 2разряда блебо

Bt wucAe Ke нногоч/гена

cdffus ноитиссы o/ieffo

( Конец J Фиг.5

Кдшг.б

| Оранский A.M | |||

| Аппаратные методы в цифровой вычислительной технике | |||

| - Минск: Изд-во БГУ, 1977, с | |||

| Гидравлическая или пневматическая передача | 0 |

|

SU208A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-23—Публикация

1984-05-04—Подача