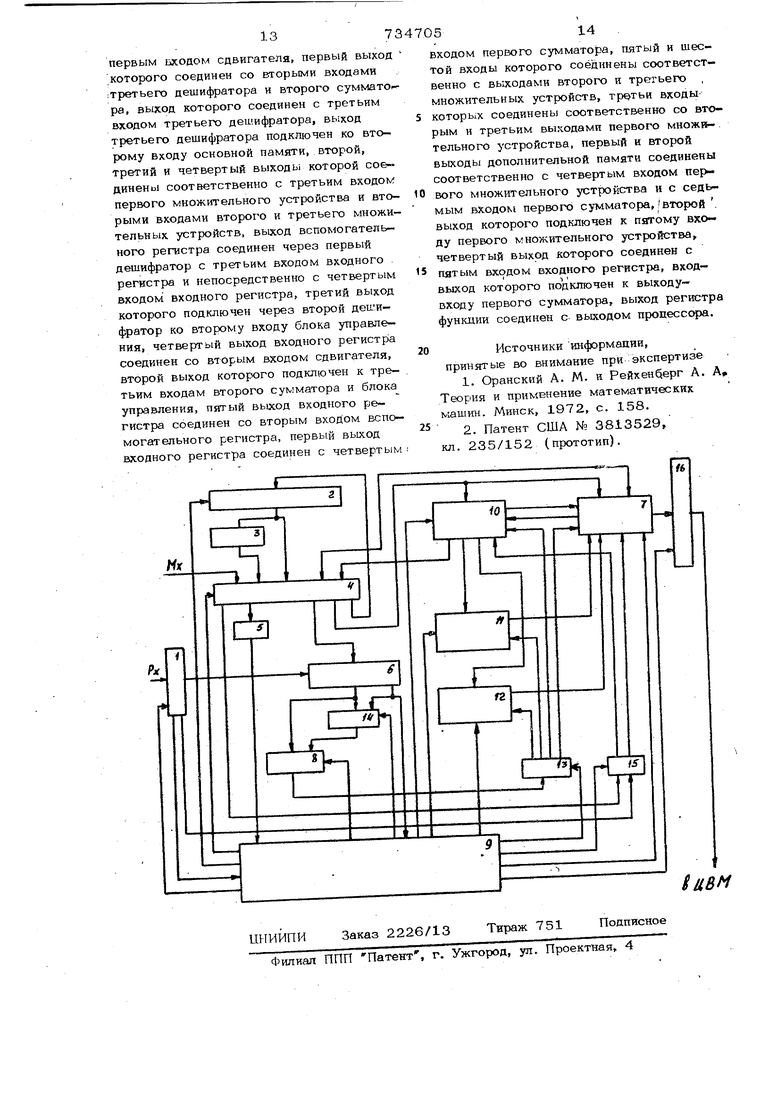

Изобретение относится к вычислительной технике и может быть использовано как в качестве автономного функционального преобразователя, так и в качестве периферийного устройства спепиализиро,ванных и универсальных ЦВМ для вычисления функций: е , л х , sinx . Известны процессоры для вычисления элементарных функций табличнрго типа на основе постоянного запоминающего устройства (ПЗУ), в состав которых входит регистр аргумента, в качестве которого используется регистр числа ПЗУ i Недостаток известного процессора - значительный объем памяти. Наиболее близким по технической суш ности к изобретению является специализи рованный процессор для вычисления элементарных функций ( интерполятор высокого порядка), содержащий входной регистр, на первую группу входов которого подается аргумент, первая груп па выходов входного регистра связана с первой группой входов множительного устройства, вторая группа выходов входного регистра связана со входами постоянного запоминающего устройства (ПЗУ),, в котором хранятся значения узловых точек функции, сумматор, первая группа входов которого связана с выходами множительного устройства, вторая группа входов множительного устройства связана с вькодами второй группы вентилей, выходы сумматора соединены с первой группой входов регистра функции, выходы ПЗУ связаны со входами второй группы вентилей, регистр функции, выходы которого соединены с первой группой входов первой группе вентилей, с второй группой входов выходного буфера, выходной буфер, выход которого соединен со входом ЦВМ, блок управления, выходы которого связаны со входами регистра функции, первой, второй группт вентилей, входного регистра выходного буфера 2 . Недостаток этого процессора - низкое быстродействие, связанное с тем, что вычисление функшм ведется по схеме Горнера. Такой способ вычисления функпии требует число умножений равным старшей степени многочлена. Поэтому при повышенных требованиях к точности вычисления (50--60 двоичных разрядов и более) время нахождения функции стано вится недопустимо большим. Цепь изобретения - повышение бьютро действия. Поставленная дель достигается тем, что в специализированный процессор, содержащий входной регистр, первое множительное устройство,первый сумматор, основную память, регистр функции, счетчик порядка, причем первый выход первого сумматора соединен с первым входом регистра функции, второй вход которого подключен к первому выходу блока управления, первый вход счетчика порядк соединен со входом процессора, первый выход входного регистра соединен с первым входом первого множительного устройства, первый выход которого соединен с первым входом первого сумматора, второй вход которого подключен к первому выходу основной памяти, вход процессора соединен с первым входом входного регистра, второй вход которого подклю чен к второму выходу блока управления, введены вспомогательный регистр, дешифраторы, сдвигатель, второй сумматор, второе и третье мноиштельные устройств дополнительная память, причем третий выход блока управления соединен с третьим входом первого сумматора, четве{ тый и пятый выходы - соответственно с первыми входами основной и дополнитель ной памяти, шестой, седьмой и восьмой выходы - соответственно с первыми входами второго и третьего множительных устройств и со вторым входом первого множительного устройства, девятый и десятый вькодь - соответственно с первы- ми входами второго сумматора и третьег дешифратора, одиннадцатый выход - с первым входом вспомогательного регистр двенадцатый выход - с вторым входом счетчика порядка, первый выход которого соединен с первым входом блока управле ния, второй выход счетчика порядка соединен со вторым входом дополнительной пам)гги, третий вход которой подключен ко второму выходу входного регистра, третий выход счетчика порядка соединен с первым входом сдвигателя, первый выход которого соединен со вторыми вхо дами третьего дешифратора и второго сум матора, выход которого соединен с тре054тьим входом третьего дешифратора, вььход третьего дешифратора подключен ко второму входу основной памяти, второй, третий и четвертый выходы которой соединены соответственно с третьим входом первого множительного устройства и вторыми входами второго и третьего множительных устройств, выход вспомогательного регистра соединен через первый деши(|ратор с третьим входом входного регистра и непосредственно с четвертым входом входногх регистра, третий выход которого подключен через второй дешифратор ко второму входу блока управления, четвертый выход входного регистра соединен со вторым входом сдвигателя, второй выход которогбподключен к третьим входам второго сумматора- и блока управления, пятый выход входногхэ регистра соединен со вторым входом вспомогательного регистра, первый выход входного регистра соединен с четвертым входом первого сумматора, пятшй и шестой входы которого соединены соответст- венно с выходами второго и третьего множительных устройств, третьи входы коTopbix соединены соответственно со вторым и третьим выходами первого множительного устройства, первый и второй выходы дополнительной памяти соединены соответственно с четвертым входом первого множительного устройства и с седьмым входом первого сумматора, вто-. рой вьлод которого подключен к пятому входу первого множительного устройства, четвертый выход которого соединен с пятым входом входного регистра, входвыход которого подключен к выходувходу первого сумматора, выход регистра функции соединен с выходом процессора. Блок-схема специализированного процессора представлена на чертеже. Процес1 ор содержит счетчик 1 порядка, вспомогательный регистр 2, первый деши4чзатор 3, входной регистр 4, второй дешифратор 5, сдвигатель 6, первый сумматор 7, третий деи1и4ратор 8, блок 9 управления, первое 10, второе 11 и третье 12 множительные устройства, основная память 13, второй сумматор 14, дополнительная память 15, регистр 16 функции. Процессор работает следующим об- разом, Вычисление функции в процессоре разделяется на два этапа. На первом этапе диапазон изменения аргумента функции сводится к интервалу р, l . Затем происходит процесс вычисления функции. Следует заметить, что способ приведения аргумента к заданному интервалу зависит от вида функции, а процесс вычисления функции одинаков для всех указанных функций. Рассмотрим приведе ние аргумента к интервалу р, l в отдельности для каждой из функций е ir X , smxicosx) при условии, что диапазон изменения их аргумента + (2 - 2). I. Функция е, в соответствии с диапазоном представления аргумента выделяют три обла .ти изменения функции: Этим трем областям соответствуют две области изменения аргумента: При 2в зависимости о знака X процессор долже11 генерироват сигнал схз и О. Таким образом, выч 1сление имеет сь/:ь сл лишь для х MQn , что соответствует двоичному порядку PV Ъ переменной X , Фун кцию можно представить в виде jcntx oX.-en-t).. . р -функция от целой части аргумента; „x-enlx -функция от дробной части аргумента. Т. е. для вычисления функции е в указанном диапазоне необходимо выдели целую часть аргумента, вычислить функ ции от обеих частей аргумента и затем перемножить полученные значения. Действия по приведению аргумента начинаются после поступления на входн регистр 4 мантиссы аргумента MX на счетчик 1 порядка аргумента Р и блок 9 управления признака функции признаку функции блок 9 управления на страивается на выполнение определенно алгоритма, который начинается с анал порядка аргумента. Если порядок аргумента не равен ну то в зависимости о-т знака порядка алго в ритм приведения к интервалу разделяется на две ветви. Пусть знак порядка О, тогда при РХ - формируется сигнал , если PV то мантисса аргумента сдвигается влево с одновременным вычитанием единицы из величины порядка. Для повышения быстродействия сдвиги выполншотся не пюследоватепько во входном регистре 4, а с помощью вспомогательного регистра 2 и дешифратора 3. Сдвиг происходит в дещифраторе 3, на который подается аргумент, пред- . варительно записанный во вспомогательный регистр 2. Сдвинутый аргумент вновь поступает во входной регистр 4. Дещифра- тор 5 представляет собой набор стандартных схем И-ИЛИ, управляемых блоком 9 управления. Сдвиг аргукжнта продолжается до равенства порядка нулю L разрядов входного рет истра 4 (соответствующие целой части аргумента), провер$вотся затем на равенство нулю (условие и в случае напичая ненулевых битов из памяти 15 выбирается значение е Формирование адреса памяти 13 связано с методом сокращения степени мно- гочлеиа аппроксимирующего функцию. Суть метода состоит в следующем. К таблично-алгоритмическим методам относятся методы, использующие хранение коэффициентов многочлена в запоминающем устройстве и алгоритмический способ вычисления самого многочлена. При этом мантисса аргумента разделяется на две части: старшую ст разрядность которой определяется адресностью запоминающего устройства, и младщую Каждому значению Хр на интервале Р, l изменения функции соответствует своя узловая точка. Всего таких точек 2 , где - величина KC . После анализа S +1- 1Ьазряда аргумента формируется адрес памяти 13 на основании разложения: ) .лУ-(с. (к 4U) («.% где если г Т. е., если значение к значению Хс прибавляется единица и из памяти выбираются коэффициенты многочлена, соответствующие соседней узловой точке.

Or затем необходимо отнять величину 2, Если Х , то модификадии аргумента не происходит. Использование формулы (4) уменьшает в 2 раза аргумент аппроксимируюшегх)

многочлена, в силу че;го абсолютная ошибка сокращается в 2 раз. При заданной точности описанный прием позволяет со- кратить степень многочлена, что приводит к повьпиению быстродействия.

Для схемной реализации этого метода ,

служат сдвигатель 6, второй сумматор 14 и дешифратор 3. Сдвигатель 6 необходим для сдвига старших S +1 разряда аргумента вправо. Сдвиг вправо всей мантиссы приводит к значительной потере точности представления аргумента. Величина сдвига зависит от порядка у а. гумента, но не больше L . Таблица поясняет работу сдвигателя 6 для S 1С управляемого тремя последними разрядами счетчика 1 порядка.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| Специализированный процессор для вычисления элементарных функций | 1984 |

|

SU1265764A1 |

| Устройство для вычисления элементарных функций | 1984 |

|

SU1185329A1 |

| Специализированный процессор | 1977 |

|

SU723581A1 |

| Специализированный процессор | 1981 |

|

SU1023339A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Специализированный процессор для вычисления элементарных функций | 1985 |

|

SU1330627A1 |

| Устройство для вычисления функции @ =2 @ | 1981 |

|

SU1057942A1 |

| Устройство для вычисления функций синуса и косинуса | 1987 |

|

SU1494002A2 |

Примечание. +

Если после сдвига ( S +1)ый разрщравен единице, го значения первьш S разрядов складываются с ним на втором сумматоре 14 и через дешифратор 3 подаются на адрес1 ые вхрды памяти 13. Одновременно с этими действиями из вычитается единица на пергюм сумматоре 7.

Если ( S +1)-ь;й разряд сдвягателя 6 не равен единице, то блок 9 yapatvie-. ния никаких действий по преобразованию Ст vi производит. X,. 3 обход

второго сумматора 14 через дешифратор 3 сразу поступает на адресные входы памяти 13 (дешифратор строится на ос .нове стандартных схем И-ИЛИ).

II. Функция Сп X .

Пусть аргумент задается выражением

.

(5)

где MX - мантисса X ; Р - порядок X

Используя известное в элементарной математике соотношение, получаем

елх-епм 4р еп2. (б)

Обычно логарифм представляют в виде h (1+ г ), где 1. Это соответствует равенству

nMx 2n(uz),()

где Z М;( 1, VAx - мантисса сдвинутая таким образом, что моясет быть представлена кодом

..(8)

Рде Т.- - двоичная цифра числа.

Сдвйг выполняется до первой ситуации, при которой перед запятой устанавливается единица, т.е. можно записать

Mx-M,2

О)

где К. - число сдвигов до получения кода (10). Таким образом означает наличие на выходе сдвигателя 6 значения к-го разряда входного регистра 4. ,()р еп1епм -кгл2 -p en2-Er(U2)4()ena () где (Р, - к )-код, содержащийся на сче чике 1 пор5щка. Действия по вычислению функции начинаются с анализа знака мантиссь. При отрицательном аргументе формирует ся сигнал В лчисление невозможно . Если знак мантиссы положительный, то аргумент сдвигается влево до появления в старшем разряде входного регистра 4 единицы. Величина сдвига определяется количеством старших нулевых разрядов аргумента во входном регистре 4. Для их обнаружения введен дешифратор 8, принцип работы которого определяется уравнениями типа: ...а где Р; V -ый выход схемы; - инверсный к старших , Ql,«7r-/«K разр5 дов аргумента. Дешифратор имеет несколько выходов на определенные величины сдвига. Сдвиг вь:полняются так же, как в случае функции е . Порядок соответственно изменяется пропорционально количеству сдвигов. Затем для получения дробной части величины Рп (1 +Z ) содержимое вход Hoixi регистра 4 сдвигается еще раз влево без изменения кода в счетчике 1 порядка. Формирование адреса памяти 13 выполняется так же, ка и в пр хыдущем случае на основании формулы (6) Величина () малоразрядна и в целях повьпления быстродействия целесообразно выполнить умножение () 2 в ПЗ Для этой цели служит память 15. Она сое тоит из двух частей: в первой части содер а во вторюй - жатся значения е значения (РК К ) вп 2 111. Функция slnx Сведение аргумента функции «пХ к р, 1 основано на соотноинтервалушении S;nx Sin(2nкл-) вln, где к - пелое число; Ч - переменная в интервале р, 2 -2( 2TC.( --ent er) TTt . у Обозначим 7 -entie -, где Два старших разрада величины Z ука- . (} зывают номер квадранта, в котором находится угол Ч . Представим величину , как - (14) in 1 - e naitz sm Vj где О V 1. Вычисление sm - V в зависвмостн от квадранта, в котором находится аргумент, производится по формулам: sin - V 1 квадранта, 1-тр sm-() для П квадранта, (15) {щу квадранта. ) для 1У квадранта. Переход к функции cos х можно осуществить по формуле cos х,- (х -V ) . , ( в том случае формулы вычисления записываются так: - И-V) для 1 квадранта, для П квадранта (17) -sin- -V для UI квадранта, -sin Jv для 1У квадранта, Приведение к интервалу в спецпроцессоре начинается с умножения мантиссы MX на 1/2 в первом множительном устройстве 1О. Полученное произведение записывается во входной регистр 4. Если ОРВДО нроидаедения РХ О и РХ О, то сдвигами влево содержимого входного регистра 4 добиваются равенства порядка нулю (т.е. получаем переменную Z ). В зависимостн от номера квадранта и вв ФУНКЦИИ (в(ПХ или cos М из ед инияы вычитается Л ( , находнщаяса во входном регистре 4 ( формулы 15 и 17) . Дпя перехода от переменной i к переменной VMX сдвигается влево на два разряда без изменения порядка. Действия блока 9 утфавления дпя получения адреса памяти 13 аналогичны действие в обоих предыдущих случаях. После формирования адресов памяти 13 в 15 и выборки коэффициентов многочпена начинается вычисление функции. nn-ervv X Вычисление величины I п(.У, S«n производится алгор мическн. Все эти функции аппроксимируются рядом Тейлора одинаковой степени. Последовательность действий по вычислению многочлена может бьггь избрана разная. Для повь.шения действия в предлагаемом процессоре используются еще дополнительно два малоразрядных множительных устройства. Это позвсзяяет распараллелить. процесс вы-. числения функции. Последовательность действий по вычислению м югочлена пятой степени: F(x) b)()b..b/..X где F(x) - вычисляемая функция; Ь- b ... ,bg. - коэффициент многочлена; X - аргумент, Степень многочлена выбрана из требо ваний по точности вычисления р(х) (разрядность аргумента 50-6О разрядов Сначала на первом мномштельном устройстве вычисляется значение X и параллельно с ним на втором кчножительном устройстве 11 значение Ь,,Х. На втором этапе вычисления работают парал лельно все множительньде устройства и второй сумматор 14: на первом мнодси- тельном устройстве 1О вычисляется на втором 11 - , на третьем 12 Х , на втором сумматоре 14 - сумма Ь + Ь, X . Затем одновременно находятся значения b . Xна первом множительном устройстве 10, bgX на третьем мнежительном устройстве 12, .на втором сумматоре 14. Причем первый сумматор 7 формирует сумму во время работы первого множительного устройства 1О. Последующу5о работу процессора составляет нахождение всей суммы в скобке формулы (18), ее умножение на X в первом множительном устройстве 10 и вычисле И1е окончательного результата. Так как первое множительное уигройс во 10 обрабатывает операкдь, полной раз рядности, а остальнь е множите; ьк-: 1е уст ройства малоразрядные и работают параллельно с первым, то время умножения определяется только временем работ первого множительного устройства 10. Время вычисления функции в предлага емом процессоре составляет 1УМИ. СП . Сигналш для управления работой бсех блоков- процессора поступают из блока O 0512 9 управления, который представляет собой конечный автомат Мили или Мура. Уменьшение времени вычисления в предлагаемом процессоре составляет 1,1 МКС или около 50% по отношению време 1и вычисления функции в известном при увеличении аппаратурных затрат на . 15-20%. Формула изобретения Специализированный процессор, содержащий входной регистр, первое множительное устройство, первый сумматор, основную па.мять, регистр функции, счетчик порядка, причем первый выход первого сумматора соединен с первьгм входок регистра функции, второй вход которого подключен к первому выходу блока управления, первый вход счетчика порядка соединен со входом процессора, первый выход входного регистра соединен с первым входом первого множительного устройства, первый которого соединен с первым входом первого сумматора, второй вход которого подключен к первому выходу основной памяти, вход процессора соединен с первым входом входного регистра, второй вход которого подключен к второму ЬЫХОДУ блока управления, ,о т личаюшийся тем, что, с целью повышения быстродействия, в процессор введены вспомогательной регистр, дешифраторы, сдвигате.Г1Ь, второй сумматор, второе и третье множительные устройства, дополнительная память, причем третий вы.ход блока управления соединен с третьим входом первого сумматора, четвертый и пятый выход - соответственно с первыми вxoдa ш основной и дополнительной памяти, шестой, седьмой и восьмой выходы - соответственно с первь.ми входами второго и третьего множительного устройств и со вторым входом .первого множитель- ного устройства, девятый и десятый выходы - соответственно с первыми входами второго сумматора и третьего дешифратора, одиннадцатый выход с первым входок вспомогательногх) регистра, двенадцатый выход - со вторь.м входом счетчика порядка, первый вь;хоп которого соединен с первым входом блока управления, второй вь1ход счетчика порядка соединен со вторым входом дополнительной памяти, третий вход которой подключен ко второму выходу входного регистра, третий выход счетчика порядка соединен с

первым входом сдвигатепя, первый выход которого соединен со вторыми входами ;третьего дешифратора и второго сумматора, выход которого соединен с третьим входом третьего дешифратора, выход третьего дешифратора подключен ко второму Входу основной памяти, второй, третий и четвертый выходы которой соединены соответственно с третьим входом первого множительного устройства и вторыми входами второго и третьего множительных устройств, выход вспомогательного регистра соединен через первый дешифратор с третьим входом входного регистра и непосредственно с четвертым входом входного регистра, третий выход которого подключен через вторюй дешифратор ко второму входу блока управления, четвертый выход входного регистра соединен со вторым входом сдвигателя, второй выход которого подключен к третьим входам второго сумматора и блока управления, пятый выход входного регистра соединен со вторым входом вспо могательного регистра, первый выход входного регистра соединен с четвертым

ВХОДОМ первого сумматора, пятый и шестой входы которого соединены соответственно с выходами второго и трегьего множительных устройств, третьи входыкоторых соединены соответственно со вторым и третьим выходами первого множи-. тельного устройства, первый и второй выходь дополнительной памяти соединены соответственно с четвертым входом первого множительного устройства и с седьмым входом первого сумматора, Iвторой . выход которого подключен к nsfrouy входу первого множительного устройства, четвертый выход которого соединен с пятым входом входного регистра, входвыход которого подключен к выходувходу первого сумматора, выход регистра функции соединен с выходом процессора.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1980-05-15—Публикация

1977-12-14—Подача