(5) УСТРОЙСТВО ДЛЯ ОБНАРУ«ЕНИЯ И РЕГИСТРАЦИИ ОШИБОК ДИСКРЕТНОГО КАНАЛА СВЯЗИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения и регистрации ошибок дискретного канала связи | 1979 |

|

SU862375A1 |

| Устройство для контроля качества канала связи | 1979 |

|

SU856023A1 |

| Устройство для обнаружения и регистрациипОТОКА ОшибОК диСКРЕТНОгО КАНАлА СВязи | 1979 |

|

SU836804A2 |

| Система передачи дискретной информации | 1985 |

|

SU1325719A1 |

| УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ И РЕГИСТРАЦИИ ОШИБОК ДИСКРЕТНОГО КАНАЛА ПЕРЕДАЧИ И НАКОПЛЕНИЯ ИНФОРМАЦИИ | 1985 |

|

SU1378757A1 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1988 |

|

SU1596464A1 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО ИЗМЕРЕНИЯ ХАРАКТЕРИСТИК ДИСКРЕТНОГО КАНАЛА СВЯЗИ | 1995 |

|

RU2138910C1 |

| Устройство для обнаружения и регистрации потока ошибок дискретного канала связи | 1974 |

|

SU593320A1 |

| Устройство для обнаружения и регистрации ошибок дискретного канала передачи и накопления информации | 1988 |

|

SU1567078A1 |

| Анализатор состояния сети обменадиСКРЕТНыМи СООбщЕНияМи | 1979 |

|

SU801271A2 |

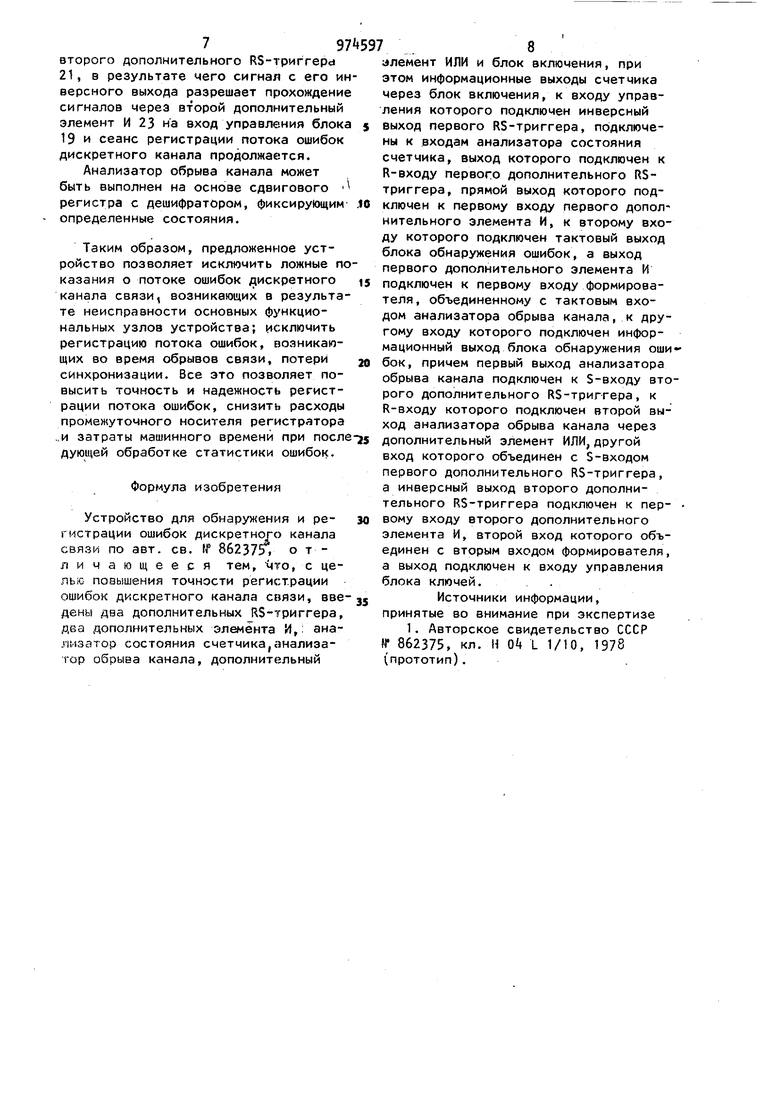

Изобретение относится к технике электросвязи и может использоваться в аппаратуре для статического исследования дискретных каналов связи. По основному авт. св. № 862375 изве.стно устройство для обнаружения и регистрации ошибок дискретного канала связи, содержащее блок обнаружения ошибок, элемент ИЛИ, блок ключей, счетчик, блок управления, регистратор формирователь, блок промежуточной памяти, два RS-триггера, коммутатор, регистр сдвига, блок элементов ИЛИ и два элемента И, блок промежуточной па мяти соединен с входом регистратора, синхронизирукяций выход которого через блок управления подключен к управляющим входам блока промежуточной памяти и регистратора, а тактовый выход блока -обнаружения ошибок соединен с первым Ъходом формирователя, объединенным с первым входом первого элемента И,-выход которого связан с счетным ВХОДОМ счетчика, а первый выход формировйтеля соединен с R-входом первого RS-триггера, инверсный-выход которого подключен к второму входу первого элемента И и S-входу второго RS-триггера, а S-вход первого RS-триг гера и второй вход формирователя объединены и подключены к выходу элемента ИЛИ, первый и второй вход которого соединены соответственно с выходом Ошибка блока обнаружения ошибок и выходом переполнения счетчика, инфор мационные выходы которого через koMмутатор, вход управления которого подключен к выходу второго элемента И, соединены с соответствующими входами блока элементов ИЛИ, выходы которых подключены к информационным входам блока промежуточной памяти, первый и второй вход второго элемента И соединены соответственно с тактовым выходом блока обнаружения ошибок и с прямым выходом второго RSтриггера, R-вход которого объединен 397 с входом установки нулевого состояния счетчика, входом управления блока клю чей и вторым выходом формирователя, примем информационный выход регистра сдвига, информационный вход и выход сдвига которого соединены соответственно с выходом Ошибка и тактовым выходом блока обнаружения ошибок, через последовательно соединенные блок ключей, блок элементов ИЛИ и блок промежуточной памяти подключены к входу регистра tlj. Однако известное устройство имеет низкую точность регистрации ошибок дискретного канала связи, . Цель изобретения - повышение точ-ности регистрации ошибок дискретного канала связи. Для этого в устройство для обнару жения и регистрации ошибок дискретного канала связи введены дна дополнительных RS-триггера, два дополнительных элемента И, анализатор состо яния счетчика, анализатор обрыва канала, дополнительный элемент ИЛИ и блок включения, при этом инйормационные выходы счетчика через блок вкл чения, к входу управления которого подключен инверсный выход первого :- 3 -триггера, подключены к входам ана лизлтора состояния счетчика, выход котсфого подключен к R-Bxofly первого дополнительного RS-триггера, прямой выход которого подключен к первому входу первого дополнительного элемен та И, к второму входу которого подKnsc-feH тактовый выход блока обнаруже |;юл ошибок, а выход первого дополнительного элемента и подключен к первому входу формирователя, объединенному с тактовым входом анализатора обрыва канала, к другому входу которого подключен информационный вы.1Д блока обнаружения ошибок, примем первый выход анализатора обрыва канала подключен к S-входу второго дополнительного RS-триггера, к R-BXO ду которого подключен второй выход анализатора обрыва каналы через дополнительный элемент ИЛИ, другой вхо iiOToporo обг- единен с S-входом первого дополнительного RS-триггера, а инверсный выход второго дополнительного RS-триггера подключен к первому входу второго дополнительного элемен та И, второй вход которого объединен с вторым входом формирователя, а выход подключен к входу управления бло ка ключей. На чертеже представлена структурая схема предложенного устройства. . Устройствоjдля обнаружения и реистрации ошибок дискретного канала вязи содержит блок 1 обнаружения шибок, первый и второй элементы И , 3 соответственно, блок управления, формирователь 5, счетчик 6, блок 7 включения, анализатор 8 состояния счетчика, регистратор 9 первый и второй RS-триггеры 10, 11 соответственно, элемент ИЛИ 12, коммутатор 13, регистр сдвига k, блок 15 элементов ИЛИ, блок 1б промежуточной памяти, анализатор 17 обрыва канала, дополнительный элемент ИЛИ 18, блок 19 ключей, первый и второй дополнительные RS-триггеры 20, 21 соответственно, первый и второй дополнительные элементы И 22, 23 соответственно. Устройство работает следующим образом. Сигнал Начало сеанса измерения, поступая с внешней аппаратуры непосредственно на S-вход первого допол нительного RS-триггера 20, а черездополнительный элемент ИЛИ 18 на R-вход второго дополнительного RSтриггера 21, устанавливает последние соответственно в единичное и нулевое состояния. Потенциал с прямого выхода первого дополнительного RS-триггера 20 разрешает прохождение сигналов через первый дополнительный элемент И 22, а потенциал с инверсного выхода второго дополнительного RS-триггера 21 прохождение сигналов с соответствующего выхода формирователя 5 через второй дополнительный элемент И 23 на вход управления блока 19 ключей. С помощью блока 1 обнаружения ошибок первого дополнительного элемента И 22, первого дополнительного RSтриггера 20, первого элемента И 2, формирователя 5, счетчика 6, двух RS-триггеров 10, 11 элемента ИЛИ 12, коммутатора 13, второго элемента И 3 б:лока 15 элементов ИЛИ, блока 16 промежуточной памяти, второго дополнительного элемента И 23, блока 19 ключей, регистра сдвига 1, регистратора 9, блока управления 4 происходит обнаружение и регистрация потока ошибок дискретного потока связи. . Одновременно с этим работают схемы, включающие: блок 7 включения, анализатор 8 состояния счетчика, первый дополнительный RS-триггер 20, инфор59мационные выходы счетчика 6 через блок 7 включения соединены с анализатором 8 состояния счетчика, выход которого подключен к R-входу первого дополнительного RS-триггера 20, прямой выход которого связан с одним из входов первого дополнительного элемента И 22; анализатор 17 обрыва канала, дополнительный элемент ИЛИ 18, вторые дополнительные RS-триггер 21 и элемент И 23, информационный и тактовый вход анализатора 17 соединены соответственно с выходом Ошибка и выходом первого дополнительного элемента И 22, а первый и второй выход анализатора 17 обрыва канала подключены непосредственно к 5-входу, и через дополнительный элемент ИЛИ 18 к R-входу второго дополнительного RS-триггера 21 соответственно, причем

его инверсный выход соединен с вторым входом дополнительного элемента И 23. выход последнего подключен к входу управления блока 19 ключей.

При отсутствии ошибок в последова- 25 тельности, поступающей с выхода Ошибка блока 1 обнаружения ошибок, тактовые импульсы через первый дополнительный элемент И 22, на второй вход которого подается разрешаюи(ий сигнал 39 с прямого выхода первого дополнительного RS-триггера 20, поступают на элемент И 2. На второй вход элемента И 2, объединенный с входом управления блока 7 включения, поступает сиг нал с инверсного выхода RS-триггера 10, разрешающий: прохождение сигналов с выхода первого дополнительного элемента И 22 на счетный вход счетчика 6 через элемент И 2; подключение через блок 7 включения информаци онных сигналов с выходов счетчиков 6 к анализатору 8 состояния счетчика. В случае неисправности счетчика 6 анализатор состояния счетчика выдает сигнал, поступающий на внешнюю аппаратуру, сигнализируя о неисправности устройства. Этот сигнал запрещает про хождение тактовых импуьсов с его выхода на соответствующие элементы И, формирователь 5, анализатор 17 обрыва канала, вход сдвига регистра сдвига 1, вследствие чего исключается регистрация потока ошибок через по ;ледовательно соединенные коммутатор 13, блок 15 элементов ИЛИ, блок 1б промежуточной памяти на регистраторе ,9.

триггера 21, на вход управления блока 19 ключей и разрешает регистрацию последовательности, записанной в ре:гистре сдвига k через последовательно соединенные блок 19 ключей, блок 15 элементов ИЛИ, 16 промежуточной памяти на регистратор 9. Одновременно последовательность ошибок поступает на информационный вход анализатора 17 обрыва канала, на другой вход которого поступают через открытый первый дополнительный элемент И 22 импульсы тактовой частоты с блока 1 обнаружения ошибок. В 7 Тем самым автоматически исключает ся регистрация ложных показаний о потоке ошибок, возникающих вследствие неисправности счетчика 6, уменьшаечхя расход промежуточного носителя регистратора 9, повышается точность регистрации потока ошибок. При появлении на выходе Ошибка блока 1 обнаружения ошибок сигнала Ошибка последний поступает через элемент ИЛИ 12 на R-вход первого RSтриггера 10 и на вход формирователя 5, разрешая формирование на его выходе сигнала через семь тактов после прихода сигнала Ошибка. Сигнал с выхода формирователя 5 поступает через второй дополнительный элемент И 23, открытый сигналом с инверсного выхода второго дополнительного RSслучае наличия обрыва связи или потери синхронизации на выходе анализатора 17 обрыва канала появляется сигнал, поступающий на S-вход второго дополнительного RS-триггера 21. По сигналу с его инверсного выхода, поступающему на второй вход второго дополнительного элемента И 23, запрещается прохождение сигналов с выхода формирователя на вход управления блока 19 ключей, в результате чего прекращается регистрация последовательности, записанной в регистре сдвига 1 через последовательно соепиненные блок 19 ключей, блок 15 элементов ИЛИ, блок 16 промежуточной памяти на регистратор 9 на все время обрыва связи. В результате снижается расход промежуточного Носителя регистратора 9, автоматически исключаются из статистики ошибки, возникающие из-за обрыва связи. При окончании обрыва связи анализатор 17 выдает на другом .выходе сигнал, поступающий через дополнительный элемент ИЛИ 18 на R-вход э второго дополнительного Д5-триггера 21, в результате чего сигнал с его ин версного выхода разрешает прохождение сигналов через второй дополнительный элемент И 23 на вход управления блока 19 и сеанс регистрации потока ошибок дискретного канала продолжается. Анализатор обрыва канала может быть выполнен на основе сдвигового регистра с дешифратором, фиксирующим определенные состояния. Таким образом, предложенное устройство позволяет исключить ложные по казания о потоке ошибок дискретного канала связи, возникающих в результате неисправности основных функциональных узлов устройства; исключить регистрацию потока ошибок, возникающих во время обрывов связи, потери синхронизации. Все это позволяет повысить точность и надежность регистрации потока ошибок, снизить расходы промежуточного носителя регистратора „и затраты машинного времени при посл дующей обработке статистики ошибок. Формула изобретения Устройство для обнаружения и регистрации ошибок дискретного канала связи по авт. св. № 8б237р, отличающееся тем, что, с целью повышения точности регистрации ошибок дискретного канала связи, вве дены два дополнительных RS-триггера, два дополнительных элемента И,: анализатор состояния счетчика анализагор обрыва канала, дополнительный злемент ИЛИ и блок включения, при этом информационные выходы счетчика через блок включения, к входу управления которого подключен инверсный выход первого RS-триггера, подключены к входам анализатора состояния счетчика, выход которого подключен к R-входу первого дополнительного RSтриггера, прямой выход которого подключен к первому входу первого дополнительного элемента И, к второму входу которого подключен тактовый выход блока обнаружения ошибок, а выход первого дополнительного элемента И подключен к первому входу формирователя, объединенному с тактовым входом анализатора обрыва канала, к другому входу которого подключен информационный выход блока обнаружения , причем первый выход анализатора обрыва канала подключен к S-входу второго дополнительного RS-триггера, к R-входу которого подключен второй выход анализатора обрыва канала через дополнительный элемент ИЛИ, другой вход которого объединен с S-входом первого дополнительного RS-триггера, а инверсный выход второго дополнительного RS-триггера подключен к пер- вому входу второго дополнительного элемента И, второй вход которого объединен с вторым входом формирователя, а выход подключен к входу управления блока ключей. . Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР « 862375, кл. Н Oi L 1/10, 1978 (прототип).

Начало сеанса изме(енил

Авторы

Даты

1982-11-15—Публикация

1980-06-13—Подача