Изобретение относится к вычислительной технике и может быть использовано в аппаратуре, предназначенной для статистических исследований каналов связи и накопления информации.

Цель изобретения - повышение быстродействия устройства.

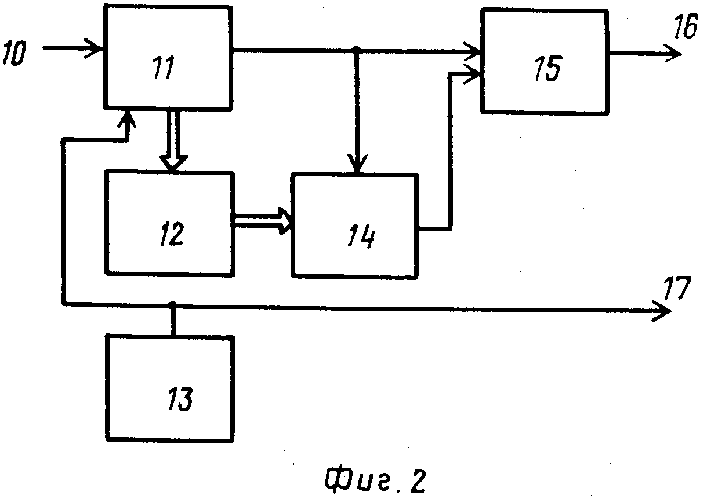

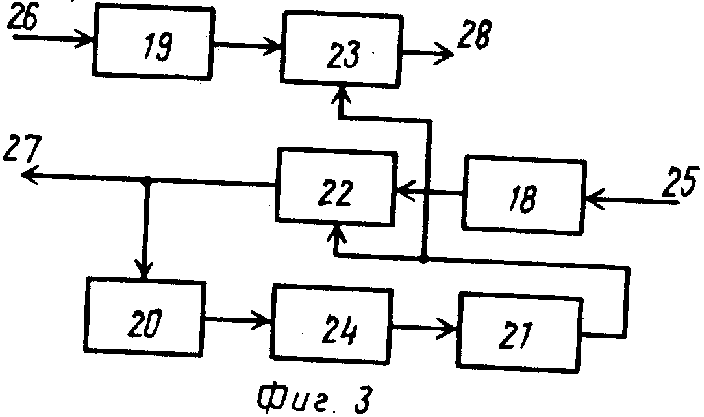

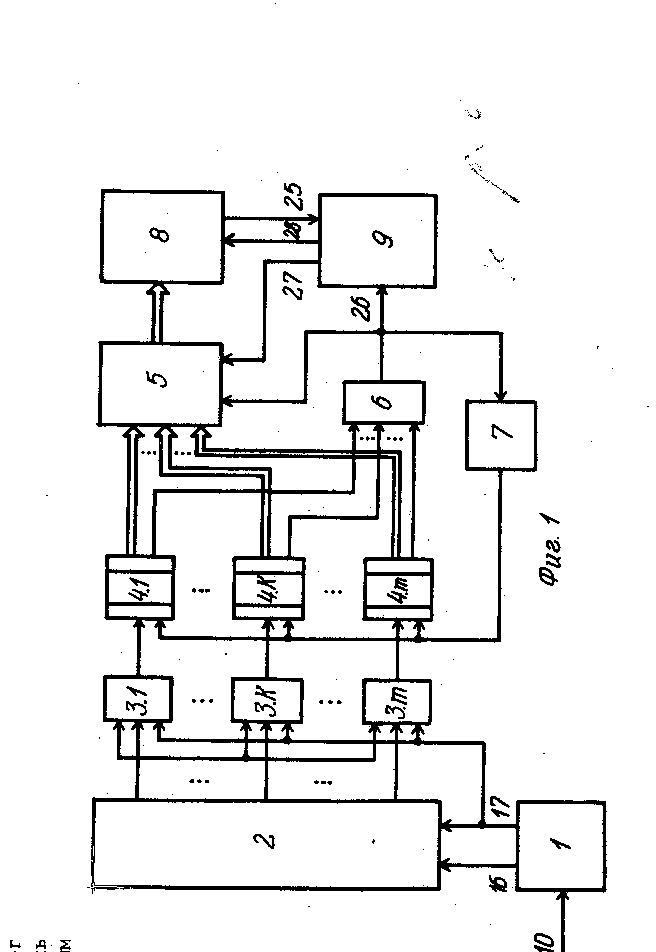

На фиг. 1 приведена блок-схема устройства; на фиг. 2 - блок-схема блока обнаружения ошибок; на фиг. 3 - блок-схема блока управления.

Устройство для обнаружения и регистрации ошибок дискретного канала передачи и накопления информации содержит блок 1 обнаружения ошибок, регистр 2 сдвига, элементы 3 И, счетчики 4, блок 5 промежуточной памяти, элемент 6 ИЛИ, формирователь 7 импульсов, регистратор 8 и блок 9 управления. На фиг. 1 обозначен вход 10 устройства.

Блок 1 обнаружения ошибок выполнен (см. фиг. 2) на регистре 11 сдвига, группе 12 сумматоров по модулю два, генераторе 13 тактовых импульсов, мажоритарном элементе 14 и сумматоре 15 по модулю два. На фиг. 2 обозначены первый и второй выходы 16, 17 блока 1.

Блок 5 промежуточной памяти может быть выполнен, например, на буферных регистрах, число которых равно числу счетчиков 4, и тактирующем их генераторе тактовых импульсов, частота которых отличается от частоты генератора 13.

Блок 9 управления выполнен (см. фиг. 3) на первом-четвертом формирователя 18-21 импульсов, первом и втором триггерах 22, 23 и элементе 24 задержки. На фиг. 3 обозначены первый и второй входы 25, 26 и первый, второй выходы 27, 28.

Регистратор 8 может быть любым (индикатором, печатающим устройством и т. п. ) с выходом готовности.

Формирователи 18-21 блока 9 управления и формирователь 7 представляют собой любые схемы ждущих мультивибраторов.

Устройство для обнаружения и регистрации ошибок дискретного канала передачи и накопления информации работает следующим образом.

В качестве входного сигнала для оценки помехозащищенности дискретного канала передачи и накопления информации, как правило, используется тестовый сигнал, представляющий собой псевдослучайную последовательность импульсов, поступающих на вход регистра 11 блока 1 обнаружения ошибок. Сдвиг информации в регистре 11 осуществляется с помощью импульсов тактовой частоты, вырабатываемых генератором 13 тактовых импульсов, а длина регистра 11 соответствует длине псевдослучайной последовательности и равна n = 2k - 1, где k = 1, 2, . . . , i. Состояние регистра 11 анализируется в каждый момент времени, наступающий после очередного тактового импульса, группой 12 сумматоров по модулю два, количество сумматоров по модулю два в которой равно (n-1)/2 и которые подключены к соответствующим выходам регистра 11 [1] , и мажоритарным логическим элементом 14, результат голосования которого поступает на вход сумматора 15 по модулю два вместе (одновременно) с выходной информацией регистра 11. На выходе 16 блока 1 формируется поток ошибок, причем логической единице соответствует ошибка, а логическому нулю - отсутствие ошибки, в данном разряде входной информации.

Поток ошибок из блока 1 обнаружения ошибок поступает на регистр 1 сдвига, длина которого должна соответствовать максимальной априорной длине m пакета ошибок. С помощью импульсов тактовой частоты генератора 13 с выхода 17 блока 1 производится сдвиг потока ошибок в регистре 2 сдвига. Выходы всех разрядов регистра 2 сдвига поступают на элементы 3 И, причем на элемент 3.1 И поступает сигнал с выходов l-го разряда регистра 2 сдвига, что соответствует прохождению каждой ошибки; на элемент 3.2 И поступают сигналы с выхода 1-го и 2-го разрядов регистра 2 сдвига, что соответствует прохождению двойных ошибок, и т. д. На элемент 3. m И поступают сигналы с l-го и m-го разрядов регистра 2 сдвига, что соответствует прохождению пакета ошибок длины m. Выходные сигналы элементов 3 И, стробированные импульсами тактовой частоты с генератора 13, поступают на соответствующие счетчики 4, с помощью которых и подсчитываются количество одиночных 4.1, двойных 4.2 и т. д. до длины m (4. m) пакетных ошибок.

При заполнении какого-либо счетчика 4, а в случае равной длины всех счетчиков это будет счетчик 4.1, - сигнал переполнения этого счетчика поступит через элемент 6 ИЛИ на регистры блока 5 промежуточной памяти и в них запишется содержимое счетчиков 4. Сигнал с элемента 6 ИЛИ поступит также на вход формирователя 7, который сформирует короткий задержанный импульс и им произойдет обнуление счетчиков 4 в момент времени, когда информация из счетчиков 4 перепишется в блок 5.

Кроме того, сигнал с элемента 6 ИЛИ поступит на вход второго формирователя 19 импульсов блока 9 управления, который и запустит второй триггер 23 блока 9 управления, при срабатывании которого включается регистратор 8. Последний при этом выдаст сигнал готовности. Этот сигнал запустит первый формирователь 18, импульс с которого запустит первый триггер 22, сигнал с которого даст разрешение на перезапись информации с блока 5 промежуточной памяти на регистратор 8.

Время записи на регистраторе 8 задается с помощью элемента 24 задержки (схема таймера), запускаемого сигналом разрешения с триггера 22 через формирователь 20 импульсов. По окончании времени задержки сигнал с элемента 24 задержки, сформированный в короткий импульс с помощью формирователя 21, устанавливает в исходное положение триггеры 22, 23.

Таким образом, в рассматриваемом устройстве происходит сжатие информации об ошибках дискретного канала и передачи и накопления информации передач выдачей ее на регистратор, благодаря чему значительно повышается скорость регистрации, т. е. появляется возможность применить регистраторы с малым быстродействием, например цифропечать. (56) Колесник В. Д. , Мирончиков Е. Т. Декодирование циклических кодов. М. : Связь, 1966, с. 236-242.

Авторское свидетельство СССР N 593320, кл. H 04 L 1/24, 1974.

Авторское свидетельство СССР N 862375, кл. H 03 M 13/02, 1979.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения и регистрации ошибок дискретного канала передачи и накопления информации | 1988 |

|

SU1567078A1 |

| Устройство для обнаружения ошибок дискретного канала передачи информации | 1990 |

|

SU1777245A1 |

| МОДЕЛИРУЮЩИЙ КОАП | 2013 |

|

RU2516703C1 |

| Декодер мажоритарного двоичного кода | 1988 |

|

SU1566488A1 |

| Устройство для обнаружения и регистрации ошибок дискретного канала связи | 1980 |

|

SU974597A2 |

| Устройство для обнаружения и регистрации ошибок дискретного канала связи | 1979 |

|

SU862375A1 |

| УСТРОЙСТВО для ИСПРАВЛЕНИЯ ОШИБОК В КОДОВОЙКОМБИНАЦИИ | 1971 |

|

SU293243A1 |

| Пороговый декодер сверточного кода | 1982 |

|

SU1078654A1 |

| Тренажер радиотелеграфиста | 1983 |

|

SU1119057A1 |

| Кодек несистематического сверточного кода | 1990 |

|

SU1714812A1 |

Изобретение относится к вычислительной технике. Его применение в аппаратуре, предназначенной для статистических исследований каналов связи и накопления информации, позволяет повысить быстродействие устройства. Устройство содержит блок 1 обнаружения ошибок, регистр 2 сдвига, элементы 3 И, блок 5 промежуточной памяти, элемент 6 ИЛИ, формирователь 7 импульсов, регистратор 8, блок 9 управления и счетчик 4.1. Введение счетчиков 4.2 - 4. m, где m - максимальная длина пакетной ошибки, обеспечивает сжатие регистрируемой информации. 2 з. п. ф-лы, 3 ил.

Авторы

Даты

1994-02-15—Публикация

1985-09-30—Подача