л о

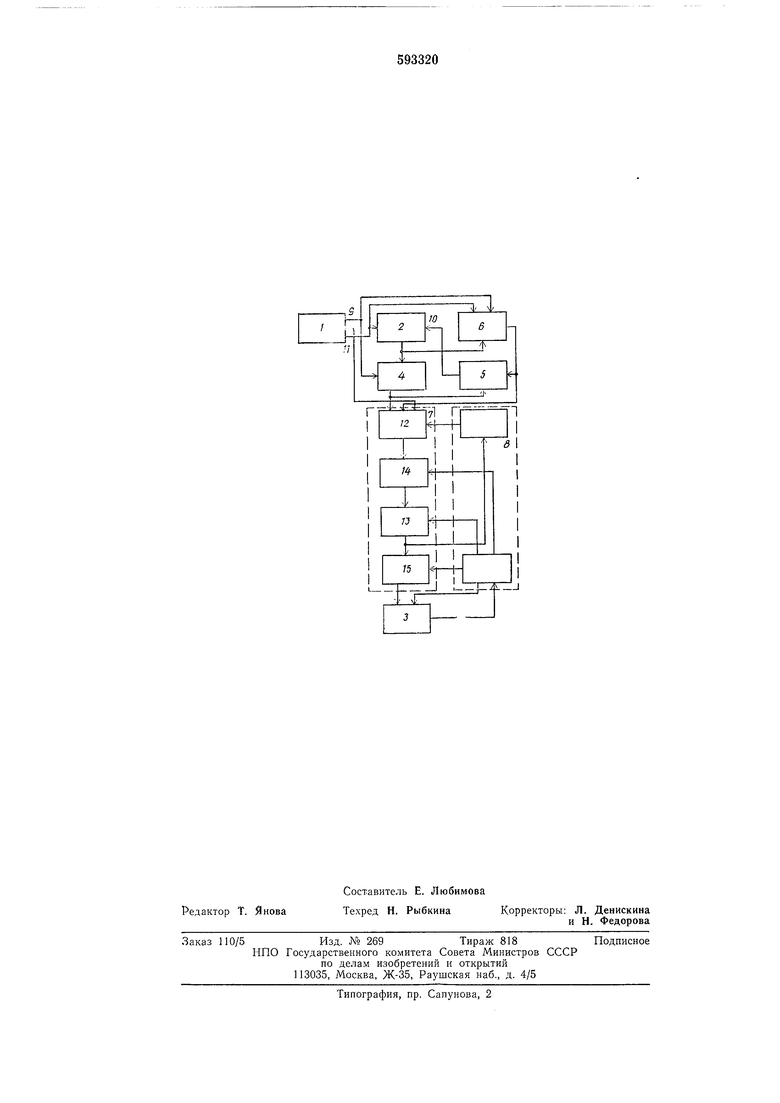

точной памяти подключен к входу регистратора 3, синхронизирующий выход последнего через блок 8 управления подключен к управляюш,им входам блока 7 промежуточной памяти и регистратора 3, кроме того, выход счетчика 2 тактовых импульсов подключен к одному из входов формирователя 6 временных меток, к двум другим входам которого подключены соответственно выход 9 «ошибка и тактовый выход блока 1 обнаружения оитибок, выход формирователя 6 временных меток подключен к входу 10 «Сброс счетчика 2 тактовых импульсов через элемент ИЛИ 5, к другому входу которого подключен выход блока

4ключей, а выход 11 «знак ошибки блока 1 обнаружения ошибок и выход формирователя

6 временных меток подключены к соответствуюш,пм входам блока 7 промежуточной памяти, состоящего из блока 12 оперативной иамяти, блока 13 буферной памяти и импульсных ключей 14 и 15.

Устройство работает следующим образом.

Тактовые импульсы поступают иа вход двоичного пятиразрядного счетчика 2, выход каждого разряда которого соединен с соответствующим импульсным ключом блока 4 ключей. С появлением сигнала ощибки все пять ключей этого блока открываются и двопчное число со счетчика 2, соответствующее номеру посылки, на которой происходит ошибка, записывается в пять ячеек блока 12 оперативпой памяти. Одновременно в седьмую ячейку блока 12 оперативной намяти записывается сигнал вида ощибок. При записи числа импульсами с выхода блока ключей 4 через элемент ИЛИ 5 производится сброс счетчика 2 в нулевое состояние. Принимаемые и анализируемые блоком 1 обнаружения ощибок элементарные посылки разбиваются на блоки по тридцать одной посылке. Для этого с ириходом каждой тридцать первой посылки формирователь 6 выдает и.мпульс отметки блока, который записывается в шестую ячейку блока 12 оиеративной памяти и через элемент ИЛИ

5устанавливает счетчик 2 в нулевое состояние.

В случае возникновения ошибки на тридцать первой посылке происходит запрет формирования импульса блоковой отметки сигналом ошибки, и в блок 12 оперативной памяти со счетчика 2 записывается число «тридцать один в двоичиом коде.

Регистратор 3 в каждом цикле своей работы выдает сигналы синхронизации, поступающие на блок 8 упр.авления. Последним в соответствующие моменты цикла работы регистратора 3 вырабатываются сигналы управления на перезапись информации из блока 12 оперативной памяти в блок 13 буферной иамятп через семь импульсных ключей 14, сигналы

4

управления на регистрацию информации из блока 13 буферной памяти на бумажную ленту регистратора 3 через семь импульсных ключей 15; сигналы на установку блока 13 буферной памяти в исходное состояние; сигналы транспортировки ленты па продвижение бумажной лепты регистратором 3.

При записи пиформации из блока 12 оперативной памяти в блок 13 буферной памяти блоком 8 управления вырабатывается сигнал на установку блока 12 оперативной памяти в исходное состояпие.

Такое взаимодействие узлов устройства позволяет исключить потерю информации при регистрации потока ощибок из-за совпадепия моментов записи информации в блок 12 оперативиой памяти с любым сигналом синхронизации регистратора 3.

Формула изобретения

Устройство для обнаружения и регистр.ации потока ошибок дискретного канала связи, содерл ащее на входе блок обнаружения ощибок, а также счетчик тактовых импульсов и регистратор, иапример, перфоратор, отличающееся тем, что, с целью обеспечения непрерывной регистрации с одиовременным сжатием потока ощпбок дискретного капала связи, введены блок ключей, элемент ИЛИ, формирователь временных меток, блок промежуточной памяти и блок уиравления, при этом тактовый выход блока обнаружения ощибок иодключен ко входу счетчика тактовых импульсов, выход которого через последовательно соединенные блок ключей, к другому входу которого подключен выход «ошибка блока обнаружения ошибок, и блок промежуточной памяти подключен ко входу регистратора, синхронизирующий выход которого через блок унравления нодключен к управляющим входам блока промежуточной памяти и регистратора, кроме того, выход счетчика тактовых импульсов подключен к одному из входов формирователя временных меток, к двум другим входам которого иодключеиы соответственно выход «ошибка и тактовый выход блока обнаружения ошибок, выход формирователя временных меток подключен ко входу «сброс счетчика тактовых импульсов через элемент Р1ЛИ, к другому входу которого подключен выход блока ключей, а выход «знак ошибки блока обнаружения ошибок и выход формирователя временных меток подключены к соответствующим входам блока промежуточной памяти.

Источники информации, иринятые во внимание ири экспертизе

1. Авторское свидетельство СССР № 224553, кл. И 04L 1/00, 1968.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения и регистрациипОТОКА ОшибОК диСКРЕТНОгО КАНАлА СВязи | 1979 |

|

SU836804A2 |

| Устройство для обнаружения и регистрации ошибок дискретного канала связи | 1980 |

|

SU974597A2 |

| УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ И РЕГИСТРАЦИИ ОШИБОК ДИСКРЕТНОГО КАНАЛА ПЕРЕДАЧИ И НАКОПЛЕНИЯ ИНФОРМАЦИИ | 1985 |

|

SU1378757A1 |

| Устройство для обнаружения и регистрации ошибок дискретного канала связи | 1979 |

|

SU862375A1 |

| Устройство для обнаружения и коррекции ошибок | 1986 |

|

SU1372367A1 |

| Устройство для обнаружения и регистрации ошибок дискретного канала передачи и накопления информации | 1988 |

|

SU1567078A1 |

| Устройство синхронизации по циклам | 1976 |

|

SU618858A1 |

| УСТРОЙСТВО для ИСПРАВЛЕНИЯ ОШИБОК ПРИ ИТЕРАТИВНОМ КОДИРОВАНИИ | 1969 |

|

SU251253A1 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| Анализатор кодовых последовательностей импульсов (его варианты) | 1984 |

|

SU1238243A1 |

Авторы

Даты

1978-02-15—Публикация

1974-08-20—Подача