(54) УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ И РЕГИСТРАЦИИ ОШИБОК ДИСКРЕТНОГО КАНАЛА СВЯЗИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения и регистрации ошибок дискретного канала связи | 1980 |

|

SU974597A2 |

| Устройство для обнаружения и регистрации ошибок дискретного канала передачи и накопления информации | 1988 |

|

SU1567078A1 |

| УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ И РЕГИСТРАЦИИ ОШИБОК ДИСКРЕТНОГО КАНАЛА ПЕРЕДАЧИ И НАКОПЛЕНИЯ ИНФОРМАЦИИ | 1985 |

|

SU1378757A1 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1988 |

|

SU1596464A1 |

| УСТРОЙСТВО АДАПТИВНОГО КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ | 2000 |

|

RU2169431C1 |

| Динамическое запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1133625A1 |

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

| Устройство для измерения параметровпОМЕХОуСТОйчиВОСТи диСКРЕТНыХ блОКОВ | 1979 |

|

SU841012A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| Устройство для моделирования канала передачи дискретной информации | 1985 |

|

SU1273943A1 |

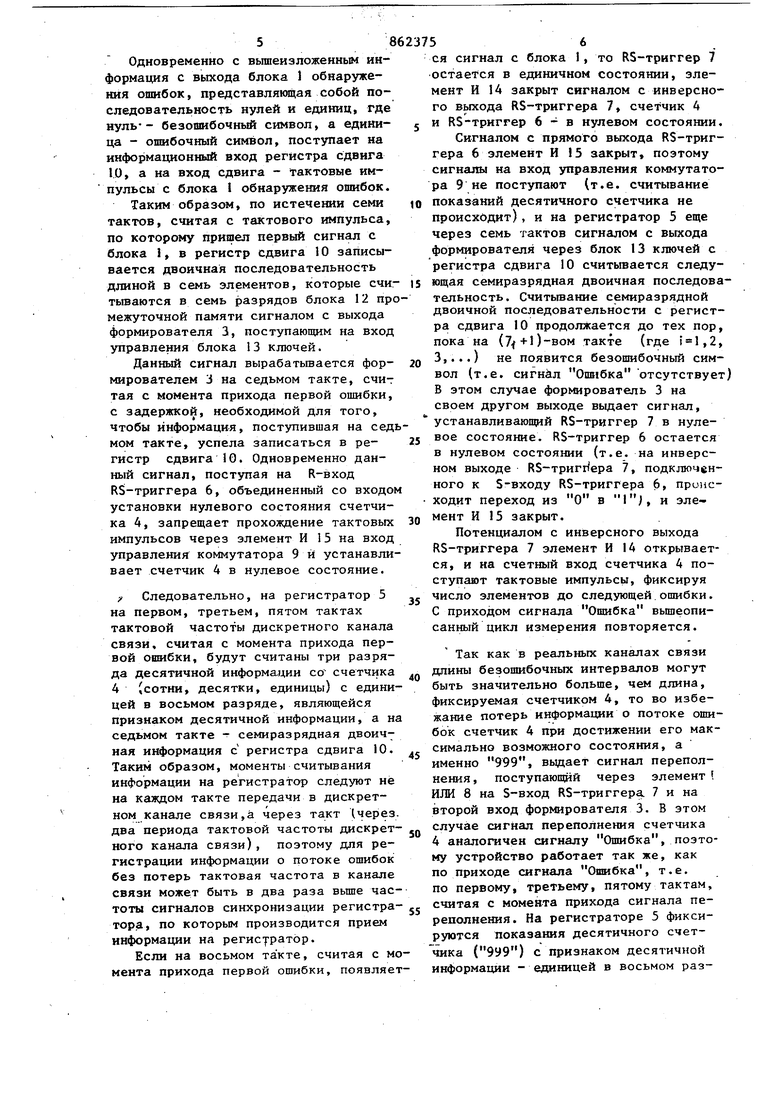

Изобретение относится к технике .электросвязи и может использоваться в аппаратуре для статического исследования дискретных каналов связи, Известно устройство для обнаружения и регистрации ошибок дискретного ка1нала связи, содержащее счетчик, элемент ИЛИ, блок ключей, блок обнар жения ошибок, первый выход которого соединен с одним входом формировател последовательно соединенные блок про межуточной памяти, регистратор и бло управления, один выход которого соединен с другим входом регистратора, а другие выходы соединены с входами блока промежуточной памяти i . Однако известное устройство работает с небольшой скоростью. Цель изобретения - повышение скорости регистрации потока опюбок. Для этого в устройство для обнару жения и регистрации ошибок дискретного канала связи, содержащее счетчик, элемент ИЛИ, блок ключей, блок обнаружения ошибок, первый выход которого соединен с одним входом формирователя, последовательно соединенные блок промежуточной памяти, регистратор и блок управления, один выход которого соединен с другим входом регистратора, а другие выходы соединены с входами блока промежуточной памяти, введены два элемента И, два, RS-триггера, блок элементов ИЛИ, коммутатор и регистр сдвига, причем первые входы элементов И соединены с первым выходом блока обнаружения ошибок, второй выход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом счетчика и с одним входом регистра сдвига, другой вход которого соединен с первым выходом блока обнаружения ошибок, а выходы через блок ключей соединены с одними входами блока элементов ИЛИ, другие входы которого через коммутатор соединены с выходами счетчика, первый вход KQ3foporo соединен с выходом первого элемента И, а второй вход - с одним выходом формирователя, соединенным также с соответствующим входом блока ключей и R-входом первого.К5-триг гера, S-вход которого соединен с выходом второго RS-триггера, соединенным также со вторым входом первого элемента И, выход элемента ИЛИ соединен с S-входом второго RS-триггера и другим входом формирователя, другой выход которого соединен с R-Bxof oM второго RS-триггера, выход первого RS TpHrrepa соединен со вторым входом второго элемента И выход которого соединен с соответствующим входом.коммутатора. Йри этом, вькоды блока элементов ИЛИ соединены со входами блока промежуточной памяти. На чертеже представлена структурная электрическая схема предложенного устройства. Устройство для обнаружения и регистрации ошибок дискретного канала связи содержит блок 1 обнаружения ошибок, блок 2 управления, формирова тель 3, счетчик 4, регистратор 5, RS-триггеры 6,7, элемент ШШ 8, коммутатор 9, регистр сдвига 10, блок П элементов ИЛИ, блок 12 промежуточ ной памяти, блок 13 ключей, элементы И 14,15, причем RS-триггеры имеют R-вход и S-вход. Устройство работает следующим образом. В случае отсутствия ошибок в последовательности, поступающей с блока 1 обнаружения ошибок, тактовые импульсы через элемент И 14, на второй вход которого подается разрешающий сигнал с инверсного выхода RS-триггера 7, поступают на счетный вход счетчика 4, который подсчитывает дли ну безошибочного интервала .(число беэошибочньпс символов между ошибочными) , а потенциалом с прямого выход RS-триггера 6, находящегося в нулевом состоянии, запрещается прохождение тактовых импульсов с блока 1 обн ружения ошибок через элемент И 15 на вход управления коммутатора 9. При появлении на выходе блока 1 обнаружения ошибок сигнала ошибки п ледний, поступая через элемент ИЛИ 8 на S-вход RS-тригг-ера 7,устанавливает его в единичное состояние Поступая на вход формирователя 3, о разрешает формирование сигнала чере семь тактов после поступления сигнала с блока 1, а по заднему фронту сигнала с инверсного выхода RS-триггера 7 (т.е. при переходе уровня на инверсном выходе RS-триггера 7 из в О) RS-триггер 6 устанавли ваетс,т в единичное состояние. В результате этого потенциалом с инверсного выхода RS-триггера 7 штрещается прохождение тактовых импульсов через элемент И 14 на счетный вход счетчика 4, а сигналом с прямого выхода RS-триггера 6 открывается элемент И 15, и тактовые импульсы с блока 1 обнаружения ошибок, поступая на вход управления коммутатора 9, разрешают считывание показаний десятичного счетчика через блок I1 элементов ИЛИ в блок 12 промежуточной памяти и далее, с помощью блока 2 управления, в регистратор 5, Блок 12 проме,1суточной памяти и блок 2 управления служат для исключения потери информации из-за несовпадения моментов вьщачи информации с сигналами синхронизации регистратора 5. Регистратор в каждом цикле своей работы выдает сигналы синхронизации, поступающие на блок 2 управления. Последний в соответствующие моменты цикла работы регистратора 5 вырабатывает сигналы управления на регистрацию ииформации из блока 12 промежуточной памяти на бумажную ленту регистратора, сигналы транспортировки на продвижение бумажной ленты регистратора 5. Считьюание показаний счетчика 4 осуществляется по первому, третьему и пятому тактовьм импульсам, считая с тактового импульса, по которому пришел сигнал с блока 1 через элемент ШШ 8 на вход формирователя 3, т.е. частота считывания десятичной информации на регистрирующее устройство в раза ниже тактовой частоты в дискретном канале связи. Таким образом, на первом, третьем и пятом тактах, считая с момента прихода сигнала с блока I, происходит считывание сотён, десятков и единиц (10, Ю , 10°) со счетчика 4 , IV/ , IU / со счетчика 4 в четыре разряда блока 12 промежуточной памяти, так как каждому десятичному разряду соответствуют четыре двоичных разряда3 () . Признаком десятичной информации служит запись единицы в восьмой разряд блока 12 Промежуточной памяти.

Одновременно с вышеизложенным информация с выхода блока 1 обнаружения ошибок, представляющая собой последовательность нулей и единиц, где нуль-- безошибочный символ, а единица - ошибочный символ, поступает на информационный вход регистра сдвига 10, а на вход сдвига - тактовые импульсы с блока I обнаружения ошибок.

Таким образом, по истечении семи тактч5В, считая с тактового импульса, по которому пришел первый сигнал с блока i, в регистр сдвига 10 записывается двоичная последовательность длиной в семь элементов, которые считьшаются в семь разрядов блока 12 про межуточной памяти сигналом с выхода формирователя 3, поступающим на вход управления блока 13 ключей. Данный сигнгш вырабатьшается формирователем 3 на седьмом такте, счит тая с момента прихода первой ошибки, с задержкой, необходимой для того, чтобы информация, поступившая на седь мом такте, успела записаться в регистр сдвига 10. Одновременно данный сигнал, поступая на R-вход RS-триггера 6, объединенный со входом установки нулевого состояния счетчика 4, запрещает прохождение тактовых импульсов через элемент И 15 на вход управления коммутатора 9 и устанавливает счетчик 4 в нулевое состояние. f Следовательно, на регистратор 5 на первом, третьем, пятом тактах тактовой частоты дискретного канала связи, считая с момента прихода первой ошибки, будут считаны три разряда десятичной информации со счетчика 4 (сотни, десятки, единицы) с единицей в восьмом разряде, являющейся признаком десятичной информации, а на седьмом такте - семиразрядная двоич ная информация с регистра сдвига 10. Таким образом, моменты считывания информации на регистратор следуют не на каждом такте передачи в дискретном канале связи,а через такт чepeз. два периода тактовой частоты дискретного канала связи) , поэтому для регистрации информации о потоке ошибок без потерь тактовая частота в канале связи может быть в два раза вьште частоты сигналов синхронизации регистратора, по которым производится прием информации на perHCfpaTop. Если на восьмом такте, считая с мо мента прихода первой ошибки, появляет

ся сигнал с блока 1, то RS-триггер 7 остается в единичном состоянии, элемент И 1А закрыт сигналом с инверсного вьпсода RS-триггера 7, счетчик 4

и RS-триггер 6 - в нулевом состоянии. Сигналом с прямого выхода RS-триггера 6 элемент И 15 закрыт, поэтому сигналы на вход управления коммутатора 9 не поступают (т.е. считывание

показаний десятичного счетчика не происходит), и на регистратор 5 еще через семь тактов сигналом с выхода формирователя через блок 13 ключей с регистра сдвига 10 считьгоается следующая семиразрядная двоичная последовательность. Считьгаанне семиразрядной двоичной последовательности с регистра сдвига 10 продолжается до тех пор, пока на ()-вом такте (где i l,2, 3,...) не появится безошибочный символ (т.е. сигнал Ошибка отсутствует) В этом случае формирователь 3 на своем другом выходе выдает сигнал, устанавлнвающнй RS-триггер 7 в нулевое состояние. RS-триггер 6 остается в нулевом состоянии (т.е. на инверсном выходе RS-TpHrriepa 7, подключенного к S-ВХОДУ RS-триггера 6, происходит переход из О в , и элемент И 15 закрыт. Потенциалом с инверсного выхода RS-триггера 7 элемент И 14 открывается, и на счетный вход счетчика 4 поступают тактовые импульсы, фиксируя число элементов до следующей.ошибки. С приходом сигнала Ошибка вьш1еописанный цикл измерения повторяется. Так как в реальных каналах связи длины безошибочных интервалов могут быть значительно больше, чем длина, фиксируемая счетчиком 4, то во избежание потерь информации о потоке ошибок счетчик 4 при достижении его максимально возможного состояния, а именно 999, выдает сигнал переполнения , поступающий через элемент ИЛИ 8 на S-вход RS-триггера 7 и на второй вход формирователя 3. В этом случае сигнал переполнения счетчика 4 аналогичен сигналу Ошибка, поэтому устройство работает так же, как по приходе сигнала Ошибка, т.е. по первому, третьему, пятому тактам, считая с момента прихода сигнала переполнения. На регистраторе 5 фиксируются показания десятичного счетчика (999) с признаком десятичной информации - единицей в восьмом разряде, а на седьмом такте считывается двоичная информация из регистра сдвига 10.

Таким образом, предложеииое устройство позволяет без потерь производить регистрацию потока ошибок, поступающего со скоростью, в два раза превышающей скорость регистрации ошибок известным устройством.

Формула изобретения

Устройство для обнаружения и регистрации ошибок дискретного канала связи, содержащее счетчик, элемент ИЛИ, блок ключей, блок обнаружения ошибок, первый выход которого соединен с одним входом формирователя,

последовательно соединенные блок промежуточной памяти, регистратор и ёлок управления, один выход которого соединен с другим входом регистратора, а другие выходы соединены с входами блока промежуточной памяти, о т л ичаю-щееся тем, что, с целью повышения скорости регистрации потока ошнбдк, введены два элемента И, два RS-триггера, блок элементов ШШ, коммутатор и регистр сдвига, причем первые входы элементов И соединены с первым выходом блока обнаружения ошибок, второй выход которого соединен с первым входом элемента ШШ, второй

вход которого соединен с выходом счетчика и с одним входом регистра сдвига, другой вход которого соединен с первым выходом блока обнаружения ошибок, а выходы через блок ключей соединены с одними входами блока элементов ИЛИ, другие входы которого через коммутатор соеданены с выходами счетчика, первый вход которого соединен с выходом первого элемента И, а второй вход. - с одним выходом формирователя, соединенным также с соответствукшщм входом блока ключей и R-входом первого RS-триггера, Ь-вход которого соединен с выходом второго RS-триггера, соединенным также со вторьа4 входом первого элемента И, выход элемента ИЛИ соединен с S-BXOдом второго RS-триггера и другим входом формирователя, другой выход которого соединен с R-входом второго RS-триггера, выход первогоoRSтриггера соединен со вторьв4 входом второго элемента И, выход которого , соединен с соответствукицим входом коммутатора, при этом выходы блока элементов ШШ соединены со входами блока промежуточной памяти.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1981-09-07—Публикация

1979-10-12—Подача