(54) ИНТЕГРАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Операционный усилитель с периодической компенсацией смещения нуля | 1982 |

|

SU1024938A1 |

| Интегратор | 1979 |

|

SU834715A1 |

| ИНТЕГРАТОР | 1990 |

|

RU2020580C1 |

| Интегратор | 1983 |

|

SU1088017A1 |

| Квадратор | 1982 |

|

SU1084824A1 |

| Интегратор | 1981 |

|

SU1029187A1 |

| Интегратор | 1978 |

|

SU748439A1 |

| ИНТЕГРАТОР С ОБНУЛЕНИЕМ | 1991 |

|

RU2015556C1 |

| Интегратор | 1986 |

|

SU1401485A2 |

| Интегратор | 1978 |

|

SU855674A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в автоматических регуляторах, моделирующих устройствах.

Известен интегратор с большой постоянной времени интегрирования, содержащий операционный усилитель, накопительный электролитический конденсатор, резисторы,опорный источник, стабилитрон Г11.

Недостаток этого интегратора состоит в том, что электролитический конденсатор не обеспечивает стабильности постоянной времени в диапазоне температур и во времени.

Наиболее близок по технической сущности к предлагаемому интегратор, содержащий операционный усилитель (ОУ), накопительный конденсатор, включенный между инвертирующим входом и выходом ОУ, соединенные последовательно ключ и масштабный резистор, включенные между инвертирующим входом ОУ и шиной нулевого потенциала,- и цепочка из последовательно включенных второго масштабного резистора и второго ключа, включенная между ОУ и источником входного сигнала С2.

Недостаток известного интегратора - небольшая; точностьиз-за нарушения балансировки ОУ при переклю5 чении ключей.

Цель изобретения - повышение точности интегрирования.

Поставленная цель достигается тем, что интегратор, содержащий опера10ционный усилитель, инвертирующий вход которого через последовательно соединенные первый и второй мае-, штабные резисторы и первый ключ соединен с шиной нулевого потенциала

15 и через интегрирующий конденсатор подключен к выходу операционного усилителя, являющемуся выходом интегратора, а неинвертирующий вход операционного усилителя соединен с пер20вым выводом третьего масштабного резистора, и второй ключ, один из выводов которого является входом интегратора, содержит четвертый и пятый масштабные резисторы, причем

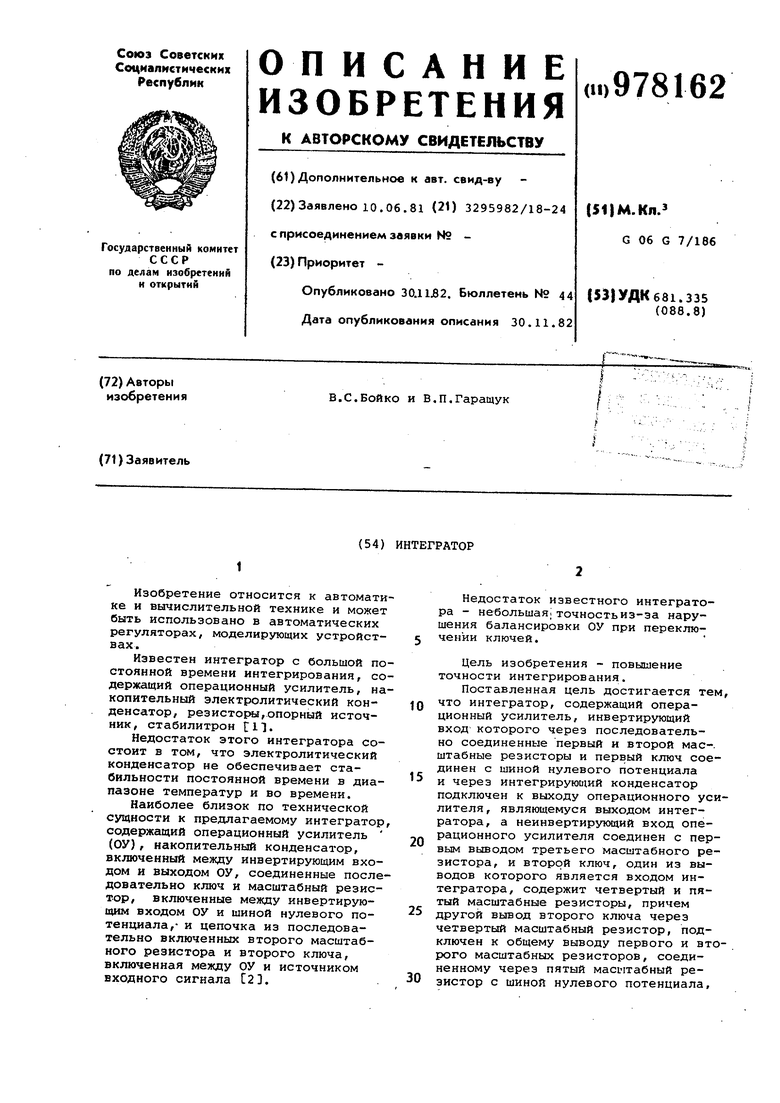

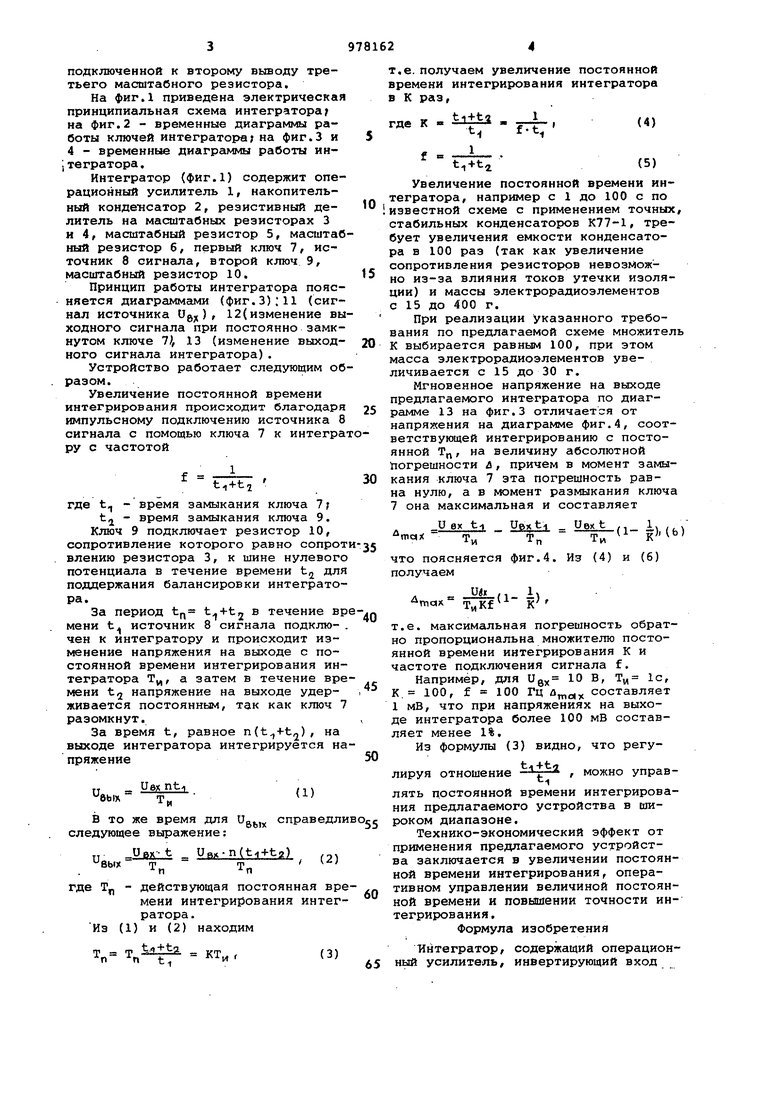

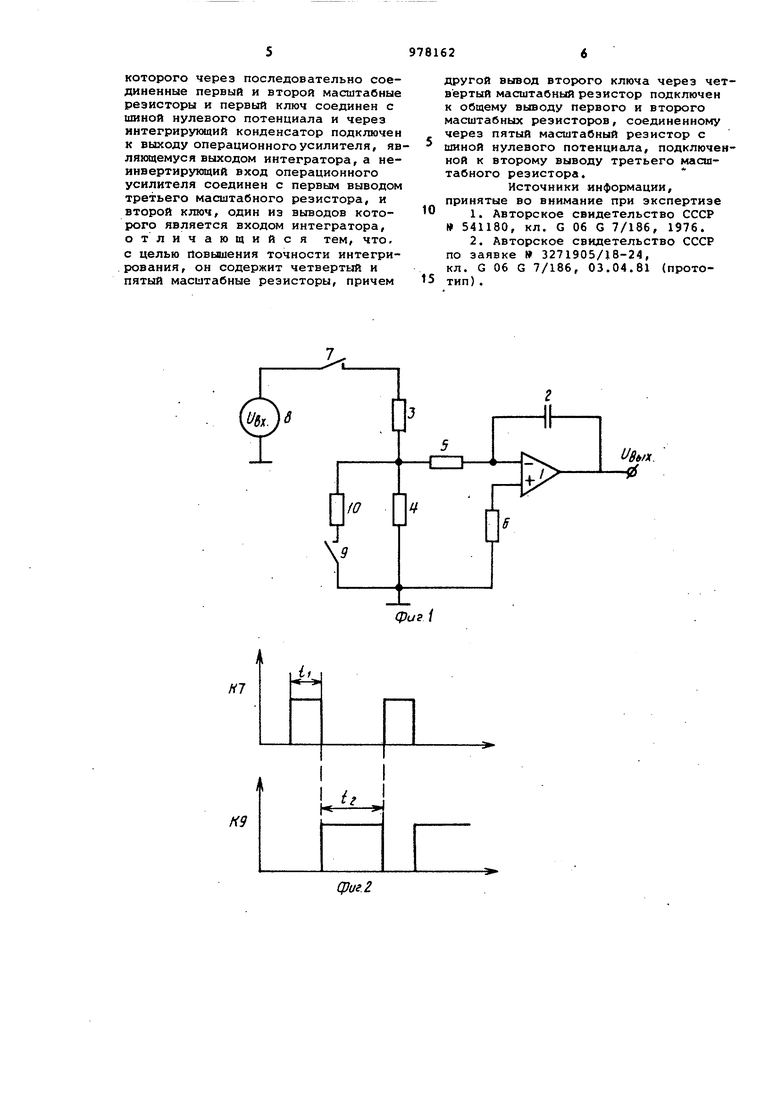

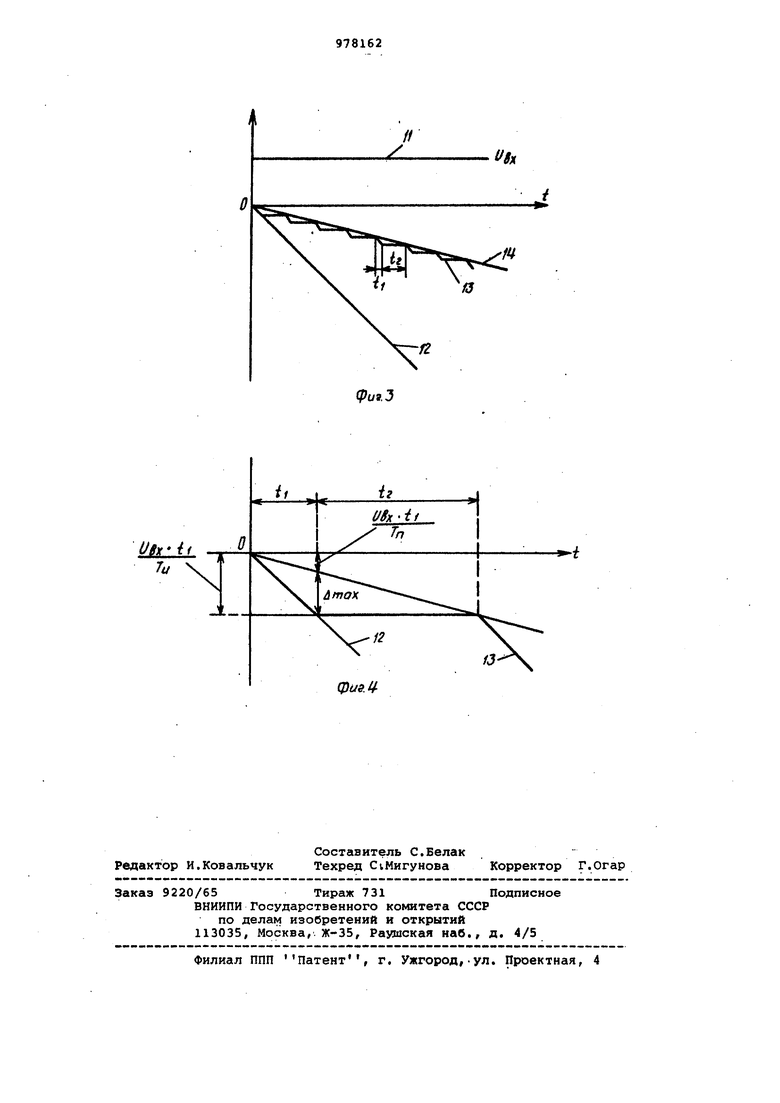

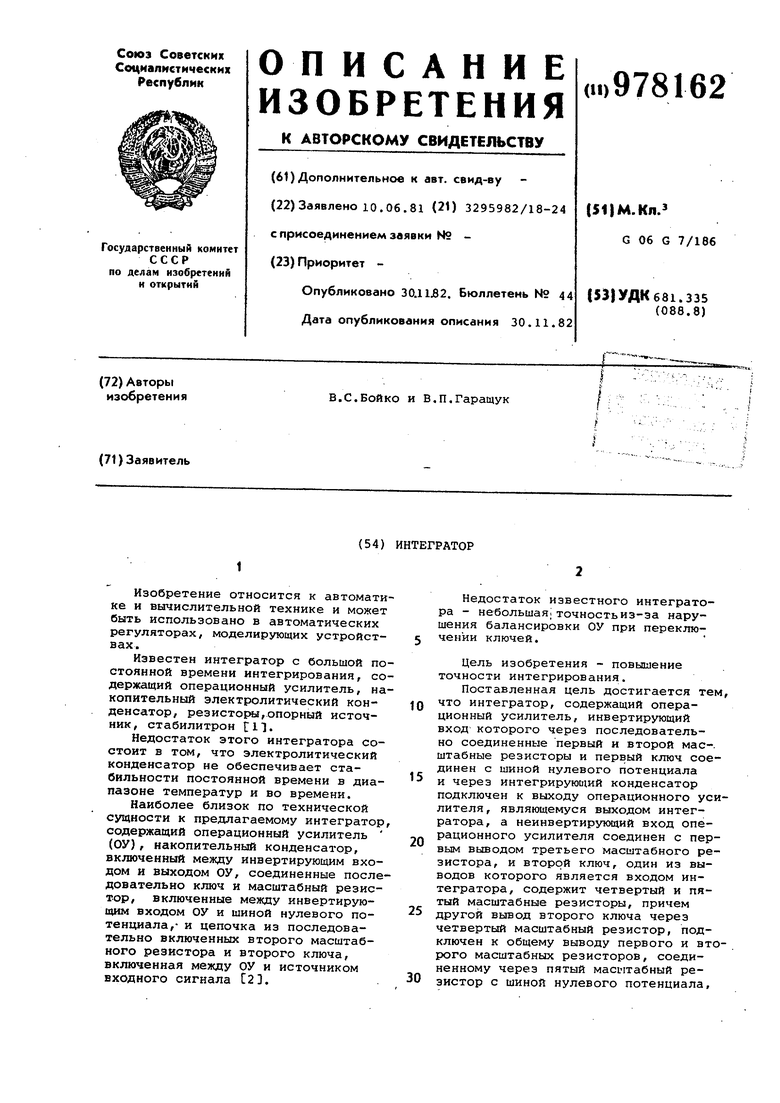

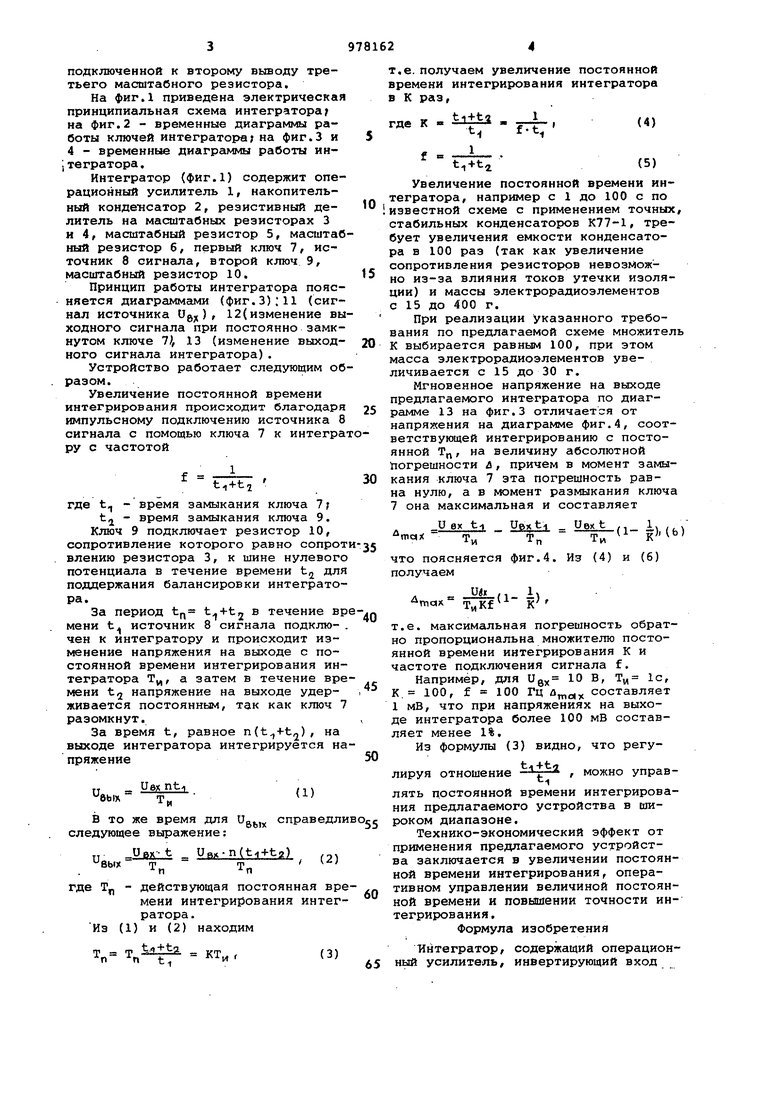

25 другой вывод второго ключа через четвертый масштабный резистор, подключен к общему выводу первого и второго масштабных резисторов, соединенному через пятый мас1чтабный ре30зистор с шиной нулевого потенциала. подключенной к второму выводу третьего масштабного резистора, На фиг.1 приведена электрическая принципиальная схема интегратора на фиг.2 - временные диаграммы работы ключей интегратора; на фиг.З и 4 - временные диаграммы работы ин|тегратора. Интегратор {фиг.1) содержит операционный усилитель 1, накопительный конде нсатор 2, реэистивный делитель на масштабных резисторах 3 и 4, масштабный резистор 5, масштаб ный резистор б, первый ключ 7, источник 8 сигнала, второй ключ 9, масштабный резистор 10. Принцип работы интегратора поясняется диаграммами (фиг.З);11 (сигнал источника Ugj() , 12(изменение вы ходного сигнала при постоянно замкнутом ключе 1), 13 (изменение выходного сигнала интегратора). Устройство работает следующим об разом. Увеличение постоянной времени интегрирования происходит благодаря импульсному подключению источника 8 сигнала с помощью ключа 7 к интегра ру с частотой время замыкания ключа 7 f время замыкания ключа 9. Ключ 9 подключает резистор 10, сопротивление которого равно сопрот влению резистора 3, к шине нулевого потенциала в течение времени t, для поддержания балансировки интегратора. За период t в течение ap мени t источник 8 сигнала подключен к интегратору и происходит изменение напряжения на выходе с постоянной времени интегрирования интегратора Ту,, а затем в течение вре мени t,2 напряжение на выходе удерживается постоянным, так как ключ 7 разомкнут. За время t, равное n(,j), на выходе интегратора интегрируется на пряжение и ах nt. В то же время для и, справедли след5пощее выражение: ивх t Uflx-n() ТпТ„ где Т - действующая постоянная вре мени интегрирования интегратора. Из (1) и (2) находим т.е. получаем увеличение постоянной времени интегрирования интегратора в К раз. tl+t . где К « Увеличение постоянной времени интегратора, например с 1 до 100 с по известной схеме с применением точных, стабильных конденсаторов К77-1, требует увеличения емкости конденсатора в 100 раз (так как увеличение сопротивления резисторюв невозможно из-за влияния токов утечки изоляции) и массы электрорадиоэлементов с 15 до 400 г. При реализации указанного требования по предлагаемой схеме множитель К выбирается равным 100, при этом масса электрорадиоэлементов увеличивается с 15 до 30 г. Мгновенное напряжение на выходе предлагаемого интегратора по диаграмме 13 на фиг.З отличается от напряжения на диаграмме фиг.4, соответствующей интегрированию с постоянной Tf,, на величину абсолютной погрешности л, причем в момент замыкания ключа 7 эта погрешность равна нулю, а в момент размыкания ключа 7 она максимальная и составляет U ах ti Uex ti Uex t . 1.. -mmrp.. - K VD J Ти И n что поясняется фиг.4. Из (4) получаем к т.е. максимальная погрешность обратно пропорциональна множителю постоянной времени интегрирования К и частоте подключения сигнала f. Например, для Ugx 10 В, Ту, 1с, К. 100, f 100 Гц составляет 1 мВ, что при напряжениях на выходе интегратора более 100 мВ составляет менее 1%. Из формулы (3) видно, что регуti+tjлируя отношение можно управлять постоянной времени интегрирования предлагаемого устройства в широком диапазоне. Технико-экономический эффект от применения предлагаемого устройства заключается в увеличении постоянной времени интегрирования, оперативном управлении величиной постоянной времени и повышении точности интегрирования . Формула изобретения Интегратор, содержащий операционный усилитель, инвертирующий вход

которого через последовательно соединенные первый и второй масштабные резисторы и первый ключ соединен с шиной нулевого потенциала и через интегрирующий конденсатор подключен к выходу операционного усилителя, являющемуся выходом интегратора, а неинвертирующий вход операционного усилителя соединен с первым выводом третьего масштабного резистора, и второй ключ, один из выводов которого является входом интегратора, отличающийся тем, что, с целью Повышения точности интегрирования, он содержит четвертый и пятый масштабные резисторы, причем

другой вывод второго ключа через четвертый масштабный резистор подключен к общему вьтоду первого и второго масштабных резисторов, соединенному через пятый масштабный резистор с шиной нулевого потенцигша, подключенной к второму выводу третьего масштабного резистора.

Источники информации, принятые во внимание при зкспертизе

0

кл. G 06 G 7/186, 03.04.81 (прото5тип) .

ii

HI

//

Авторы

Даты

1982-11-30—Публикация

1981-06-10—Подача