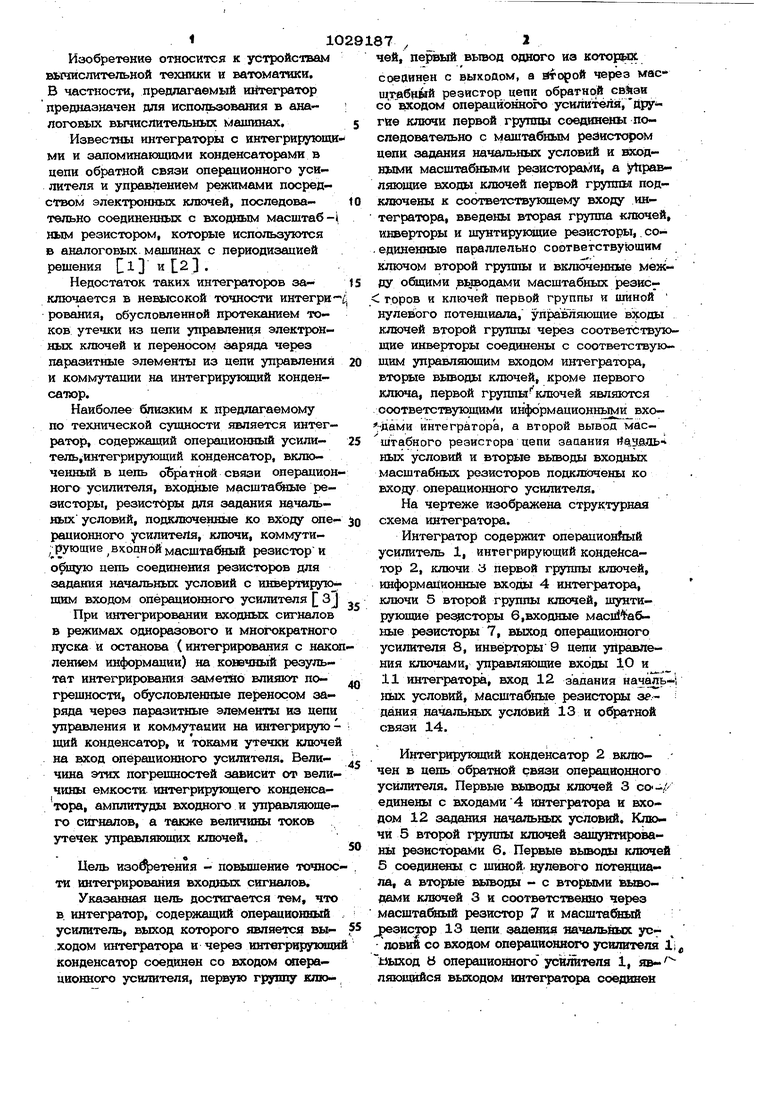

1 Изобретение относится к устройствам иьгаислитепьной техники и ватоматикк. В частности, предлагаемый интегратор предназначен для использования в аналоговых вычислительных машинах. Известны интеграторы с интегрирующи ми и запоминакяцими конденсаторами в цепи обратной связи операционного усилителя и управлением режимами посредством электронных ключей, последовательно соединенных с входным масштабным резистором, которые используются в аналоговых машинах с периодизацией решения . Недостаток таких интеграторов заключается в невысокой точности интегри- рования, обусловленной протеканием токов утечки из цепи управления электронных кгаочей и переносом заряда через паразитные элементы из цепи управления и коммутации на интегрирукшшй конденса-вор. Наиболее близким к предлагаемому по технической сущности является интегратор, содержащий операционный усилитель.интегрирующий конденсатор, включенный в цепь обратной связи операцион ного усилителя, масштабные резисторы, резисторы для задания начальных условий, подалюченные ко входу one рационного усилителя, ключи, коммути рующие вкоаноймасштабиый резистори общую цепь соединения резисторов для задания начальных условий с инвертирую шим входом операционного усилителя 3j При интегрировании входных сигналов в режимах одноразового и многократного пуска и останова ( интегрирования с нако лением информации) на конечный результат интегрирования заметно влияют погрешности, обусловленные переносом заряда через паразитные элементы из цепи управления и коммутации на интегрирую щий конденсатор, и токами утечки ключе на вход операционного усилителя. Величина этих погрешностей зависит от величины емкости интегрирующего конденсатора, амплитуды входного и управляющего сигналов, а также величины токсж утечек управляющих ключей. Цель изофетения - повышение точное ти интегрирования входных сигналов. Указанная цель достигается тем, что в интегратор, содержащий операционный усилитега, выход которого является выходом интегратора и через интегрирующи конденсатор соединен со входом «lepa- ционногю усилителя, первую группу клю7чей, первый вывод одного из которых соединен с выходом, а агорой через маеш,т-а6вмй резистор цепи обратной свйаи СОБХОДОМ операционного усилителя,Другие первой группы соединены последовательно с маштабным резистором цепи задания начальных условий и ншдвыми масштабными резисторами, а управляющие входы ключей первой группы подключены к соответствующему входу интегратора, введены вторая группа ключей, инверторы и шунтирукацие резисторы,. соединенные параллельно соответствующим ключом второй группы и включенные менеВУ общими вьтодами масштабных резисгоров и ключей первой группы и шиной нулевого потенциала, управ пяющие входы ключей второй группы через соответствующие инверторы соединены с соответствующим управляющим входом интегратора, вторые вьшоды ключей, кроме первого ключа, первой группи ключей являются соответствующими информационными вхо-дами интегратора, а второй вывод мае- штабного резистора цепи зааання йазйЦЬных условий и вторые выводы входных масштабных резисторов подключены ко входу операционного усилителя. На чертеже изображена структурная схема интегратора. Интегратор содержит операцион&ый усилитель 1, интегрирующий кондейсатор 2, ключи 3 первой группы ключей, информационные входы 4 интегратора, ключи 5 второй группы ключей, шунтирующие реа асторы 6,входные мас1Й абные резисторы 7, выход операционного усилителя 8, инверторы 9 цепи управления ключами, управляющие входы 10 и 11 интегратора, вход 12 задания начешь-Г ных условий. Масштабные резисторы зеДания начальных условий 13 и обратной связи 14. Интегрирукмций конденсатор 2 вклю- чен в цепь обратной связи операционного усилителя. Первые выводы ключей 3 единены с входами 4 интегратора и входом 12 задания начальных условий. Ключи 5 второй группы ключей защутетироватл резисторами 6, Первые выводы ключей 5 соединшы с шиной, кулевого потенциала, а вторые выводы - с вторыми выводами ключей 3 и соответственно через масштабный резистор 7 и масштабный юзистор 13 цепи эааенкя начальных условий со входом операционного усюштепя 1;, ыход tt операционного усилйтепя 1, лякяцийся выходом (штегратора соединен

1О291874

с вьшодом одного из ключей 3чальаык условий анапоппва работе клкьпервой rfywOA ключей. Управляющие вхо . чей по входам 4. Во щ)емя перехориюго ПЫ ключей 3 и 5 ввлючеьы в npoi:«roo пршесса, когда ключи 3 я 5 неполвостью

фазе через иаверторы 9, Входы шсверхо- замкнуты, токи утечки и паразтшью соров 9 соединены с зшравлякшоши вхощвмн. s тавляющие сигнала из цепей управления Ю и 15. Интех фор cofiepHoiT июсколысоЦИ) „ вхояов 4. Рассмотрим работу схемы оо одному входу. Интегратор работает следующим об разом. При интеи нжрованисЕ входного сигвала, последний через входной аналогок юпоч 3 поступает на входной резистор 7 и шл зывает протекание тока через «trti irfapyiO ший конд сатор 2. При этом ToKtt Г вчки от цепи управления ключей 3 и 5, и дополнительный сипюл, обусловленный I переносом заряда через паразитные составлякшие емкостей из цепей управ- ления и коммутации аналогсжых ключей на иЕстегрирующий ксюденсатор, шунтирую тся низкоомными входными цепями и сопротивлением замкнутого ключа 3. Аналоговый ключ 5 в режиме интегрирования разомкнут. В режиме хрешения инфс ыации аналоговый ключ 3 размыка ется, а аналоговый клюЧ 5 замыкается, и это приводит к тому, что токи утечки от цепи управления и дополнительньй парази-гаый сигнал из цепей управления и коммутации аналоговых ключей щуНтя руютря на ШИНУ нулевого потенциала; вязКИМ сопротивлением замкнутого аналоговсячэ ключа 5. В реткиме licxoRBoe состояние Е цепи задания начальных услсивий ю ксоду 12 ключи 3 открыты, (а ключи 5 зёж|ялты, и инте1 1 1сшщй ковЛенсатор 2 аа ряжается инвертором начальных услсюий до величины, равной минус Uex НУ. При интегрировании и хранении ииформадии в цепи задания начальных условий клю чя. 5 oTK pabmii, а ключи 3 закрыты. Рахуга ключей схемы в цепи задания на коммутации щунтируются на шину потешила через дозюлнительный езистор 6. перенос заряда через парактаоые элементы ключей на интегрирую ий кящевсатор и токи утечки ключей а вход операционного усилителя удут .. инимальны и не повли51ют на конечный езультат интегрирования. в предлагаемом устройстве за счет введения небольшого числа дополшссельных элементов и установки на входе схемы вваяаговоро ключа удается увеличить точность как режиме одноразового, так и в режиме мнсг жратяого ToycfSu и остаHoiB (интегрирсшашсе с накохшением информации) путем умшоашения погрешностей, о словл шых переносом через паразитяые элементы из ueira управления и Коммутации на интегрирующий конденсатор и токами утечки ключей на вход ооерационного усилителя. Испытывается макет блока БИ-41. .Резулх заты испытаний показывают, что в режиме MHoroKpaTHofo пуска и останова (интегрирования с накоплением (гаформа ции) величины погрешности интегр«фования дгш разных ТСС-цшючек находятся на уров;не погршиностей бпока БИ-31, работающего в режиме одноразового интегриро вания. ;1|учший базош объект - интегра iTOt с п)воднэааией решешя (блок 1,БИ-31), входящий в состав серийно выпускаемые шшаратуры АВК-32, АЁЙК-33 не подвсмшет получить величину погр воста в режимах интегрирования с наКоплегасем инфс дации для разных ЯСЦепочек на уровне погрешностей в режиме одноразов и интегрирования.

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегратор | 1985 |

|

SU1298775A1 |

| Интегратор | 1986 |

|

SU1401485A2 |

| Устройство для квантования непрерывного сигнала по уровню | 1989 |

|

SU1674174A1 |

| Интегратор с управляемым ограничением выходного сигнала | 1986 |

|

SU1305724A1 |

| Времяимпульсный квадратичный преобразователь | 1986 |

|

SU1406610A1 |

| Устройство для моделирования упругого гистерезиса | 1980 |

|

SU966708A1 |

| Интегратор | 1988 |

|

SU1728871A1 |

| Аналоговый интегратор | 1979 |

|

SU855673A1 |

| Аналого-цифровой интегратор | 1981 |

|

SU1013978A1 |

| Интегратор | 1978 |

|

SU855674A1 |

ИНТЕГРАТОР, содержащий сперапионный усилитель, выход которого является, выходом интегратора и через интегрирующий конденсатор соещшен со входом операшюнного усилителя, первую группу ключей, первый вывод одного из KovGpmx. соединен с выходом, а вторсЛ Через масштабный резистор цепи ной связи со входом опербшионного усилителя, другие ключи первой группы соединены последовательно с маштабным резистором цепи задания начальных условий и входными масштабными резисторами, а управляющие входы ключей пер-, вой группы подключены к соотве1ствующ му управляющему входу интегратора, отличающийся тем, что, с : целью повышения точности интегрирования, в него введены вторая группа ключей, инверто{ 9и и шунтирующие резисторы, соединенные параллельно с соответствующим ключом второй группы и включенные между общими взыводами масштабных резисторов и ключей перьой и шиной яулоэого потенциала, управляющие входы ключей второй группы через ветст)гюаше инверторы соединены с соот : ветствуклцим управляющим входом интег- , erafaae выводы ключей, кроме первого КЛЮ1Ш, первой группы являются соответствующими информационными входами интегратора, а второй вывод маошта &{ого резистора цепи задания начальных условий и вторые вывсщы входных масштабных резисторов подключены ко ВХОДУ операционного усилителя. tC а

Авторы

Даты

1983-07-15—Публикация

1981-10-23—Подача