Изобретение относится к запоминающим устройствам и может быть использьовано вв двухпроцессорных и двухмашинных вычислительных системах в качестве общей оперативной памяти.

Цель изобретения - расширение области применения устройства за счет обеспечения одновременного считывания информации для двух потребителей при совпадении адресов обращения.

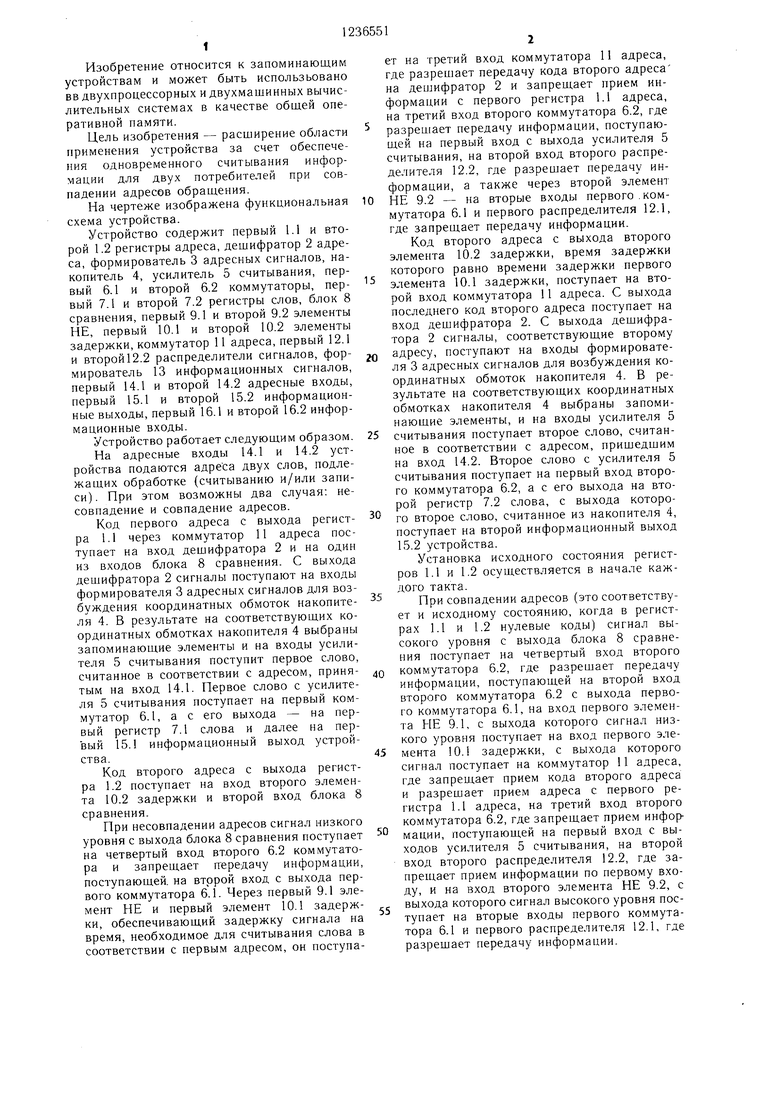

На чертеже изображена функциональная схема устройства.

Устройство содержит первый 1.1 и второй 1.2 регистры адреса, дешифратор 2 адреса, формирователь 3 адресных сигналов, накопитель 4, усилитель 5 считывания, первый 6.1 и второй 6.2 коммутаторы, первый 7.1 и второй 7.2 регистры слов, блок 8 сравнения, первый 9.1 и второй 9.2 элементы НЕ, первый 10.1 и второй 10.2 элементы задержки, коммутатор 11 адреса, первый 12.1 и второй12.2 распределители сигналов, формирователь 13 информационных сигналов, первый 14.1 и второй 14.2 адресные входы, первый 15.1 и второй 15.2 информационные , первый 16.1 и второй 16.2 информационные входы.

Устройство работает следующим образом.

На адресные входы 14.1 и 14.2 устройства подаются адре са двух слов, подлежащих обработке (считыванию и/или записи). При этом возможны два случая: несовпадение и совпадение адресов.

Код первого адреса с выхода регистра 1.1 через коммутатор 11 адреса поступает на вход дешифратора 2 и на один из входов блока 8 сравнения. С выхода дешифратора 2 сигналы поступают на входы формирователя 3 адресных сигналов для возбуждения координатных обмоток накопителя 4. В результате на соответствующих координатных обмотках накопителя 4 выбраны запоминающие элементы и на входы усилителя 5 считывания поступит первое слово, считанное в соответствии с адресом, принятым на вход 14.1. Первое слово с усилителя 5 считывания поступает на первый коммутатор 6.1, а с его выхода - на первый регистр 7.1 слова и далее на первый 15.1 информационный выход устройства.

Код второго адреса с выхода регистра 1.2 поступает на вход второго элемента 10.2 задержки и второй вход блока 8 сравнения.

При несовпадении адресов сигнал низкого уровня с выхода блока 8 сравнения поступает на четвертый вход второго 6.2 коммутатора и запрещает передачу информации, поступающей, на второй вход с выхода первого коммутатора 6.1. Через первый 9.1 элемент НЕ и первый элемент 10.1 задержки, обеспечивающий задержку сигнала на время, необходимое для считывания слова в соответствии с первым адресом, он поступает на третий вход коммутатора 11 адреса, где разрешает передачу кода второго адреса на деплифратор 2 и запрещает прием информации с первого регистра 1.1 адреса, на третий вход второго коммутатора 6.2, где

разрешает передачу информации, поступающей на первый вход с выхода усилителя 5 считывания, на второй вход второго распределителя 12.2, где разрещает передачу информации, а также через второй элемент

0 НЕ 9.2 - на вторые входы первого.коммутатора 6.1 и первого распределителя 12.1, где запрещает передачу информации.

Код второго адреса с выхода второго элемента 10.2 задержки, время задержки которого равно времени задержки первого

элемента 10.1 задержки, поступает на второй вход коммутатора 11 адреса. С выхода последнего код второго адреса поступает на вход дешифратора 2. С выхода дешифратора 2 сигналы, соответствующие второму

адресу, поступают на входы формирователя 3 адресных сигналов для возбуждения координатных обмоток накопителя 4. В результате на соответствующих координатных обмотках накопителя 4 выбраны запоминающие элементы, и на входы усилителя 5

5 считывания поступает второе слово, считанное в соответствии с адресом, прищедщим на вход 14.2. Второе слово с усилителя 5 считывания поступает на первый вход второго коммутатора 6.2, а с его выхода на второй регистр 7.2 слова, с выхода которо го второе слово, считанное из накопителя 4, поступает на второй информационный выход 15.2 устройства.

Установка исходного состояния регистров 1.1 и 1.2 осуществляется в начале каждого такта.

При совпадении адресов (это соответствует и исходному состоянию, когда в регистрах 1.1 и 1.2 нулевые коды) сигнал высокого уровня с выхода блока 8 сравнения поступает на четвертый вход второго

0 коммутатора 6.2, где разрешает передачу информации, поступающей на второй вход второго коммутатора 6.2 с выхода первого коммутатора 6.1, па вход первого элемента НЕ 9.1, с выхода которого сигнал низкого уровня поступает на вход первого эле5 мента 10.1 задержки, с выхода которого сигнал поступает на коммутатор 11 адреса, где запрец-1,ает прием кода второго адреса и разрещает прием адреса с первого регистра 1.1 адреса, на третий вход второго коммутатора 6.2, где запрещает прием инфор мации, поступающей на первый вход с выходов усилителя 5 считывания, на второй вход второго распределителя 12.2, где запрещает прием информации по первому входу, и на вход второго элемента НЕ 9.2, с

, выхода которого сигнал высокого уровня поступает на вторые входы первого коммутатора 6.1 и первого распределителя 12.1, где разрещает передачу информации.

Код первого адреса с выхода регистра 1.1 через коммутатор 11 адреса поступает на вход дешифратора 2, с выходов которого сигналы поступают на входы формирователя 3 адресных сигналов для возбуждения координатных обмоток накопителя 4. В результате на соответствующих обмотках накопителя 4 выбраны запоминающие элементы и на входы усилителя 5 считывания поступает слово, считанное в соответствии с адресом обращения. Слово с выходов усили- теля 5 считывания поступает на первый вход первого коммутатора 6.1, с выхода которого слово поступает на вход первого регистра 7.1 слова и на второй вход второго коммутатора 6.2, с выхода которого слово поступает на вход второго регистра 7.2 слова. С выходов первого 7.1 и второго 7.2 регистров слов информация поступает на первый 15.Ги второй 15.2 информационные выходы устройства соответственно.

Формула изобретения

Оперативное запоминающее устройство, содержащее накопитель, формирователь адресных сигналов, усилитель считывания, ком- мутаторы, регистры слов, формирователь информационных сигналов, распределители сигналов, дешифратор адреса, блок сравнения и регистры адреса, входы которых являются адресными входами устройства, выходы первого регистра адреса подключены к одним из входов блока сравнения, к другим входам которого подключены выходы второго регистра адреса, выходы дешифратора адреса подключены к входам формирователя адресных сигналов, выходы которого подключены к адресным входам накопителя, ин-

формационные выходы которого соединены с входами усилителя считывания, выходы которого подключены к первым входам коммутаторов, выходы которых соединены с одними входами регистров слов, другие входы и выходы которых являются соответственно информационными входами и выходами устройства, выходы первого и второго регистров слов подключены к одним входам распределителей сигналов, выходы которых соединены с входами формирователя информационных сигналов, выходы которого подключены к информационным входам накопителя, отличающееся тем, что, с целью расширения области применения устройства за счет одновременного считывания информации для двух потребителей при совпадении адресов обращения, о но содержит коммутатор адреса, элементы задержки, элементы НЕ, причем выход первого коммутатора соединен с вторым входом второго коммутатора, выход блока сравнения соединен с четвертым входом второго коммутатора и входом первого элемента НЕ, выход которого подключен к входу первого элемента задержки, выход которого соединен с третьим входом второго коммутатора, другим входом второго распределителя сигналов, входом второго элемента НЕ и третьим входом коммутатора адреса, второй и первый входы которого соединены соответственно с выходом второго элемента задержки и выходом первого регистра адреса, а выход коммутатора адреса соединен с входом дешифратора адреса, вход второго элемента задержки подключен к выходу второго регистра адреса, выход второго элемента НЕ соединен с вторым входом первого коммутатора и другим входом первого распределителя сигналов.

15.2

15.1

ir/T/

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство | 1980 |

|

SU938317A1 |

| Многоканальное оперативное запоминающее устройство | 1987 |

|

SU1432606A1 |

| Многоканальное запоминающее устройство | 1981 |

|

SU953669A1 |

| Оперативное запоминающее устройство | 1981 |

|

SU978192A1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ СИГНАЛОВ С ПРОГРАММНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 1997 |

|

RU2110890C1 |

| Многоканальное оперативное запоминающее устройство (его варианты) | 1982 |

|

SU1088067A1 |

| Запоминающее устройство с самоконтролем | 1979 |

|

SU847377A1 |

| Динамическое запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1133625A1 |

| Модуль программируемого коммутатора | 1986 |

|

SU1376094A1 |

| Оперативное запоминающее устройство | 1983 |

|

SU1095233A1 |

Изобретение относится к запоминающим устройствам и может быть использовано в двухпроцессорных и двухмашинных вычислительных системах в качестве общей оперативной памяти. Сущность изобретения заключается в расширении области применения устройства. Устройство содержит накопитель, формирователи сигналов, усилители считывания, коммутаторы, регистры слов, распределители сигналов, регистры адреса, блок сравнения, дешифратор адреса, коммутатор адреса, элементы задержки и элементы НЕ. Введение в известное устройство новых элементов, а именно коммутатора адреса, элементов НЕ и элементов задержки, позволяет обеспечить одновременное считывание информации для двух потребителей при совпадении адресов обращения. I ил. ьо со ot ел СП

| Магнитное оперативное запоминающее устройство | 1976 |

|

SU647742A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Оперативное запоминающее устройство | 1980 |

|

SU938317A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Электронные цифровые вычислительные машины | |||

| Под ред | |||

| К | |||

| Г | |||

| Самофалова, Ки- ев: Вища школа, 1976, с | |||

| СПОСОБ ПОЛУЧЕНИЯ ХЛОРИСТОГО БАРИЯ ИЗ ТЯЖЕЛОГО ШПАТА | 1923 |

|

SU480A1 |

Авторы

Даты

1986-06-07—Публикация

1984-09-12—Подача