Изобретение относится к запоминающим устройствам и может быть использовано в двухпроцессорных вычис лительных системах (комплексах) в качестве общей оперативной памяти. Известно многоканальное запомина ющее устройство, в котором применяется рациональное размещение чисел в модулях памяти в виде элементов матрицы со сдвигом, обеспечивающее при регулярных обращениях к памяти в рамках одной задачи одновременное обращение в пределах одного и того столбца или строки матрицы, причем модули памяти имеют встроенные элвм ты индексации для выполнения сдвига til. Недостатком этого устройства явл ется его сложность. Наиболее близким к предлагаемому техническим решением является много канальное запоминающее устройство, содержащее регистры адресов, подключенные к координатным дешифраторам, координатные формирователи , подключенные к соответствующим -координатным шинам накопителя, причем шины считывания накопителя через .блок усилителей воспроизведения подключены к первым входам блоков коммутаторов усилителей воспроизведения, выходы которых через регистры слова связаны с выходными шинами устройства и с первыми входами первичных узлов выборки разрядных формирователей , выходы которых подключены к разрядным шинам накопителя через последовательно-соединенные блок выбора разрядных формирователей и блок разрядных формирователей, выходы регистров адресов через блок выбора усилителей воспроизведения подключены к вторым входам первых первичных узлов выбора разрядных формирователей и к вторым входам первого блока коммута-i торов усилителей воспроизведения, дополнительные регистры адресов, дополнительные координатные дешифраторы адресов, дополнительный блок выбора усилителей воспроизведения, дополнительный выход устройства, два блока схем ИЛИ, три бг.ока схем И, две схемы совпадения, схему И-НЕ и три схемы НЕ 2 .

Недостатком этого устройства является то, что приоритеты его каналов жестко определены и в нем не обеспечивается возможность изменения приоритетов своих каналов, за счет чего ограничивается область применения устройства.

Целью изобретения является расширение области применения устройства за счет обеспечения возможности управления, приоритетом его каналов.

Поставленная цель достигается тем , что в многоканальное запоминающее устройство, содержащее накопитель, формирователи адресных сигналов, формирователи разрядных сигналов, усилители воспроизведения, коммутаторы, регистры слова, схему сравнения, преобразователи кодов адреса, регистры адреса, дешифраторы адреса, элементы И, элементы ИДИ и первый элемент НЕ, причем входы первого и второго регистров адреса являются адресными входами первого канала устройства , а выходы соединены q входами первого преобразователя кодов адреса , выходы которого подключены к одним из входов схемы сравнения, входы третьего и четвертого регистров адреса являются адресными входами второго канала устройства, а выходы соединены с входами второго преобразователя кодов адреса, выходы которого подключены к одним из входов первого элемента И и другим входам схемы сравнения, выход которой соединен с входом первого элемента НЕ, выходы первого и второго дешифраторов адреса подключены соответственно к одним из входов первого и второго элементов ИЛИ, выходы которых соединены соответственно с входами первого и второго формирователей адресных сигналов выходы которых соединены с адресными входами накопителя, другие входы первого и второго элементов ИЛИ подключены соответственно к выходам третьего и четвертого дешифраторов адреса, входы которых соединены с выходами второго и третьего элементов И соответственно, одни из входов которых подключены соответственно к выходам

Третьего и четвертого регистров адреса, входы усилителей считывания соединены с выходами накопителя,а выходы - с одними из входов первого и второго коммутаторов, выходы которых подключены соответственно к одним из входов первого и второго регистров слова, выходы которых соединены соответственно с одними из

0 входов третьего и четвертого коммутаторов, выходы которых подключены через пятый коммутатор к входам формирователей разрядных сигналов, выходы которых соединены с разрядными

5 входами накопителя, выход первого элемента И подключен к другим входам второго и четвертого коммутаторов, выходы схемы сравнения, выходы и другие входы первого и второго регистров слова являются соответственно индикаторным выходом устройства, информационными выходами и входами первого и второго каналов устройства, введены четвертый, пятый и шестой элементы И, третий и четвертый элементы ИЛИ и второй элемент НЕ, причем одни из входов четвертого, пятого и шестого элементов ;И подключены соответственно к выходам первого и второго регистров адреса и к выходам первого преобразователя кодов адреса, выходы четвертого, пятого и шестого элементов И соединены соответственно с входами первого и второго дешифраторов-адреса и с другими входами первого и третьего коммутаторов, другие входы четвертого, пятого и шестого элементов И подключены к выходу третьего элемента ИЛИ, первый вход которого соединен с выходом второго : элемейта НЕ, вход.которого подключен к первому входу четвертого элемента ИЛИ, выход которого соединен с другими входами первого, второго и третьего элементов И, вторые входы третьего и четвертого элементов ИЛИ подключены к выходу первого элемента НЕ, вход второго элемента НЕ является управляющим входом устройства.

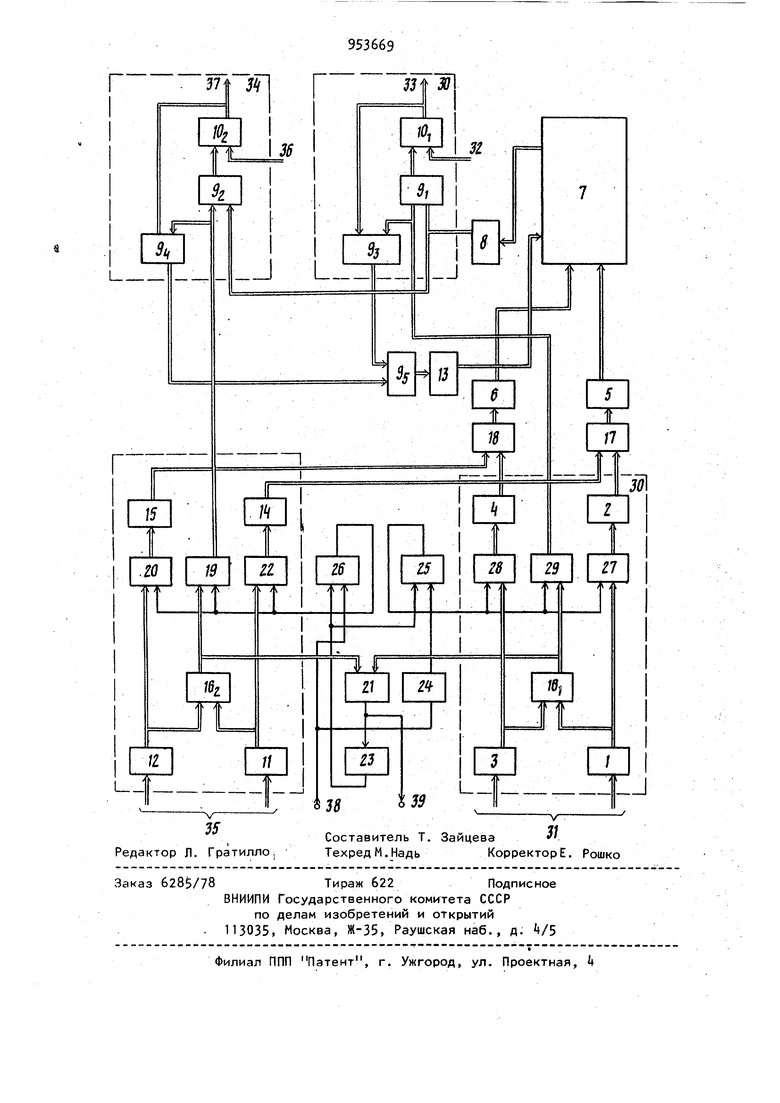

На чертеже представлена структурная схема предложенного устройства.

Устройство содержит первый регистр I адреса, первый дешифратор 2 адреса, второй регистр 3 адреса, второй дешифратор {адреса, первый 5 и второй 6 формирователи адресных сигналов , накопитель 7 усилители 8 считывания, первый 9-1, второй 95,третий 9т четвертый 94 и пятый Э ком мутаторы, первый 10 и второй 10/2. регистры слова, третий 11 и четвер тый 12 регистры адреса, формировате ли -13 разрядных сигналов, третий И и четвертый .15 дешифраторы адрес первый 16 и второй 16 преобразователи кодов адреса, первый 17 и второй 18 элементы ИЛИ, первый. 19 и второй 20 элементы И, схему 21 сравнения, третий элемент И 22, пер вый 23 и второй 2k элементы НЕ, тре тий 25 и четвертый 26 элементы ИЛИ, четвертый 27, пятый 28 и шестой 29 элементы И. На чертеже обозначены первый 30 устройства с адресными 31 и информационными 32 вхо дами, и информационными входами 33 устройства, второй канал 3.устройства с адресными 35 и информационны ми 36 входами, и информационными 37 выходами устройства, управляющий вход 38 и индикаторный выход 39 устройства Каждый из преобразователей 16 и iGij содержит сумматор по модулю два и дешифратор (не показаны). Устройство работает следующим об разом. . Код адреса первого слова посту пает от первого устройства-потребителя на входы 31 первого 30 канала. Одновременно на входы 35 второго 3 канала может быть подан код адреса второго слова. При этом наибольший интерес представляет, во-первых, несовпадение кодов адресов обоих слов и несовпадение кодов на выходах обоих преобразователей 16 и 6ii , во-вторых, совпадение кодов адресов обоих слов или совпадение кодов на выходах обоих преобразователей 16,, и 16 при несовпадении кодов адресов обоих слов. При совпадении обоих кодов адресов , поступающих на входы 31 и 35, на выходах преобразователей 16- и 16г2 коды совпадают. Каждый из преобразователей 6х| и 167 обеспечивает суммирование без учета конечного переноса двоичных кодов, поступающих на его входы, и преобразует двоичный код полученной суммы в пози ционный код. Поэтому, если коды, пос тупающие на входы 31 и 35, совпадают, например, если подан один и тот же код 01101110, где первая «половина кода (0110) подается на регистры 3 и 12, а вторая половина (1110)на регистры 1 и 11, то на выходах обоих преобразователей 16. и I6i2 будет один и тот же код, определяемый суммой 0110+1110 0100 без учета конечного переноса. Кроме того, следует отметить, что для некоторых кодов, например, для кодов 0110 1110 и 1110 0110, характеризующихся перестановкой первой и второй половин кодов, на выходах преобразователей 1б и 16 «2 будут совпадать коды, так как и в этом случае сумма кодов без учета конечного переноса (0110+1110 0100,.П10+0110 0100) будет одна и та же. Из этого следует, что равенство кодов на выходах преобразователей 16 и 16 (2 является более общим требованием , чем равенство кодов, поступающих на адресные входы 31 и 35 устройства. При несовпадении кодов на выходах обоих преобразователей 1б и , следовательно, при несЬвпадении кодов адресов, поступающих на входы 31 и 35 устройства , пёрвьГе 30 и вторые 3 каналы устройства полнестью независимы и позволяют обеспечить запись и (или) считывание одновременно двух слов следущим образом. Поскольку указанные коды не совпадают, то на выходе схемы 21 сравнения будет низкий уровень напряжения, который, пройдя через элемент НЕ 23, превратится в высокий уровень напряжения и через вторые входы элементов ИЛИ 25 и 2б поступит на вторые входы элементов И 19, 20, 22, 27, 28 и 29 в качестве разрешающего сигнала . . Код адреса первого слова, поступивший на входы 31 первого канала 30, поступит на дешифраторы 2 и j. Сигналы с выходов дешифраторов 2 и k через первые входы элементов ИЛИ 17 и 18 пройдут на входы формирователей 5 и 6 для возбуждения соответствующих координатных шин накопителя 7В результате будет записано слово в соответствии с кодом адреса, поступившим на входы 31 устройства. Пер вое считанное слово через усилители 8 поступит на первые входы коммутаторов 9-, и 9(j; с помощью выходных сигналов преобразователя 16 , определяемых кодом адреса первого считанного слова, прошедших через элемент. И 29 и поступивших на вторые входы коммутаторов .9-1, считанное 7, 9 первое слово будет передано в регистр 10 первого канала 30. Код адреса второго слова, поступивший от второго устройства-потребителя на входы 35 второго канала З, будет передан на дешифраторы И и 15 через элементы И 22 и 20, Сигналы с выходо дешифраторов 1 и 15 через вторые входы элементов ИЛИ 17 и 18 пройдут на входы формирователей 5 и 6 для возбуждения требуемых координатных шин накопителя 7. В результате из накопителя 7 будет считано второе слово в соответствии с кодом адреса поступившим на входы устройства, Усиленное второе считанное слово поступит на первые входы коммутаторов Эх, и 3(1- С помощью выходных сигналов преобразователя 1бп , определяемых кодом адреса второго считанного слова, прошедших через Ълемент И 19 на вторые входы коммутатора Эг считанное второе слово будет передано в регистр 10f2 второго канала 3 Регенерация считанной информации и (или) запись новой информации, поступающей на входы 32 и Зб устройства, происходит обычным образом. При совпадении кодов адресов обоих слов или при совпадении сумм поло вин несовпадающих кодов, и, кай следствие ,при совпадении кодов на выходах преобразователей 1бх, и 6q обеспечивается приоритетное обслуживание устройств-потребителей. При этом приоритетность обслуживания задается уровнем управляющего сигнала, поступающего извне на вход 38 устройства. При низком уровне управля-. ющего сигнала на входе 38 приоритет отдается первому устройству-потре- бителю; подключаемому к первому каналу 30 устройства. При высокбм уров не управляющего сигнала на входе 38 приоритет отдается второму устройству-потребителю, подключаемому к второму каналу З устройства. Если отдан приоритет какому-то, вполне определенному устройству-потребителю, то это означает, что данное устройство-потребитель может производить любые операции по обработке информации : считывать и (или) записывать информацию по заданному адресу накопит.еля 7, в то время как другое устройство-потребитель вообще не обслуживается. При: этом на выходе 39 устройства появится высокий уровень напряжения, сигнализи.8 рующий о произошедшем совпадении адресных кодов или сумм их половин, а работа устройства происходит следующим образом. Поскольку коды адреса совпадают или совпадают суммы их половин кодов, то на выходах преобразователей 16 и 1бг1 коды тоже совпадают. Эти коды, поступившие на входы схемы 21 сравнения, приведут к появлению на ее выходе сигнала высокого уровня. Этот сигнал, поступив на выход 39 устройства, будет сигнализировать о произошедшем совпадении указанных кодов .и поступит на вторые входы элементов ИЛИ 25 и 2б в качестве запрещающего уровня для элементов И 19, 20, 22, 27, 28 и 29. В зависимости от приоритета, т,е, от уровня управляющего сигнала, на входе 38 через элементы ИЛИ 25 или 2б будет передан только один сигнал высокого уровня, в результате будет работать либо первый 30, либо второй 3 каналы устройства. Если на входе 38 присутствует сигнал низкого уровня, то на обоих входах элемента ИЛИ 2б и на его выходе будут сигналы низкого уровня, поэтому элементы И 19, 20 и 22 во втором канале З устройства будут заблокированы, и канал З не будет реагиро-. вать на код адреса, поступившего на входы 35. В противопожность этому сигнал низкого уровня со входа 38 будет действовать через элемент НЕ 2k и элемент ИЛИ 25 на элементы И 27-29 в качестве разрешающего сигнала. В результате будет обслуживаться только устройство-потребитель, подключаемое к первому каналу 30 устройства. При наличии высокого уровня на входе 38 на входах элемента ИЛИ 25 и, следовательно, на его выходе будут сигналы низкого уровня, поэтому первый канал 30 будет заблокирован, В отличие от этого высокий уровень с входа 38 пройдет через элемент ИЛИ 2б в качестве разрешающего сигнала для элементов И 19, 20 и 22 во втором канале З, в результате будет обслуживаться только второе устройство-потребитель, подключаемое к второму каналу 3 устройства. Технико-экономическое преимущество предложенного устройства заключается в том, что оно обеспечивает режим оперативного изменения приоритетов работы, каналов-устройства, тем самым позволяет изменять

приоритет обслуживания потребителей (процессоров ЭВМ), что расширяет область применения запоминающего устройства.

Формула изобретения Многоканальное запоминающее устройство, содержащее накопитель, формирователи адресных сигналов, формирователи разрядных сигналов, усилители воспроизведения, коммутаторы, регистры слова-, схему сравнения, преобразователи кодов адреса, регистры адреса, дешифраторы адреса, элементы И, элементы ИЛИ и первый элемент НЕ , причем входы первого и второго регистров адреса являются адресными входами первого канала устройства, а выходы соединены, с вхо дами первого преобразователя кодов адреса, выходы которого подключены к одним из входов схемы сравнения, входы третьего и четвертого регистров адреса являют ся адресными входами второго канала устройства, а выходы соединены с входами второго преобразователя кодов адреса, выходы KOTOporq подключены к одним из входов первого элемента И и другим входам схемы сравнения, выход которой соединен с входом первого элемента НЕ, выходы первого и второго дешифраторов адреса подключены соответственно к одним из входов первого и второго элементов ИЛИ, выходы которых соединены соответственно с входами первого и второго формирователей адресных сигналов, выходы которых соединены с адресными входами накопителя, другие входы первого и второго элементов ИЛИ подключены соответственно к выходам третьего и четвертого дешифраторов адреса, входы которых соединены с выходами второго и третьего элементов И соответственно, одни из входов которых подключены соответственно к выходам третьего и четвертого регистров адреса, входы усилителей считывания соединены с выходами накопителя, а выходы - с одними из входов первого и второго коммутаторов, выходы которых подключены соответственно к одним из входов первого и второго регистров слова, выходы которых соединены соответственно с одними из входов третьего и четвертого Коммутаторов , выходы которых подключены через пятый коммутатор к входам формирователей разрядных сигналов, выходы .-которых соединень с разрядными входами накопителя, выход первого И подключен к другим входам второго и четвертого коммутаторов, выход схемы сравнения, выходы и другие входы первого и второго регистров слова являются соответственно индикаторным выходом устройства, информационными выходами и входами первого и второго каналов устройства, отличающееся тем, что, с целью расширения области применения устройства за счет обеспечения возможности управления приоритетом каналов .устройства, оно содержит четвер|ТЫй, пятый и шестой элементы И, третий и четвертый элементы ИЛИ и второй элемент НЕ, причем одни из входов четвертого, пятого и шестого элементов И подключены соответственно к выходам первого и второго-f eгиcтров адреса и к выходам первого преобразователя кодов адреса, выходы четвертого, пятого и шестого элементов И соединены соответственно с вхо дами первого и второго дешифраторов адреса и с другими входами первого и третьего коммутаторов, другие входы четвертого, пятого и шестого элементов И подключены к выходу третьего элемента ИЛИ, первый вход которого соединен с выходом второго элемента НЕ, вход которого подключен к первому входу четвертого элемента ИЛИ, выход KOTopotyo соединен с другими входами первого, второго и третьего элементов И, вторые входы третьего и четвертого элементов ИЛИ подключены к выходу первого элемента НЕ, вход второго элемента НЕ является управляющим входом устройства.

Источники информации, принятые во внимание при экспертизе

1. Прангишвили И.В., Стецюра Г.Г, Микропроцессорные системы. М., Науk3 kk.

ка

с.

2. Авторское свидетельство СССР по заявке I 2987190/18-2+, кл. G И С 11/06 (прототип).

55

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство | 1980 |

|

SU938317A1 |

| Запоминающее устройство | 1975 |

|

SU639016A1 |

| Магнитное оперативное запоминающее устройство | 1981 |

|

SU980161A1 |

| Многоканальное оперативное запоминающее устройство (его варианты) | 1982 |

|

SU1088067A1 |

| Оперативное запоминающее устройство | 1981 |

|

SU978192A1 |

| Многоканальное оперативное запоминающее устройство | 1987 |

|

SU1432606A1 |

| Устройство для обучения | 1987 |

|

SU1559366A1 |

| Оперативное запоминающее устройство | 1984 |

|

SU1236551A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Запоминающее устройство с резервированием | 1987 |

|

SU1411824A1 |

Авторы

Даты

1982-08-23—Публикация

1981-03-02—Подача