; Изобретение относится к импульсной тех- нике и может быть использовано при создании ИС согласования уровней.

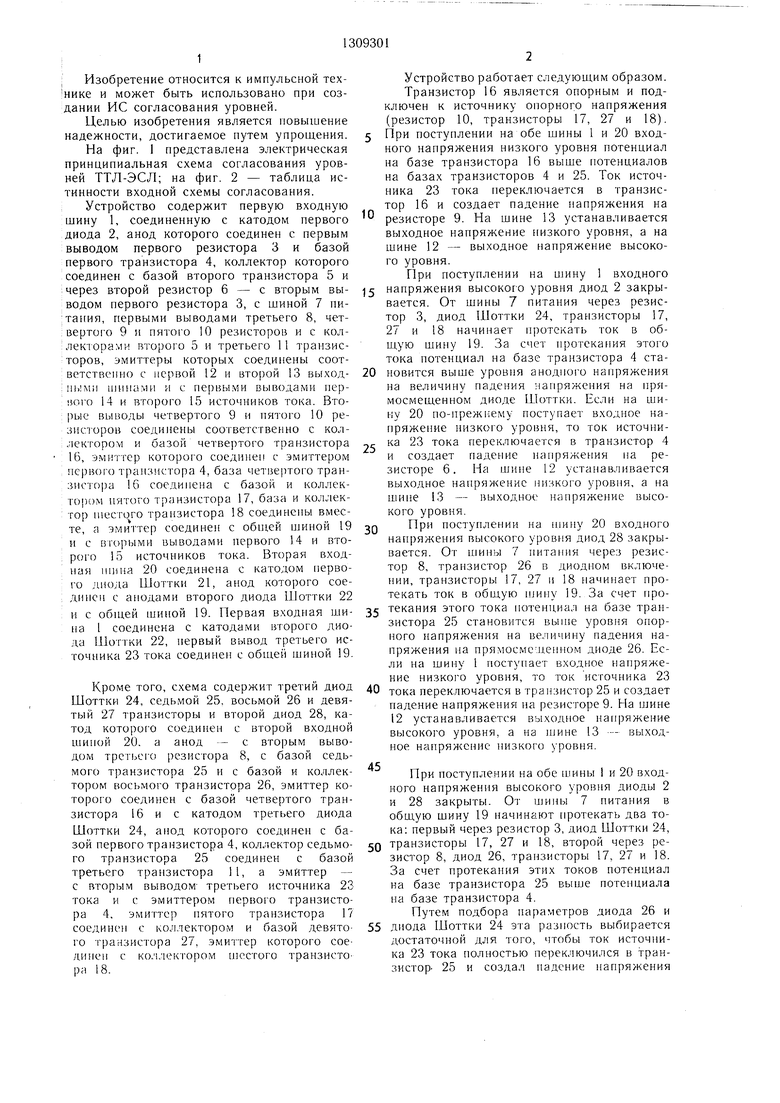

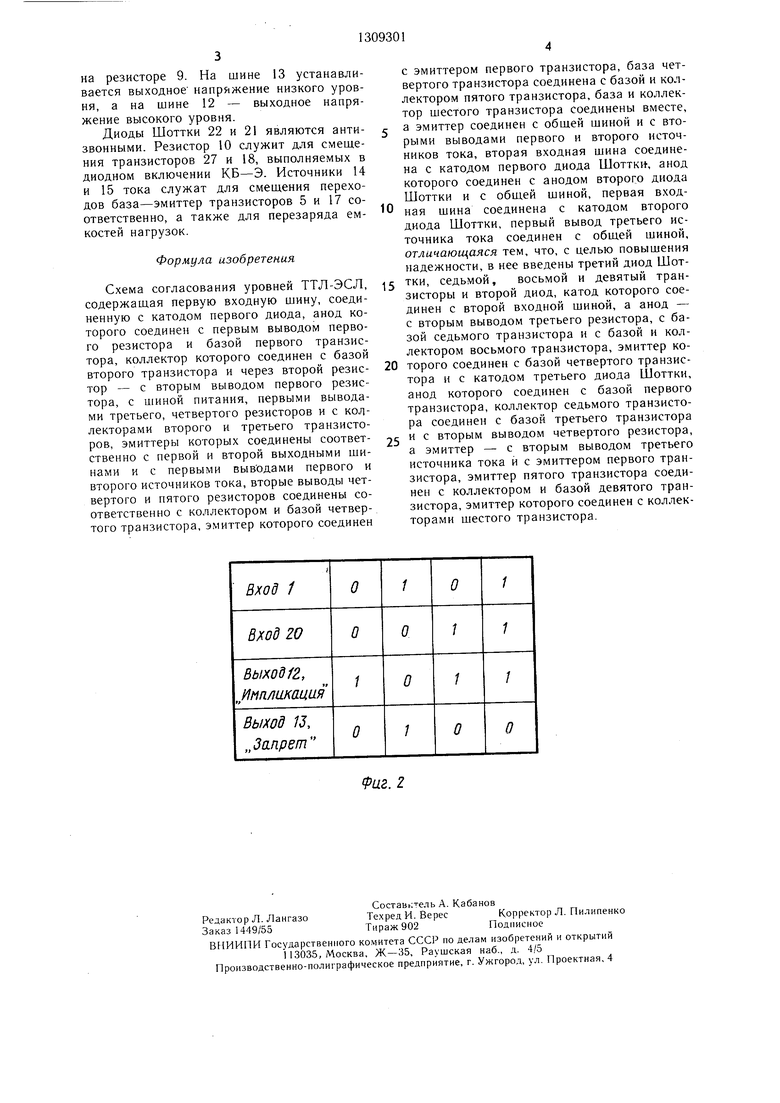

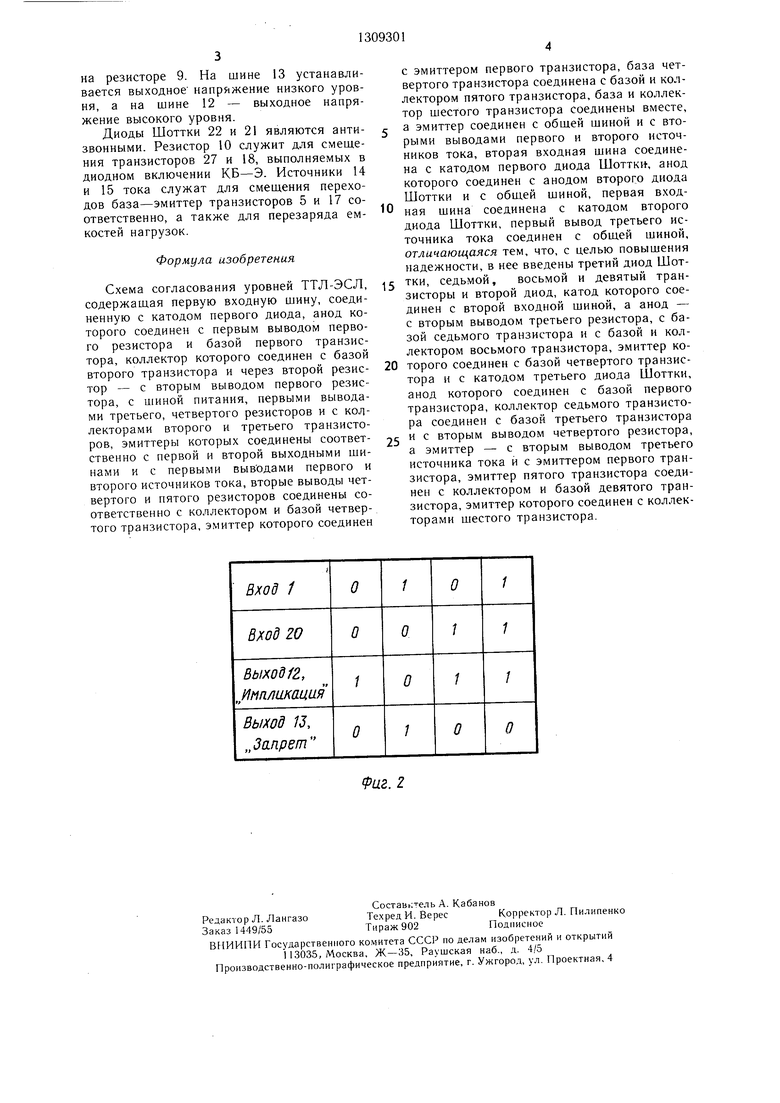

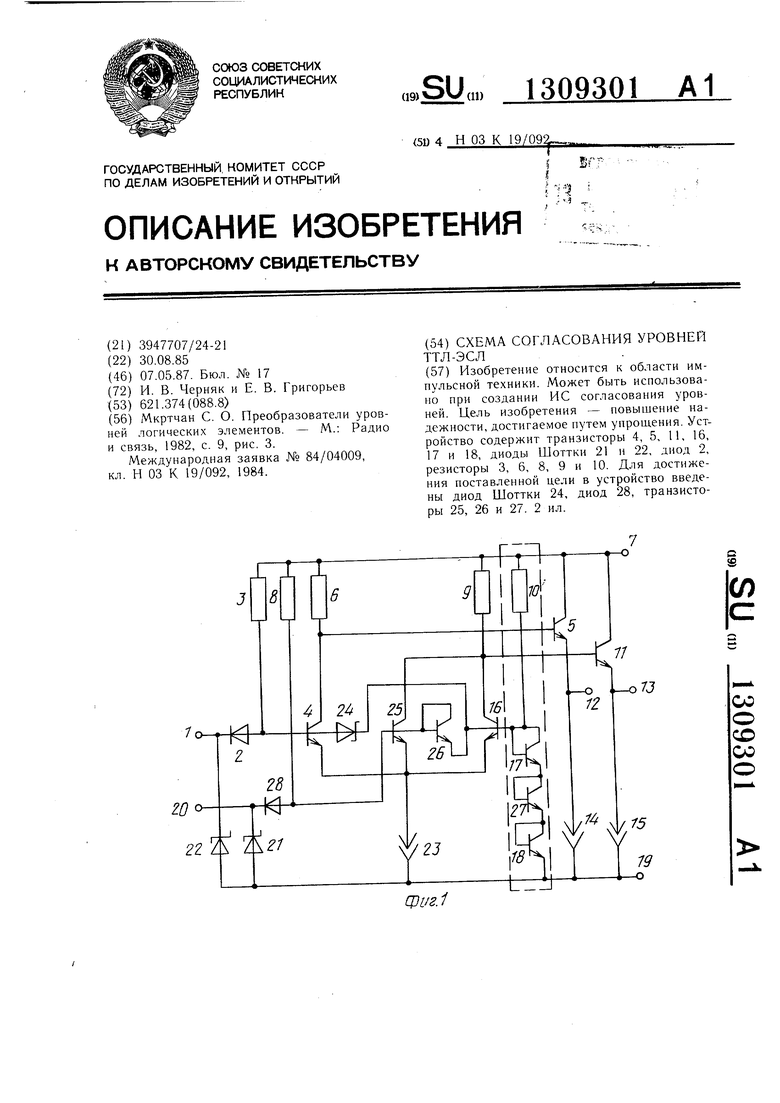

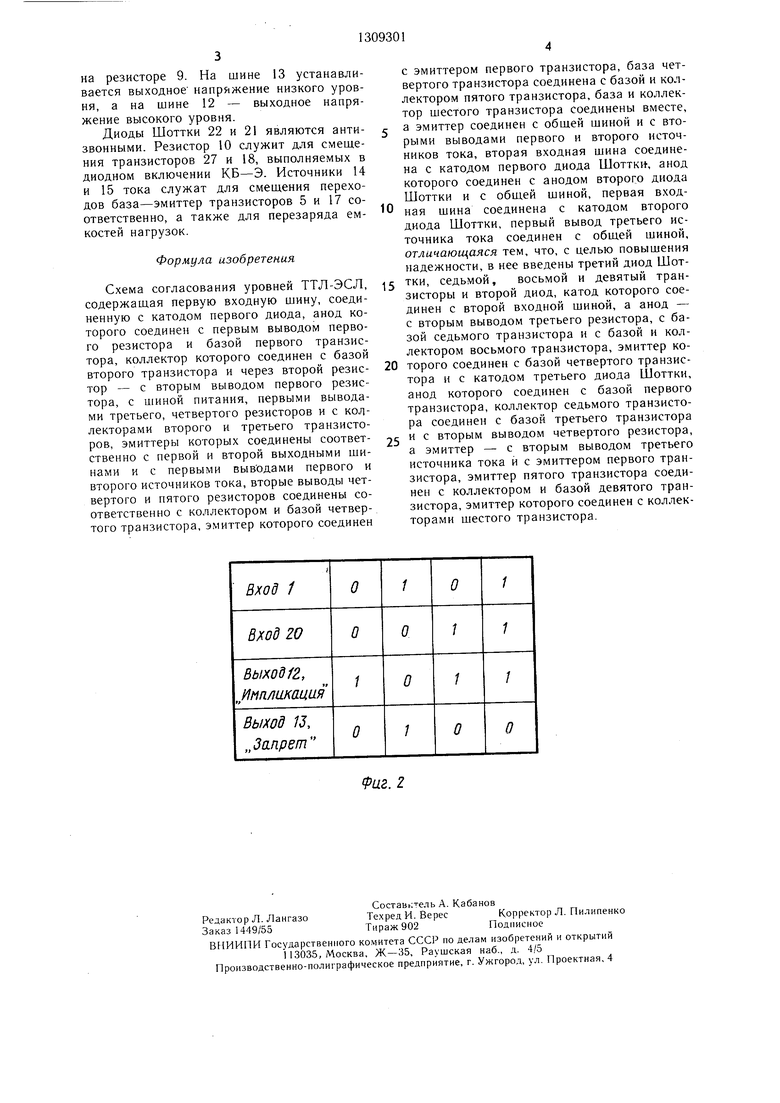

Целью изобретения является повышение надежности, достигаемое путем упрощения. На фиг. 1 представлена электрическая принципиальная схема согласования уровней ТТЛ-ЭСЛ; на фиг. 2 - таблица истинности входной схемы согласования.

Устройство содержит первую входную шину 1, соединенную с катодом первого диода 2, анод которого соединен с первым выводом первого резистора 3 и базой первого транзистора 4, коллектор которого соединен с базой второго транзистора 5 и через второй резистор 6 - с вторым выводом первого резистора 3, с шиной 7 питания, первыми выводами третьего 8, четвертого 9 и пято1 о 10 резисторов и с кол- :лекторами второго 5 и третьего 11 транзисторов, эмиттеры которых соединены соответственно с первой 12 и второй 13 выход- - шинами и с пе)вы.ми выводами пер- )огс) 14 и второго 15 источников тока. Вторые выводы четвертого 9 и пятого 10 резисторов соединены соответственно с кол- .лектором и базой четвертого транзистора 16, эмиттер которого соединен с эмиттером iicpBOix) транзистора 4, база четвертого транзистора 16 соединена с базой и коллектором пятого транзистора 17, база и коллектор шестого транзистора 18 соединены вместе, а эмиЧтер соединен с обшей шиной 19 и с вторыми выводами первого 14 и второго 15 источников тока. Вторая входная шина 20 соединена с катодом первого диода Шоттки 21, анод которого соединен с анодами второго диода Шоттки 22 и с обшей шиной 19. Первая входная шина I соединена с катодами второго диода Шоттки 22, иервый вывод третьего источника 23 тока соединен с общей шиной 19.

Кроме того, схема содержит третий диод Шоттки 24, седьмой 25. восьмой 26 и девятый 27 транзисторы и второй диод 28, катод которого соединен с второй входной шиной 20. а анод - с вторым выводом третье1 0 резистора 8, с базой седьмого транзистора 25 и с базой и коллектором восьмого транзистора 26, эмиттер которого соединен с базой четвертого транзистора 16 и с катодом третьего диода Шоттки 24, анод которого соединен с базой первого транзистора 4, коллектор седьмого транзистора 25 соединен с базой третьего транзистора И, а эмиттер - с вторым выводом- третьего источника 23 тока и с эмиттером первого транзистора 4, эмиттер пятого транзистора 17 соединен с коллектором и базой девятого транзистора 27, эмиттер которого соединен с коллектором нюстого транзистора 18.

Устройство работает следующим образом. Транзистор 16 является опорным и подключен к источнику опорного напряжения (резистор 10, транзисторы 17, 27 и 18).

При поступлении на обе шины 1 и 20 входного напряжения низкого уровня потенциал на базе транзистора 16 выше потенциалов на базах транзисторов 4 и 25. Ток источника 23 тока переключается в транзистор 16 и создает падение напряжения на

резисторе 9. На шине 13 устанавливается выходное напряжение пизкого уровня, а на шине 12 - выходное нанряжение высокого уровня.

При поступлении на шину 1 входного

напряжения высокого уровня диод 2 закрывается. От шины 7 питания через резистор 3, диод Шоттки 24, транзисторы 17, 27 и 18 начинает протекать ток в общую шину 19. За счет протекания этого тока нотенциал на базе транзистора 4 становится выше уровня анодного напряжения на величину падения напряжения на пря- мосмещениом диоде Шоттки. Если на шину 20 но-преж1-:ему поступает входное напряжение низкого уровня, то ток источника 23 тока переключается в транзистор 4 и создает падение напряжения на резисторе 6. На шине 12 устанавливается выходное напряжение низкого уровня, а на шине 13 - выходное напряжение высокого уровня.

При поступлении на шину 20 входного напряжения высокого уровня диод 28 закрывается. От шины 7 питания через резистор 8, транзистор 26 в диодном включении, транзисторы 17, 27 и 18 начинает протекать ток в общую HJHHy 19. За счет иротекания этого тока потенциал на базе транзистора 25 становится вьпие уровня опорного напряжения на величину падения напряжения на прямосме-цениом диоде 26. Если на шину 1 поступает входное напряжение низкого уровня, то ток источника 23

тока переключается в транзистор 25 и создает падение напряжения на резисторе 9. На UJИнe 12 устанавливается выходное напряжение высокого уровня, а на in и не 13 - выходное напряжение низкого уровня.

При поступлении на обе шины 1 и 20 входного напряжения высокого уровня диоды 2 и 28 закрыты. От шины 7 питания в общую шину 19 начинают протекать два тока: первый через резистор 3, диод Шоттки 24,

транзисторы 17, 27 и 18, второй через резистор 8, диод 26, транзисторы 17, 27 и 18. За счет протекания этих токов потенциал на базе транзистора 25 выше потенциала на базе транзистора 4.

Путем подбора параметров диода 26 и

диода Шоттки 24 эта разность выбирается достаточной для того, чтобы ток источника 23 тока полностью переключился в транзистор- 25 и создал падение напряжения

на резисторе 9. На шине 13 устанавливается выходное напряжение низкого уровня, а на шине 12 - выходное напряжение высокого уровня.

Диоды Шоттки 22 и 21 являются анти- звонными. Резистор 10 служит для смещения транзисторов 27 и 18, выполняемых в диодном включении КБ-Э. Источники 14 и 15 тока служат для смещения переходов база-эмиттер транзисторов 5 и 17 соответственно, а также для перезаряда емкостей нагрузок.

Формула изобретения

Схема согласования уровней ТТЛ-ЭСЛ, содержащая первую входную щину, соединенную с катодом первого диода, анод которого соединен с первым выводом первого резистора и базой первого транзистора, коллектор которого соединен с базой второго транзистора и через второй резистор - с вторым выводом первого резистора, с шиной питания, первыми выводами третьего, четвертого резисторов и с коллекторами второго и третьего транзисторов, эмиттеры которых соединены соответственно с первой и второй выходными щи- нами и с первыми выв одами первого и второго источников тока, вторые выводы четвертого и пятого резисторов соединены соответственно с коллектором и базой четвертого транзистора, эмиттер которого соединен

0

5

с эмиттером первого транзистора, база четвертого транзистора соединена с базой и коллектором пятого транзистора, база и коллектор щестого транзистора соединены вместе, а эмиттер соединен с общей щиной и с вторыми выводами первого и второго источников тока, вторая входная щина соединена с катодом первого диода Шоттки, анод которого соединен с анодом второго диода Шоттки и с общей щиной, первая входная шина соединена с катодом второго диода Шоттки, первый вывод третьего источника тока соединен с общей шиной, отличающаяся тем, что, с целью повышения надежности, в нее введены третий диод Шоттки, седьмой, восьмой и девятый транзисторы и второй диод, катод которого соединен с второй входной щиной, а анод - с вторым выводом третьего резистора, с базой седьмого транзистора и с базой и коллектором восьмого транзистора, эмиттер ко- 0 торого соединен с базой четвертого транзистора и с катодом третьего диода Шоттки, анод которого соединен с базой первого транзистора, коллектор седьмого транзистора соединен с базой третьего транзистора и с вторым выводом четвертого резистора, а эмиттер - с вторым выводом третьего источника тока и с эмиттером первого транзистора, эмиттер пятого транзистора соединен с коллектором и базой девятого транзистора, эмиттер которого соединен с коллекторами шестого транзистора.

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Двойной инвертор с минимальной асимметрией | 1987 |

|

SU1499484A1 |

| Интегральная логическая схема (ее варианты) | 1984 |

|

SU1228260A1 |

| Инверторная схема с минимальной асимметрией | 1985 |

|

SU1311016A1 |

| Транзисторный логический элемент | 1988 |

|

SU1621165A1 |

| Маломощный транзисторный логический элемент | 1988 |

|

SU1598157A1 |

| Элемент транзисторно-транзисторной ложки (его варианты) | 1985 |

|

SU1274149A1 |

| Двойной инвертор с минимальной асимметрией | 1984 |

|

SU1499483A1 |

| ТТЛ-инвертор | 1984 |

|

SU1269252A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ «ИСКЛЮЧАЮЩЕЕ ИЛИ» | 2022 |

|

RU2795286C1 |

| Устройство управления записью-считыванием информации для полупроводникового запоминающего устройства | 1986 |

|

SU1367040A1 |

Изобретение относится к области импульсной техники. Может быть использовано при создании ИС согласования уровней. Цель изобретения - повышение надежности, достигаемое путем упрощения. Устройство содержит транзисторы 4, 5, 11, 16, 17 и 18, диоды Шоттки 21 и 22, диод 2, резисторы 3, 6, 8, 9 и 10. Для достижения поставленной цели в устройство введены диод Шоттки 24, диод 28, транзисторы 25, 26 и 27. 2 ил. ZO оо о СО со о Фие. 1

| Мкртчан С | |||

| О | |||

| Преобразователи уровней логических элементов | |||

| - М.: Радио и связь, 1982, с | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Способ приготовления сернистого красителя защитного цвета | 1921 |

|

SU84A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-05-07—Публикация

1985-08-30—Подача