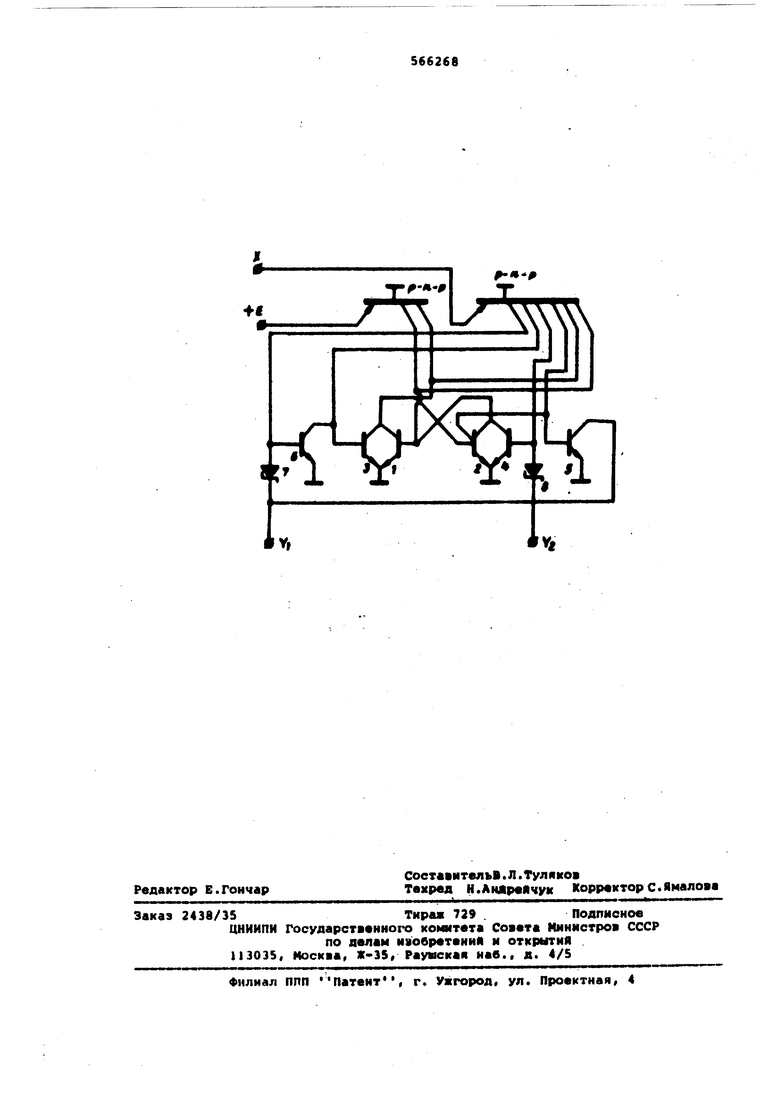

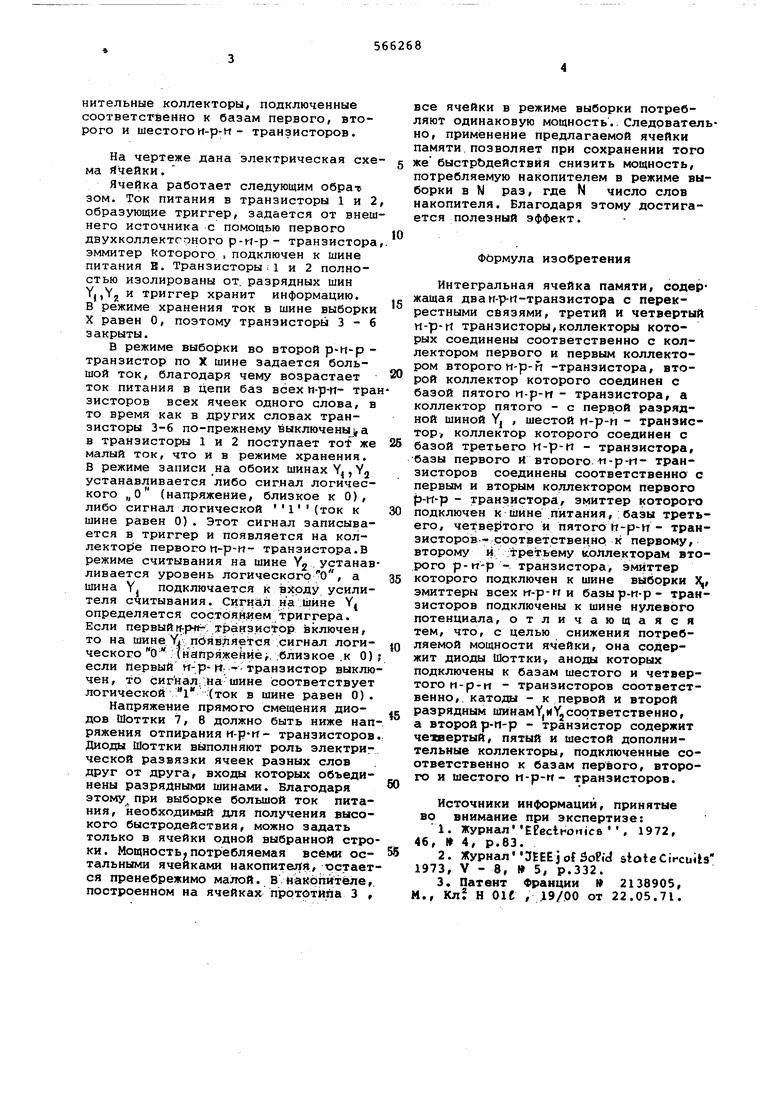

(54) ИНТЕРРАЛЬНАЯ ЯЧЕЙКА ПАМЯТИ нительные коллекторы, подключенные соответственно к базам первого, второго и шестогои-р-н - транзисторов. На чертеже дана электрическая схема Ячейки. Ячейка работает следующим обрат зоМ. Ток питания в транзисторы 1 и 2 образующие триггер, задается от внешнего источника с помощью первого двухколлектсоного р-и-р- транзистора эммитер Которого подключен к шине питания В. Транзисторыi1 и 2 полностью изолированы от, разрядных шин Y, jYg и триггер хранит информацию. В режиме хранения ток в шине выборки X равен О, поэтому транзисторы 3-6 закрыты. В режиме выборки во второй р-и-р транзистор по X шине задается большой ток, благодаря чему возрастает ток питания в цепи баз всех н-р-п- тра зисторов всех ячеек одного слова, в то время как в других словах транзисторы 3-6 по-прежнему выключеныj, а в транзисторы 1 и 2 поступает тот же малый ток, что и в режиме хранения. В режиме записи на обоих шинах Y,Y2 устанавливается либо сигнал логического „о (напряжение, близкое к 0), либо сигнал логической Ч{ток к шине равен 0). Этот сигнал записывается в триггер и появляется на коллекторё первого п-р-н- транзистора.В режиме считывания на шине Yg устанав ливается уровень логическогс о , а шина YJ подключается к В1срду усилителя считывания. Сигнал на шине Y определяется состоянием триггера. Если первый транзистор включен, то на шине Yi появляется сигнал логического 6 (нйпряжейиё. .близкое .к 0) если первый rt-pti-r транзистор выклю чен, то сигнал: :На шине соответствует логической в шине равен 0). Напряжение прямого смещения диодов Шоттки 7, 8 должно быть ниже нап ряжения отпирания K-p-rt- транзисторов Диоды Шоттки выполняют роль электриг ческой развязки ячеек разных слов друг от друга, входы которых объединены разрядными шинами. Благодаря этому при выборке большой ток питания, необходимый для получения высокого быстродействия, можно задать только в ячейки одной выбранной стро ки. Мощность потребляемая всеми остальными ячейками накопителя, tacTaeT ся пренебрежимо малой. В накопителе, построенном на ячейках прототипа 3 , се ячейки в режиме выборки потребяют одинаковую мощность. Следовательо, применение предлагаемой ячейки амяти позволяет при сохранении того е быстрЬдействйя снизить мощность, потребляемую накопителем в режиме выборки в N раз, где N число слов накопителя. Благодаря зтому достигается полезный эффект. Фйрмула изобретения Интегральная ячейка памяти, содержащая двам-р-и-транзистора с перекрестными сйязями, третий и четвертый п-р-И транзисторы,коллекторы которых соединены соответственно с коллектором первого и первым коллектором второго м-р-п -транзистора, второй коллектор которого соединен с базой пятого n-p-tt - транзистора, а коллектор пятого - с перв.ой разрядной шиной YJ , шестой и-р-п - транзистор, коллектор которого соединен с базой третьего м-р-и - транзистора, базы первого и второго, ti-p-ti- транзисторов соединены соответственно с первым и вторым коллектором первого р-н-р - транзистора, эмиттер которого подключен к Шине питания,:базы третьего, четвеЕ того и пятого tt-p-n - транзисторов.- сбответствен.нр к первому, второму и третьему коллекторам второго р-п-р - транзистора, эмиттер которого подключен к шине выборки , эмиттеры всех rt-p- и базыр-и-р- транзисторов подключены к шине нулевого потенциала, отличающаяся тем, что, с целью снижения потребляемой мощности ячейки, она соДержит диоды Шоттки, аноды которых подключены к базам шестого и четвертого п-р-п - транзисторов соответственно, катоды - к первой и второй разрядным шинамYjWYjсоответственно, а второй р-п-р - транзистор содержит четвертый, пятый и шестой дополнительные коллекторы, подключенные соответственно к базам первого, второго и шестого п-р-п - транзисторов. Источники информации, принятые во внимание при экспертизе: 1.Журнал VEEeclhornce , 1972, 46, I 4, р.83. 2.Журнал 3EEEJ of ( stoteCircuils 1973, V - 8, 5, р.332. 3.Патент Франции № 2138905, М., Кл Н 01С ,.19/00 от 22.05.71.

«-Э

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с произвольной выборкой | 1977 |

|

SU769626A1 |

| Накопитель | 1989 |

|

SU1656595A1 |

| Динамический элемент памяти | 1978 |

|

SU763966A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU752482A1 |

| Элемент памяти | 1981 |

|

SU978328A1 |

| Ячейка памяти | 1974 |

|

SU546935A1 |

| Запоминающее устройство | 1977 |

|

SU769627A1 |

| ВЫХОДНАЯ СХЕМА С ТРЕМЯ СОСТОЯНИЯМИ | 1992 |

|

RU2072629C1 |

| JK-триггер | 1989 |

|

SU1713091A1 |

| D-триггер | 1985 |

|

SU1332380A1 |

Авторы

Даты

1977-07-25—Публикация

1973-12-27—Подача