Изобретение относится к запоминакнцим устройствам и может быть использовано при создании вычислительных систем, работгиощих со словами информации различной длины, а также при необходимости параллельного обмена инфо1Ж1ацией с группами устройств.

Известно запоминающее устройство с переменным форматом данных, в котором применяется разбиение памяти на блоки и циклическое считывание информации из этих блоков, причем порядок обхода блоков изменяется -1,

Недостатком данного устройства является низкая надежность.

Наиболее близким к предлагаемому является запоминающее устройство с переменньм форматом данных, содержащее блоки ЗУ, дешифратор номера блока, элемент ИЛИ, ЗУ слов, переключатели, управляющую шину режима, адресные шины, общую шину данных и выходную шину данных, причем адресные шины подключены к. входам дешифраторов номеров блока и к первым входам ЗУ слов, выход дешифратора номера блока подключен к первому йходу элемента ИЛИ, шина управления режимом подключена к другому входу элемента ИЛИ и к первым входам переключателей, выход элемента ИЛИ подключен к другому входу ЗУ слов, выход которого подключен к вторым входам первого и второго переключателей, выход первого переключателя подключен к общей шине данных и к второму входу третьего переключателя, выходу второго и третьего переключателей подключены к второй шине данных 2.

10

Недостатком известного устройства является низкая надежность, так как в нем не предусмотрена защита зон памяти, используеких двумя различными абонентами, а также затрудне15но совмещение режимов вывода данных и режима вычислений, что приводит к сниженню быстродействия устройства.

Цель изобретения - повышение быстродействия устройства.

20

Поставленная цель достигается тем, что в запоминаккдее устройство с переменным форматом данных, содержащее накопители, первые входы которых объединены и являются управляющим 25 входом устройства, и первый регистр, введены блоки коррекции адреса, матрицы коммутаторов, блок выборки, информации, группы регистров, даиифратор и второй регистр, причем выход

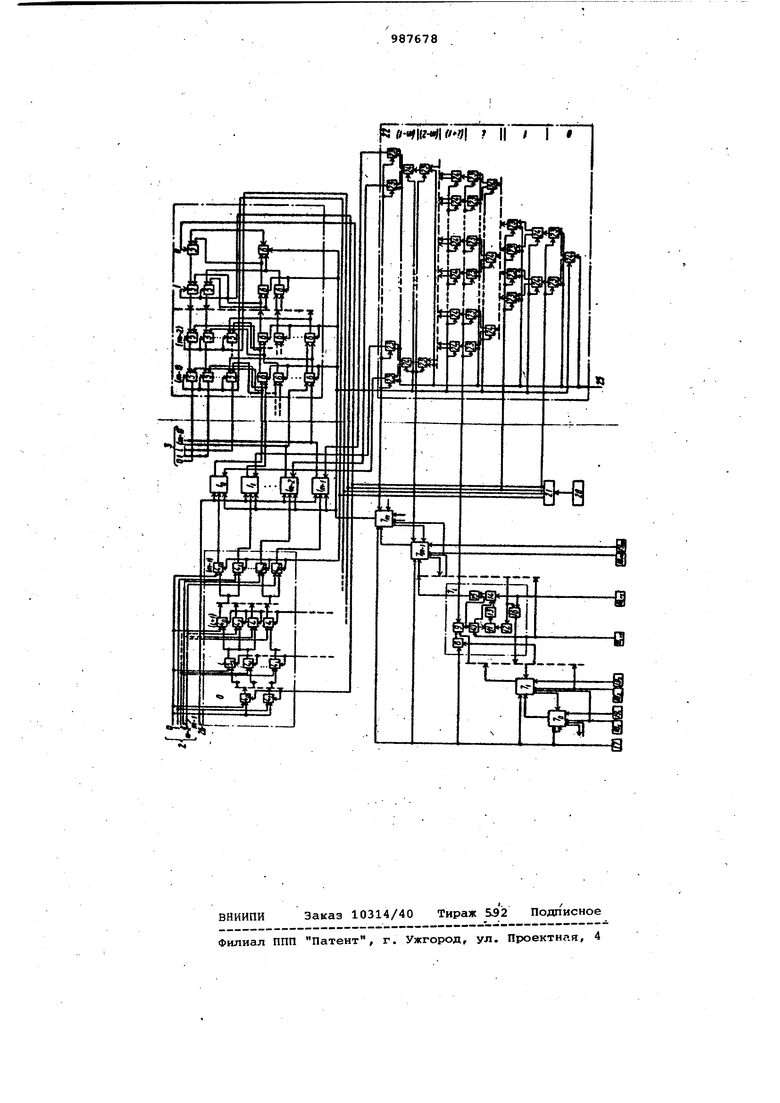

30 первого регистра подключен к первым входам блоков коррекции адреса, вторые входы которых соединены с первыми входами коммутаторов первой и второй матриц, одними из входов блока выборки информации и выходами дешифратора, вход которого подключен выходу второго регистра, первый выход каждого блока коррекции адреса, кроме последнего, соединен с третьим входом последующего блока коррекции адреса, второй выход и чет вертый вход каждого блока коррекции адреса,кроме первог;о,подключены соот ветственно к пятому и шестому входам предыдущего блока коррекции адреса,вы ходы регистров первой и второй групп .соединены соответственно с шестыми и седьмыми входами соответствующих бло ков коррекции адреса, первый выход последнего йэ которых подключен к вторым входам накопителей, первым входом коммутаторов третьей матрицы и другому входу блока выборки информации, вторые входы коммутаторов каж дого столбца, кроме первого,первой матрицы соединены с выходами коммутаторов предыдущего столбца первой матрицы, выходы коммутаторов последнего столбца первой матрицы подключены к третьим входам накопителей, вторые входы коммутаторов каждого столбца, кроме последнегр матрицы и вторые и третьи входы коммутаторов каждого столбца, кроме последнего, третьей матрицы соединены с выходами коммутаторов последующего столбца третьей матрицы, третьи входы одних из коммутаторов каждого столбца второй матрицы подключены к выходам коммутаторов соответствующей строки предыдущего столбца второй матрицы, а третьи входы других коммутаторов каждого столбца второй матрицы - к выходам коммутаторов соответствующего столбца третьей матрицы, вторые и третьи входы комму таторов последнего столбца третьей матрицы соединены с выходами накопителей, выходы одних из накопителей соединены с вторыми входами коммутаторов последнего столбца второй матрицы, выходы которых являются одними из выходов устройства, выходы других накопителей являются другими выходами устройства, четвертые входы накопителей соединены с выходами блока выборки информации, управляющие входы которого являются входами выборки устройства, информационными входами которого являются вторые вхо ды коммутаторов первого столбца первой матрицы и третьи входы кс 1мутаторов первой матрицы. . , Кроме того, каждый блок коррекции идреса содержит сумматоры по модулк два, коммутаторы, вычитатели,шифратор и умножитель, причем выход пер вого сумматора по модулю два подключен, к первому входу первого коммутатора выход которого соединен с первым входом первого вычитателя, выходы которого подключены соответственно к первому входу второго коммутатора и первому входу умножителя, второй вход которого соединен с выходом второго сумматора по модулю два, вход которого подключен к выходу второго коммутатора, второй вход которого соединен с выходом шифратора, входы третьего .сумматора по модулю два подключены соответственно к выходу первого коммутатора и выходу умножителя, а выход является первым выходом блока, входами которого с первого по четвертый являются первый вход первого сумматора по модулю два, второй и третий входы первого коммутатора и второй вход первого сумматора по модулю два, вход шифратора подключен к первому входу второго вычитателя и является пятым входом блока, шестым входом которого является второй вход второго коммутатора, третий вход умножителя, является седьмым входом блока и соединен с вторым входом второго вычитателя, выход которого является вто- рым выходом блока. При этом блок выборки информации содержит группы коммутаторов и мультиплексоров по числу накопителей,/ причем первые входы коммутаторов каждой группы объединены и являются одними из входов блока, первые входы мультиплексоров групп являются другим входом блока, второй вход мультиплексора первой группы и вторые входы коммутаторов групп являются управляющими входами блока, первый и второй выходы мультиплексоров каждой группы подключены к третьим входам соответствующих коммутаторов одноименной группы, выходы коммутаторов каждой группы, кроме последней, соединены с входами соответствующих мультиплексоров последующей группы, выходы коммутаторов последней.группы являются выходами блока. На чертеже изображена функциональная схема предлагаемого устройства. Устройство содержит накопители 1д-1, где m 7 1 - целое число, информационные входы 2(j-2 и информационные выходы ЗО-ЗУИ- первую матрицу коммутаторов 4, состоящую из 1 от О до (т-1) столбцов по j от О до i коммутаторов 4 в столбце, вторую и третью матрицы коммутаторов 5 и 6 С числом столбцов (т-1), блоки коррекции адреса, каждый иэ которых содержит первый сумматор 8 по модулю два, первый коммутатор 9, первый вычитатель id, второй Kot«tyтато 11, дешифратор 12, второй сумматор 13 по модулю два, умножитель 14, третий сумматор 15 по модулю/дв и второй вычитатель 16. Устройство содержит также первый регистр 17, предназначеиный для .хранеиия относительного адреса, первую группу регистров , предназначенных для хранения адреса начала участка памяти, вторую группу регистров 1Яг19„, предназначенных для установки {размера участка, второй регистр 20, предназначенный для хранения кода формата данных, дешифратор 21 и блок 22 выборки информации, содержащий m групп коммутаторов 23 и мультиплек соров 24. На чертеже обозначены входы 25 выборки и управляющий вход 26 устройства. Количество накопителей l lrn-i Рйвно 2 с объемсж N и длиной слова 6 разрядов (где Ми g - це лые числа). Устройство работает следующим образом. Со словами переменной длины заг поминакщее устройство работает таким образом, что по заданн 4у гщресу может быть произведена запись или считывание слов.с информационной дли ной, определяемой типом формата данных, при этом Ксццдому циклу работы памяти соответствует свой формат дан ных... В процессе работу память разбивается на участки, ячейки которых используются при работе с Форматом определенного типа. Участок памяти задается адресом начала участка А| и размером М, а в пределах участка соблюдается относительная адресация. При работе устройства с одним из фор матов данных реализуется обход участ ков памяти, отведенных для работы с другими форматами данных, и организуется параллельная работа 2 накопи телей . При работе с т-ым стаЕиаим форматом одновременно работают все накопители 1(,-1, позтому разбиение памяти на участки начинается со старшего формата. Объем памяти по этому формату равен N. Если при этсм задан размер учас ка памяти, то объем памяти, который может использоваться при работе с (т-1)-ым фоЕялатом, уменьшается и составляет 2( V. Что№1 при работе с (т-1) форматом обойти участок памяти, отведенный старшему формату, адреспамяти следует несколько скорректировать.. Эту операцию выполняют блоки . На выходе блока формируется физический адрес памяти, соответствующий заданному формату. Каждый из блоков 7„-7/) ф01Ж ирует адрес памяти Aj, и величину объема памяти Vf . СКлсл адреса памяти состоит в том, что при нулевых участкс1Х памяти форматов, старших Ч.&И 1, он равен физическому адресу памяти А , при этом объем памяти по i-му формату равен N (2)-разрядных слов. Формирование адреса памяти А происходит следукяцим образом. На первый вход сумматора 8 с регистра 17 поступает относительный адрес А, где он складывается с адресом начала зоны Ац, который поступает на второй вход сумматора 8 с 1-го регистра 18. Полученная сумма (А + ) подается на первый вход коммутатора 9, а йа его .вход подается, адрес памяти Aj,., предыдущего блока . При наличии на втором входе ксммутатора 9 единичного управляющего сигнала-, который соответствует работе памяти с i-ым форматом, коррекции подвергается либо абсолютный адрес по 1-му формату (А + АН), либо адрес А),(. Формование адреса памяти А производится в соответствии со следующим выражением. д .,; ()ми,,.,. где Е(Х) - функция вьщеления целой части аргумента X; А „ - адрес на выходе коммута- . тора 9. Приведенное выражение реализуется следуюцим образом. На первый вход вычитателя 10 lioступает адрес АК с выхода коммутатора 9, а на второй вход - адрес начала зоны Aн(f, с. (1+1)-:го регистра 18. Таким образом, на первом выходе вычитателя 10 формируется разность (А( - ), а на втором выходе сигнал , коГорый блокирует работу умножителя 14. Операция деления на реализуется путем соответствующей коммутации разрядных шин с первогЪ выхода вычитателя 10 на вход сумматсэра 13. Указанную коммутацию выполняет коммутатор 11, при этом порядок кой тации задается шифратором 12, который формирует сигналы управления в зависимости от величины . , подаваемой на его ;Вход с выхода вычитателя 16 блока i) дая того, чтобы операцию деления на . свести к операции сдвига, которую в даннс случае выполняет коммутатор 11, необходимо, чтоейл величина V;(.jf равнялась целой степени ДВОЙКИ, например, (где q - целое число). Чтобы это условие соблюдалось для всех форматов, требуется размеры участков памяти М задавать определенным образом, а именно M,-i(aV,--V,.,)-..

На сумматоре 13 к частномуот деления прибавляется единица и полученная константа подается на второй вход умножителя 14. Функция выделения целой части реализуется путем подачи на второй вход умножителя 14 только целой части суммы с в гхоДа сумматора 13.

Умножитель 14 реализует операцию умножения значения размера участка памяти, подаваемого на. третий вход умножителя 14 с (1+1) регистра 19, на константу, поступающую с выхода сумматора 13. При наличии единичного сигнала на первом входе умножителя 14 происходит блокировка умножения, т.е. реализуется умножение на ноль.

Адрес А формируется на выходе сумматора 15 в результате сложения с выхода коммутатора 9 и умножения с выхода умножителя 14.

Шлчисление объема памяти по i-му формату производится в соответствии с выражением

N-2CV,-p,-M-,)Операция вычитания реализуется на вычислителе 16 блока IJ , на пятый вход которого поступает значение V с выхода вычислителя 16 последующего блока 7.,, а на седьмой вход - значение размера М участка памяти соответствующего регистра 19. Умножение на два производится путем соответствующего соединения разрядных шин на выходе вычислителя 16.

При работе с 1-ым форматом в режиме записи производится коммутация соответствующих входов 2 на входы всех групп параллельно работающих накопителей IQ-,, Режим записи устанавливается сигналом по входу 26 на всех накопителях IO-IMI( одновременно. Выбор той или иной группы, из накопителей iQ-lm- осуществляется блоком 22 в соответствии с физическим адресом памяти по сигналсш, поступающим на входы 25.

Каждый из коммутаторов 4 работает таким образом, что при наличии на его первом входе единичного управляющего сигнала на выходе проводится информация с второго входа, в противном случае - с третьего входа. На первые входы всех.коммутаторов 4 i-ro столбца подается управляющий сигнал с дешифратора 21, соответствующий работе с 1-ым форматом. При этом на выход:(ах всех коммута:торов 4 выбранного столбца имеет место информация с соответствующих формату данных входов 2.

На выходах коммутаторов 4(1+1) столбца находится дважды скопированная информация,с 1-го столбца, на

выводе (1+2)-fo столбца - четырежды скопированная информация и т.д.

Таким образом, на каждую группу параллельно работающих накопителей

k)lw-- производится выдача информации с одних и тех же входов 2, соответствующих 1-му формату. Например, при работе с нулевым форматом информации с входа 2 о подается на входы всех накопителей ., а блок 22 определяет, на какой именно из них должна быть записана эта информация. При работе с т-ым форматом, на кгикдый j-ый накопитель 1о-1 rti-i подается через коммутаторы 4 т-го столбца ин5 формация с входа 2 и все накопители составляют единственную группу параллельно работакнцих накопителей, причем сигнал шлборки подается на них. В режиме считывания

0 коммутаторы 5 и 6 производят подключение к выходам Зд-3п.4соответствую,щих установленному формату данных и адресу памяти информационных выходов накопителей 10-1,.

5 Управление работой коммутаторов

5осуществляется сигналеиуш с дешифратора 21.

Работой коммутатора 6 управляют с1дресные сигналы с выходов блока 7 ,

0 причем младшие разряды адреса всегда поступают на входы накопителей l,Ifn-f старшие разряды управляют работой коммутаторов 6.

Например, при работе с нулевым

5 форматом информация с выходов накопителей ljj-l выдается на выход Зд при этом длина слова pjiBHa 2 разрядов, на выходах дешифратора 21 устанавливаются нулевые значения сиг0 , а при адресации используются все разряды.

В соответствии с установленным адресом на выходах коммутаторов 5 и .

6нуле.вого .столбца имеет место счи5 танное из памяти С-разрядное слово

информации, которое затем посредством ко1«4утаторов 5 выдается на выход Зр-Зуи--.

При работе с первым формате длина слова составляет 22 разрядов, а информгщия выдается на выходы 3 к

3 . На первом выходе дешифратора 21 возникает единичный сигнгш, которь1й переключает соответствующий ксиимутатор 5 нулевого столбца таким обра.зрм, что на его выход проходит информация с выхода нулевого коммутатора 6 первого столбца Поскольку количество паргшлельно работающих групп из накопителей 10-1|ц умень0 шается вдвое, то и число разрядов адреса уменьшается на единицу. Если установлен старший формат данных, то все накопители .аОотают паргшлельно и «иформгщия считывает5 ся на все выходы 3o-3m- f. Таким образе, считанная информа ция .сначала формируется коммутатора б в слово заданной длины в соответствии с установленным форматом, а затем коммутируется на соответствую щие выходы 30-3.коммутаторами 5. Блок 22 формирует сигнгшы выборки информации из накопителей 1 в соответствии с заданным форматом да ных И адресом памяти. Работой комму таторов 23 1-ой группы управляет (ч-1)-й выход дешифратора 21, кото рый задает количество одновременно выбираеАих накопителей .. Работой мульт,иплексОррв 24 той же группы управляет соответствующий старший разряд адреса памяти, приче .управление мультиплексором 24 нуле вой труппы осуществляет старший раз ряд. Сигналы выборки поступают по вхо дам 25 на вторые входы всех коммутаторов 23, KOTOiftie производят коммутацию их на, выход только при наличии единичного управляющего сигнала с соответствующего выхода дешифратора 21, в противном случае иа выход проходит сигнгш с мультиплексора 24 одноименной группы. Таким образом, предлагаемое уст,ройство позволяет, ва -першлх, организовать работу (запись и считывание) с одной И той же памятью нескольких абонентов, работающих со сл вами информации различной длины, пр перестройка памяти. п1роисходит без потери цикла обращения -во-втор Г зализовать относительную адресгилию э пределах каждого формата и защити области памяти, используемые опреде ленным форматом, при работе с другими форйа тами за счет обхода участ ков п㹫ти и, в-третьих, организовать динамическое разбиение Ьамяти.на участки в соответствии с фо1 4атами, за счет чего становится возможным обращение к одним и тем же областям Псмяти по,различным фор матам, что значительно расширяет об ласть применения предла гаемого устройства. , . Тежнико-эконсмйчёскиё преимущест а предлагаемого запсяшнакщего устройства Заключаются в его более шлсоких по сравнению с известньм быстродействии и надежности. Формула -изобретения 1. Запоминающее устройство спеременным форматом данных у содержсццее накопители, первые входы которых объединены и являются управляющим входом устройства, и первый регистр о т л и ч а ю щ е вся тем, что, с целью повышения быстродействия устройства, в него введены блоки коррекции адреса, матрищл ,коммутаторов, блок выборки информации, группы регистров, дешифратор и второй регистр, причем выход первого регистра подключен к первым входам блоков коррек1: и адреса , вторые входы которых соеди нены с первыми входами коммутаторов первой и 33торой матриц, одними из входов блока выборки информации и выходами дешифратора, вход которого подключен к выходу второго регистра, первый выход каждого блока коррекции адреса, кроме последнего, соединен с третьим входом последующего блока коррекции адреса, второй и четвертый вход каждого-блока коррекции адреса, кроме первого, подключены соответственно к пятому и гаестому входам предыдущего блока коррекции адреса, выходы регистров первой и второй групп соединены соответственно с Шестыми и седьмыми входами со- . ответствующих блоков коррекции адреса, первый выход последнего из которых подключен к вторым входам накопителей, первым входам коммутаторов третьей матрищ: и другому входу блока выборки информации, вторые входы ксяимутаторов каждого столбца, кроме первого, первой матрицы сое- . динены с выходги ш коквлутаторов предыдущего столбца первой матрицы, выходы коммутаторов последнего столб- . ца первой матрицы подключены к трет -им входам накопителей, вто1й е входы коммутаторов каждого столбца, кроме последнего, второй матридал и вторые и третьи входы коммутаторов каждого столбца, кроме последнего, третьей матрицы сое щнены с выходами коммутаторов последукяцегр столбца третьей матрицы-, третьи входы одних из коммутаторов каждо о столбца второй матрицы подключены к выходам коммутаторов соответствующей строки предыдущего столбца второй матрицы,.а третьи входы других коммутаторов каждого столбца второй матрицы - к выходам коммутаторов соответствующего столбца матрицы, вторые и третьи входы коммутаторов последнего столбца третьей матрицы со единены с выходгши накопителей, выходы одних из накопителей -соединены с вторыми входс1ми коммутаторов последнего столбца второй матрицы, выходы которых являются одними из выходов устройства, выходы других наксэтителей являются .другими выходами устройства, четвёртые входы накопиталей соединены с выходами блока выборки информации, управляющие входа которого являются входами выборки устройства, информационными вхсщеми которого являются BTOpbie входы коммутаторов первого столбца первой мат- .

рииы|.и третьи входы коммутаторов первой матрицы.

2. Устройство по п. 1, отличающееся тем,что каждый блок коррекции адреса содержит сумматоры по модулю дваIкоммутаторы,вычитатели шифратор и умножитель, причем выход первого сумматора по модулю два подключен к первому вхору первого коюяутатора, выход которого соединен 6 первым входом первого вычиФателя/ выходы которого псдаключены соответственно к первому входу второго коммутатора и первому входу умножителя, второй вход которого соединенС выходом второго сумматора по модулю два, вход которого подключен к выходу второго коммутатора, второй вход которого соединен с выходом шифратора, входы третьего сумматора по модулю два подключены соответственно к выходу первого коммутатора и выходу умножителя, а выход является первым выходом блока, входами которого с первого по четвертый являются первый вход первого сумматора по модулю два ,о и торой и третей входы первого коммутатора и второй вход первого сумматора по модулю два, вход шифратора подключен к первому входу второго вычитателя и является входом блока, шестым входом которого является второй вход второго коммутатора, третий вход умножитейя являетсяседьмым входе блока и соединен с вторым входом второго вычитателя, выход которого является вторым выходом блока.

3. Устройство по пп. I и 2, о тличающееся тем, что блок выборки инфо1 1ации содержит группы коммутаторов и мультиплексоров по числу накопителей, причем первые вхоQ ды коммутаторов каждой группы объединены и являются одними из входов блока, первые входы мульиплексоров групп являются другим входом блока, второй вход мультиплексора первой группы и. вторые входа коммутаторов групп являются управляювдгода входами блока, первый и второй выходы муль- / типлексоров каждой группы подключены к третьим входам соответствующих коммутаторов одноименной группы, ходы коммутаторов каждой группь, кроме последней, соединены с входами соответствукщих мультиплексоров последующей группы, выводы коммутаторов последней группы являются выхо5 дами блока.

Источники информации, принятые во внимание при экспертизе

1.Патент Великобритании № 1524135, 0 кл. G 4 С,опублик. 1978.

2.Патент США 4092728,

кл. G Об F 3/00, опублик. 1976 . (прототип).

() МГ Г

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровая адаптивная антенная система | 1990 |

|

SU1810943A1 |

| Устройство для умножения | 1986 |

|

SU1432506A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439618A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439617A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Устройство для сопряжения вычислительной машины с устройством ввода изображения | 1985 |

|

SU1260967A1 |

| Оперативное запоминающее устройство для растрового дисплейного терминала | 1988 |

|

SU1564692A1 |

| Модулярное устройство вычисления систем линейных алгебраических уравнений | 2015 |

|

RU2611963C1 |

| Устройство для оценки степени оптимальности размещения в многопроцессорных кубических циклических системах при направленной передаче информации | 2017 |

|

RU2727555C2 |

Авторы

Даты

1983-01-07—Публикация

1981-08-10—Подача