2. Делитель частоты, содержащий первый и второй К-триггеры, входы синхронизации которых соединены с первой входной шиной, К-вход первого ЗК-триггера соединен с шиной логической единицы, и первую выходную шину, отличающийс я тем, что, с целью расширения функциональных возможностей путем обеспечения возможности настройки, позволяющей изменять коэффициент деления, в него введены первый и второй элементы И, элемент ИЛИ, элв мент И-НЕ, первый и второй элемен,ты НЕ, вторая и третья входные шины и вторая выходная шина, причем первая выходная шина соединена с инверсньм выходом первого К-триггера и с первым входом первого

87261

элемента И, второй вход которого соединен с второй входной шиной и через первый элемент НЕ - с первым входом второго элемента И, второй .вход которого соединен с третьей входной шиной и с первым входом элемента И-НЕ, а выход с первым входом элемента ИЛИ, второй вход которого через второй элемент НЕ соединен с К-входом второго ОК-триггера, 3 -вход которого соединен с выходом элемента ИЛИ,второй вход которого соединен с выходом первого элемента И,причем прямой выход второго ЗК-триггера соединен с второй выходной шиной,инверсный выход - с вторым входом элемента И-НЕ, выход которого соединен с 3 -входом первого ЗК-триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Синхронный делитель частоты на 16 | 1984 |

|

SU1225010A1 |

| Синхронный делитель частоты на 9 на @ -триггерах | 1983 |

|

SU1148118A1 |

| Резервированный делитель частоты следования импульсов | 1986 |

|

SU1367152A2 |

| Делитель частоты следования импульсов | 1981 |

|

SU980292A1 |

| Синхронный делитель частоты на 11 на @ -триггерах | 1983 |

|

SU1150759A1 |

| Устройство для дискретной регулировки фазы | 1982 |

|

SU1027639A1 |

| Счетчик импульсов | 1977 |

|

SU784003A1 |

| Резервированный делитель частоты | 1983 |

|

SU1128389A1 |

| Устройство для вычитания частот двух независимых сигналов | 1976 |

|

SU599227A1 |

| Делитель частоты с целочисленным коэффициентом деления | 1983 |

|

SU1095414A1 |

1. Делитель частоты, содержащий первый и второй К-триггеры, входы синхронизации которых соединены с первой входной шиной, К-вход первого ДК-триггера соединен с шиной логической единицы, и первую выходную шину, отличающийся тем, что, с целью расширения функциональных возможностей путем обеспечения возможности настройки, позволяющей изменять коэффициент деления, в него введены первый, втор и третий элементы И, элемент ИЛИ, первый и второй элементы НЕ, втора и третья входные шины и вторая вых ная шина, причем первая- выходная шина соединена с первым входом первого элемента И и с прямым выходом первого ЗК-триггера, вторая входная шина соединена с вторым входом первого элемента И и через первый элемент НЕ - с первым входоь второго элемента И, второй вход которого соединен с третьей входной шиной и с первым входом третьего i элемента И, а выход соединен с первым входом элемента ИЛИ, выход (Л которого соединен с второй выходной шиной, второй вход - с выходом первого элемента И и с вторым входом третьего элемента И, выход которого соединен с Л -входом второго ЛК-триггера и через второй элемент НЕ с К-входом того же ЗК-триггера, инверсный выход которого соединен с 3 -входом первого ЗК-триггера.

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и вычислительной техники для построения программируемых делителей частоты с целочисленным коэффициентом деления.

Цель изобретения - расширение функциональных возможностей путем обеспечения -возможности настройки, позволякицей изменять коэффициент деления путем построения наращиваемых регулярных и однородных делителей частоты с программируемым коэффициентом деления.

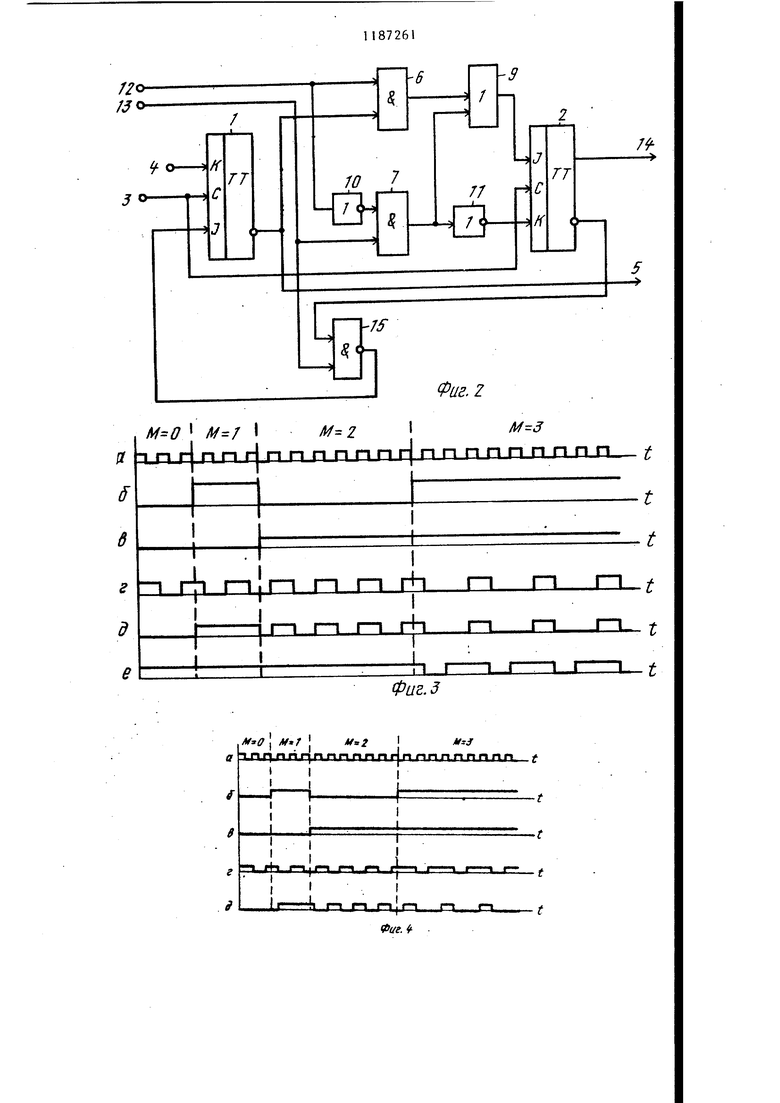

На фиг. 1 и 2 представлены электрические функциональные схемы делителей частоты, выполненных соответственно по первому и второму вариантам; на фиг. 3 и 4 - временные диаграммы, поясняющие работу делителей частоты, выполненных по первому и второму вариантам соответственно; на фиг. 5 - пример реализации на делителях частоты структурной схемы делителя частоты с программируемым коэффициентом деления; на фиг. 6 - структурная схема делителя частоты на пять; на фиг. 7 - временная диаграмма, поясняняцая его работу.

Делитель частоты по первому варианту (фиг. 1) содержит первый 1 и второй 2 D К-триггеры, входы синхронизации которых соединены

с первой входной шиной 3, К-вход первого ДК-триггера 1 соединен с шиной 4 логической единицы, первую выходную шину 5. первый 6. второй 7 и третий 8 элементы И,элемент ИЛИ 9,

первый 10 и второй 11 элементы НЕ, вторую 12 и третью 13 входные шины и вторую выходную шину 14, причем, первая выходная шина 5 соединена с первым входом первого элемен. та И 6 и с прямым выходом первого ЗК-триггера 1, вторая входная шина

12соединена с вторьм входом первого элемента И 6 и через первый элемент НЕ 10 - с первым входом второго

элемента И 7, второй вход которого . соединен с третьей входной шиной

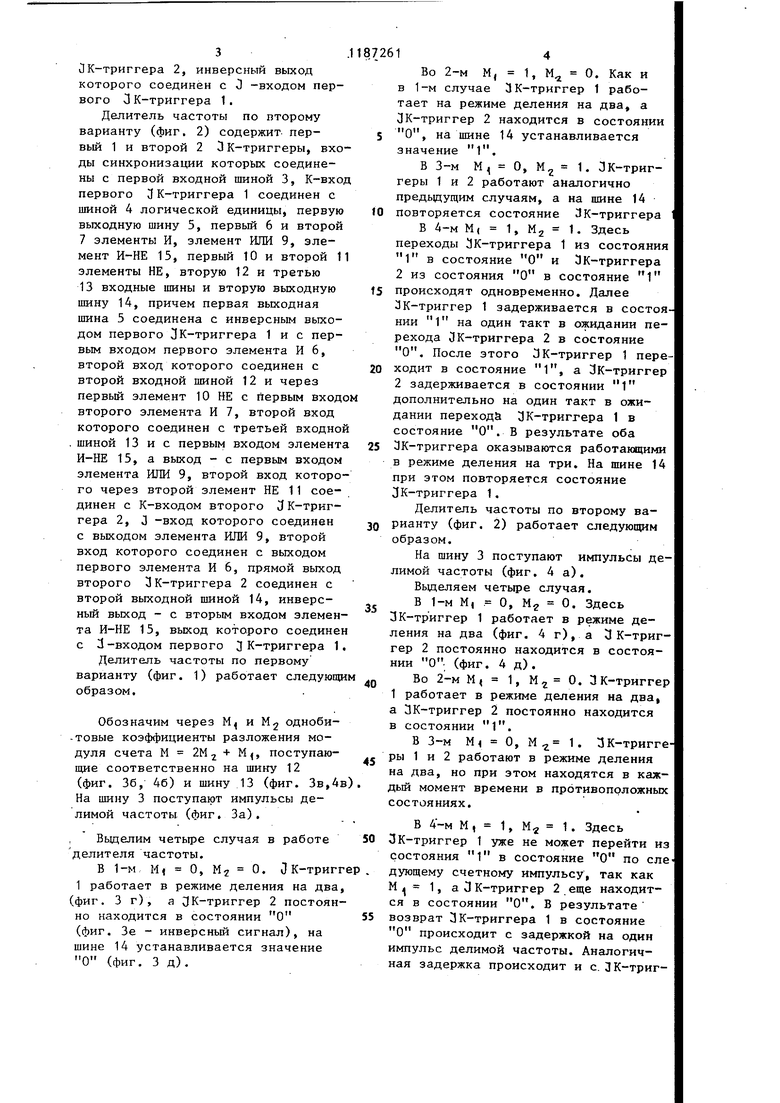

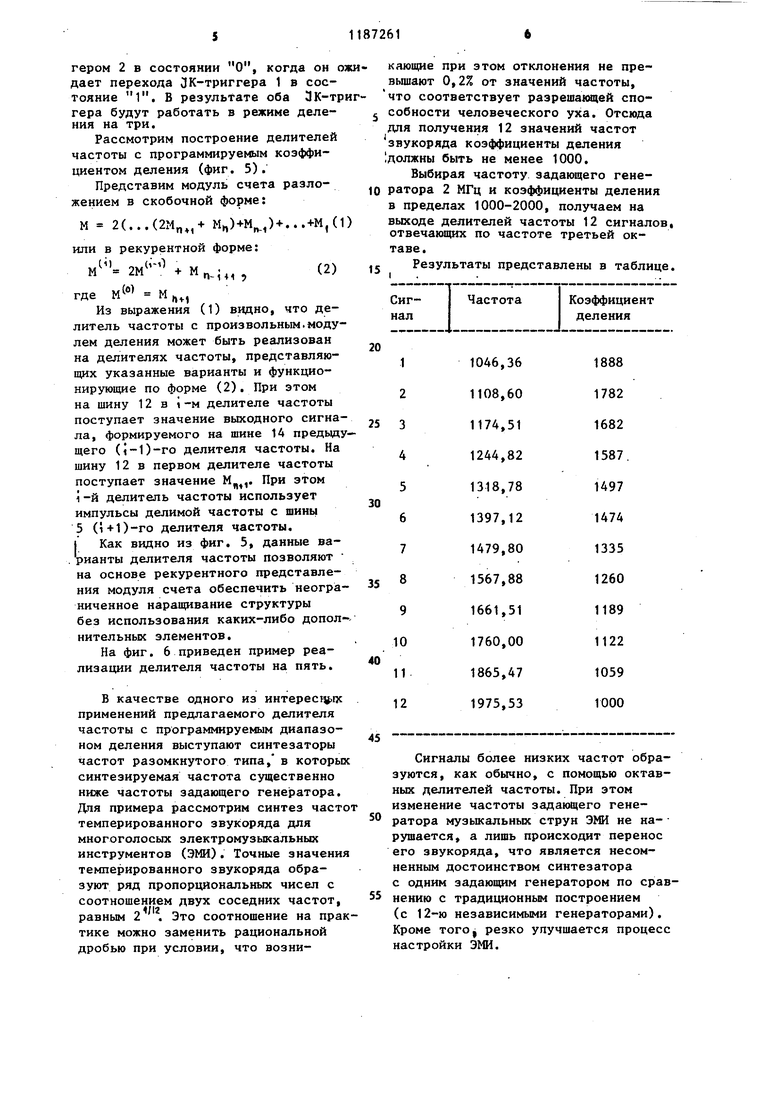

13и с первым входом третьего элемента И 8, а выход соединен с пер.вым входом элемента ИЛИ 9, выход которого соединен с второй выходной шиной 14, второй вход - с вьпсодом первого элемента Ибис вторым входом третьего элемента И 8, выход которого соединен с О -входом второго ОК-триггера 2 и через второй элемент НЕ 11 с К-входом того же ЛК-триггера 2, инверсный выход которого соединен с О -входом первого ЛК-триггера 1. Делитель частоты по второму варианту (фиг. 2) содержит первый 1 и второй 2 Зк-триггеры, вхо ды синхронизации которых соединены с первой входной шиной 3, К-вхо первого J К-триггера 1 соединен с шиной 4 логической единицы, первую выходную шину 5, первый 6 и второй 7 элементы И, элемент ИЛИ 9, элемент И-НЕ 15, первый 10 и второй 1 элементы НЕ, вторую 12 и третью 13 входные шины и вторую выходную шину 14, причем первая вькодная шина 5 соединена с инверсным выходом первого ЛК-триггера 1 и с первым входом первого элемента И 6, второй вход которого соединен с второй входной шиной 12 и через первый элемент 10 НЕ с первым вход второго элемента И 7, второй вход которого соединен с третьей входно шиной 13 и с первым входом элемент И-НЕ 15, а выход - с первым входом элемента ИЛИ 9, второй вход которо го через второй элемент НЕ 11 соединен с К-входом второго 3 К-триггера 2, J -вход которого соединен с выходом элемента ИЛИ 9, второй вход которого соединен с выходом первого элемента И 6, прямой выход второго 3К-триггера 2 соединен с второй выходной шиной 14, инверсный выход - с вторым входом элемен та И-НЕ 15, выход которого соедине с 3-входом первого 3К-триггера 1 Делитель частоты по первому варианту (фиг. 1) работает следующ образом. Обозначим через М и Mj одноби-товые коэффициенты разложения модуля счета М 2М + М, поступающие соответственно на шину 12 (фиг. 36, 46) и шину 13 (фиг. Зв,4 На шину 3 поступают импульсы делимой частоты (фиг. За). , Вьщелим четыре случая в работе делителя частоты. В 1-м М, О, Мг 0. jK-триг 1 работает в режиме деления на два (фиг. 3 г), а ОК-триггер 2 постоян но находится в состоянии О (фиг. Зе - инверсный сигнал), на шине 14 устанавливается значение О (фиг. 3 д). Во 2-м М, 1, М 0. Как и в 1-м случае ЗК-триггер 1 работает на режиме деления на два, а ЛК-триггер 2 находится в состоянии О, на шине 14 устанавливается значение 1. В 3-м М, О, M,j 1. ак-триггеры 1 и 2 работают аналогично предьщущим случаям, а на шине 14 повторяется состояние ЗК-триггера В 4-м М( 1, Mj 1. Здесь переходы ЗК-триггара 1 из состояния 1 в состояние О и ЗК-триггера 2 из состояния О в состояние 1 происходят одновременно. Далее ЗК-триггер 1 задерживается в состоянии 1 на один такт в ожидании перехода ЛК-триггера 2 в состояние О. После этого ЗК-триггер 1 переходит в состояние 1, а ЗК-триггер 2 задерживается в состоянии 1 дополнительно на один такт в ожидании перехода 3К-триггера 1 в состояние О. В результате оба ЗК-триггера оказываются работающими в режиме деления на три. На шине 14 при этом повторяется состояние ЛК-триггера 1. Делитель частоты по второму варианту (фиг. 2) работает следующим образом. На шину 3 поступают импульсы делимой частоты (фиг. 4 а). Выделяем четьфе случая. В 1-м М| 0, М 0. Здесь ЗК-триггер 1 работает в режиме деления на два (фиг. 4 г), а 3К-триггер 2 постоянно находится в состоянии О, (фиг. 4 д). Во 2-м М, 1, М 0. ЗК-триггер 1 работает в режиме деления на два, а ЗК-триггер 2 постоянно находится в состоянии 1. В 3-м MI О, М 1. ЗК-триггеры 1 и 2 работают в режиме деления на два, но при этом находятся в каждый момент времени в противоположных состояниях. В 4-м М, 1, М.г 1. Здесь ЗК-триггер 1 уже не может перейти из состояния 1 в состояние О по сле дующему счетному импульсу, так как Н 1, а J К-триггер 2 еще находится в состоянии О. В результате возврат 3К-триггера 1 в состояние О происходит с задержкой на один импульс делимой частоты. Аналогичная задержка происходит и с. ЗК-триггерои 2 в состоянии О, когда он ожидает перехода ЛК-триггера 1 в состояние 1. В результате оба ЗК-триггера будут работать в режиме деления на три.

Рассмотрим построение делителей частоты с программируемым коэффициентом деления (фиг. 5).

Представим модуль счета разложением в скобочной форме:

М 2(...(2М„, + Мк)+М,)-...+М,(1)

или в рекурентной форме:

+ М

(2)

П-141

где М

П + 1

Из выражения (1) видно, что делитель частоты с произвольным.модулем деления может быть реализован на делителях частоты, представляющих указанные варианты и функционирующие по форме (2). При этом на щину 12 в i-М делителе частоты поступает значение выходного сигнала, формируемого на шине 14 предьщу щего (i-l)-ro делителя частоты. На шину 12 в первом делителе частоты поступает значение М,. При этом 1-и делитель частоты использует импульсы делимой частоты с шинь 5 (i+1)-ro делителя частоты. I Как видно из фиг. 5, данные варианты делителя частоты позволяют на основе рекурентного представления модуля счета обеспечить неограниченное наращивание структуры без использования каких-либо дополнительных элементов.

На фиг. 6 приведен пример реализации делителя частоты на пять.

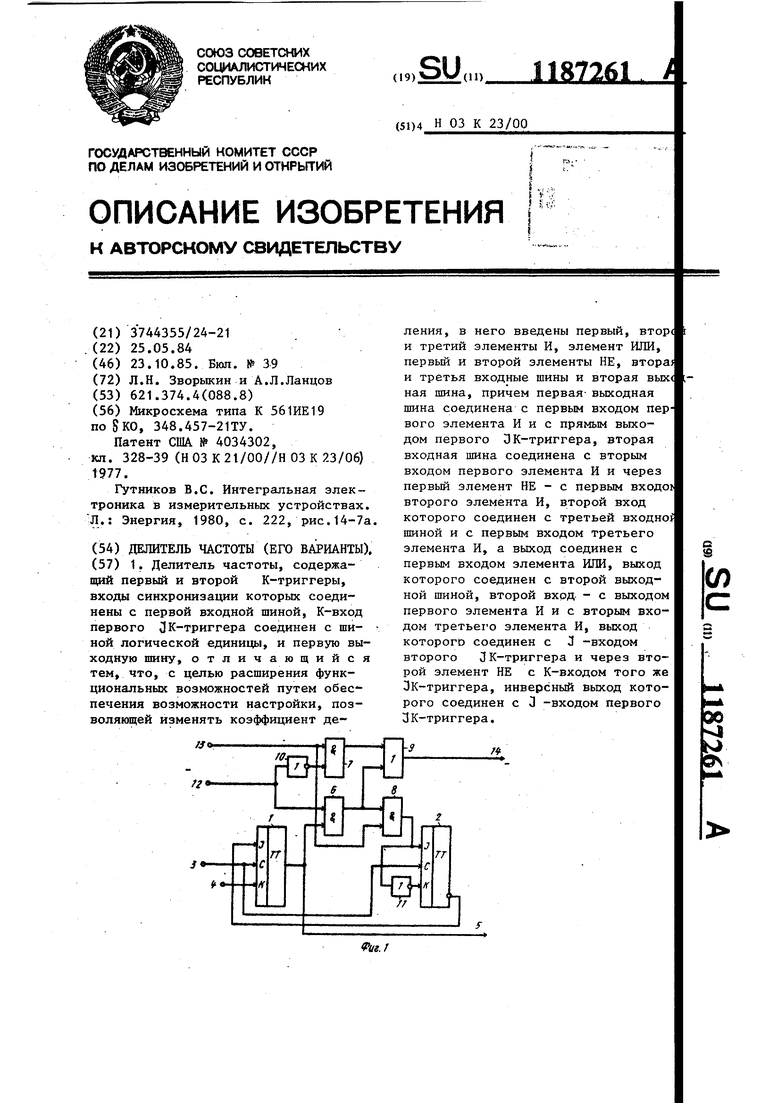

В качестве одного из интерес1| 1х применений предлагаемого делителя частоты с программируемым диапазоном деления выступают синтезаторы частот разомкнутого типа, в которых синтезируемая частота существенно ниже частоты задающего гене|ратора. Для примера рассмотрим синтез часто темперированного звукоряда для многоголосых электромузыкальных инструментов (ЭМИ). Точные значения темперированного звукоряда образуют ряд пропорциональных чисел с соотношением двух соседних частот, равным 2 . Это соотношение на практике можно заменить рациональной дробью при условии, что возникающие при этом отклонения не превышают О,2% от значений частоты, что соответствует разрешающей способности человеческого уха. Отсюда для получения 12 значений частот звукоряда коэффициенты деления должны быть не менее 1000.

Выбирая частоту задающего генератора 2 МГц и коэффициенты деления в пределах 1000-2000, получаем на выходе делителей частоты 12 сигналов, отвечающих по частоте третьей октаве. t5 Результаты представлены в таблице.

Сигналы более низких частот образуются, как обычно, с помощью октавных делителей частоты. При этом изменение частоты задающего генератора музыкальных струн ЭМИ не нарушается, а лишь происходит перенос его звукоряда, что является несомненным достоинством синтезатора с одним задающим генератором по сравнению с традиционным построением (с 12-ю независимыми генераторами). Кроме Toroj резко улучшается процесс настройки ЭМИ.

1187261

| Регенеративный приемник | 1923 |

|

SU561A1 |

| Патент США № 4034302, кл | |||

| Способ переработки сплавов меди и цинка (латуни) | 1922 |

|

SU328A1 |

| Гутников B.C | |||

| Интегральная электроника в измерительных устройствах | |||

| :Л.: Энергия, 1980, с | |||

| Камневыбирательная машина | 1921 |

|

SU222A1 |

Авторы

Даты

1985-10-23—Публикация

1984-05-25—Подача