(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство | 1978 |

|

SU788173A1 |

| Цифровая интегрирующая структура | 1974 |

|

SU674052A1 |

| Опреративное запоминающее устройство | 1976 |

|

SU645204A1 |

| Программируемое запоминающее устройство | 1977 |

|

SU736170A1 |

| Динамическое оперативное запоминающее устройство | 1987 |

|

SU1499401A1 |

| Устройство для обмена данными в многопроцессорной вычислительной системе | 1983 |

|

SU1136143A1 |

| Запоминающее устройство | 1975 |

|

SU611250A1 |

| СИНХРОННЫЙ АДАПТИВНЫЙ МУЛЬТИПЛЕКСОР | 1993 |

|

RU2078401C1 |

| Устройство коммутации | 1980 |

|

SU894866A1 |

| УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ ИНФОРМАЦИИ НА ГАЗОРАЗРЯДНОЙ ИНДИКАТОРНОЙ ПАНЕЛИ | 1993 |

|

RU2069018C1 |

Изобретение относится к вычислительной технике и может быть исполь зовано для организации программной перестановки информации в режиме разделения времени в многопроцессор ных вычислительных системах, а также в автоматизированных телефонных станциях. Известно устройство коммутации аналоговых блоков, содержащее считывающее устройство, выходы которого через дешифратор адреса шагового искателя и блок управления подключе ны к входам блока коммутации l. Однако данное устройство имеет низкое быстродействие, связанное с тем,что блок коммутации выполнен на шаговых искателях. Наиболее близким к предлагаемому является запоминающее устройство, содержащее накопитель, информационн входы которого соединены с выходам первого регистра слова, а информационные выходы - с входами второго .регистра слова, подключенного выходами к информационным выходам устройства, информационные входы которого соединены с входами первого регистра слова, первые адресные входы накопителя подключены к выходам первого дешифратора адреса, соединенного входами с выходами счетчика адреса, вторые адресные входы накопителя подключены к выходам второго дешифратора адреса, соединенного входами с выходами регистра адреса, вход которого соединен с первым выходом буферного регистра, подключенного вторым выходом к входу счетчика адреса и входами к выходам блока связи, кроме того, выходы блока управления соединены с управлящими входами накопителя, счетчика адреса регистра адреса и буферного регистра, . а входь - с выходами блока связи через регистр кода операции и дешифратор кода операции 2

. Однако это устройство имеет, |Во-первых, сложный накопитель в связи с пространственной организацией распределения в нем информации, пос-. тупеющей на входы первого регистра. 5 слова и выводимой из накопителя на входы второго регистра слова, т.е. каждый элемент памяти помимо функции хранения выполняет и функцию коммутации информации. Сложность накопи- теля этого устройства подчеркивается наличием большого количества связей; двух адресных входов, двух информационных входов и выходов и управляющих входов. Во-ЬторыХ) организация 5 ввода программы коммутации матрицы в накопитель ха эактеризуется таюхе относительно большими затратами оборудования. Необходимы дополнительные аппаратурные затраты {регистр кода 20 операции и дешифратор кода операции) для задания режимов работы и для индентифйкации-адресов, вводимых либо в регистр адреса, либо в счетчик адреса. В-третьих, наличие блока свя- 25 аи и второго дешифратора также усложняет устройство.

Цель изобретения - повышение надежности запоминающего устройства.

Поставленная цель достигается тем, что запоминающее устройство,содержащее накопитель, информационные входы которого соединены с выходами регистра слова, входы которого являются информационными входами устройства, последовательно соеди,ненные счетчик и деижфратор, входы счетчика являются одними адресными входами устройства, а выхода дешифратора подключень к адрес ньм входам постоянного накопителя, блок управления, выход которого соединен с управляющими входами счетчика, регистра слова, регистра адреса и дешифратора , содержит адресный блок и оперативный накопитель, информационные входы и выходы которого подключены к соответствующим выходам и входам регистра адреса, другие выходы которого подключены к входам дешифратора, выходы которого подключены к одним адресным входам опера tHBHOro накопителя, другие адресное входы которого подключены к выходам адресного блока, входы которого являются адресными входами устройства а управляющие входы адресного блока соединены с выходом блока управления.

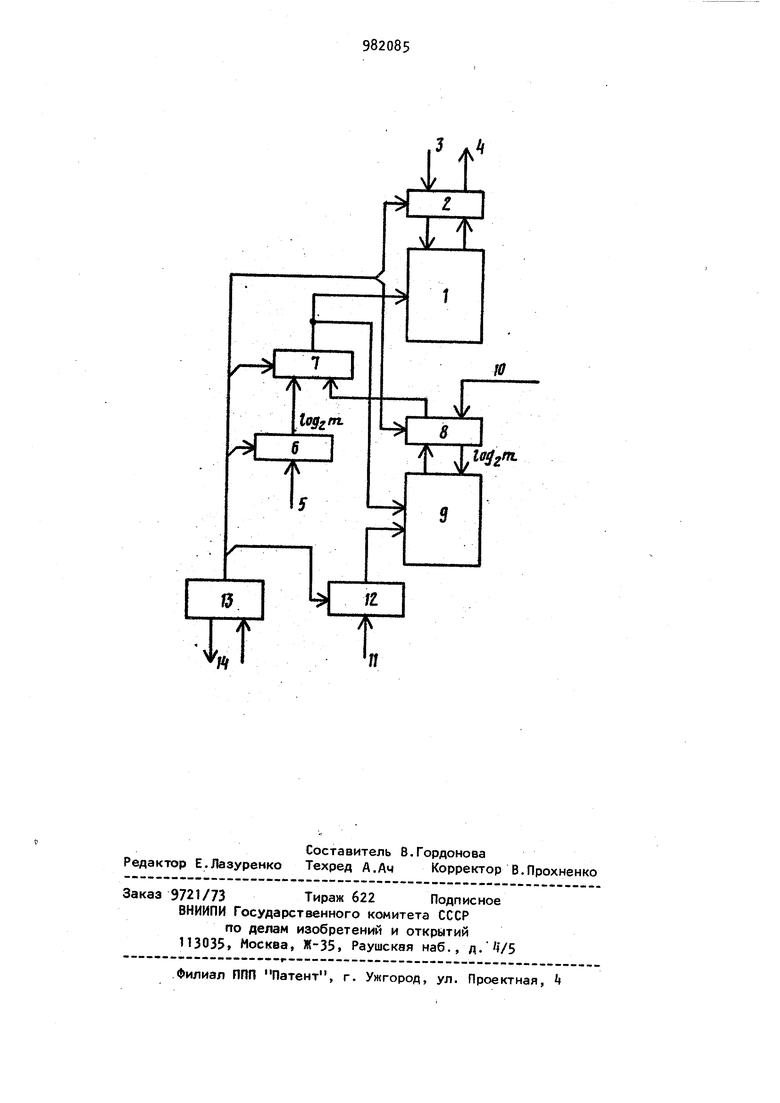

На чертеже изображено устройство.

Устройство содержит постоянный накопитель 1, регистр 2 слова, информационные входы 3 и выходы k, адресные входы 5, счетчик 6, дешифратор 7, регистр 8 адреса, оперативный накопитель 9 адресные входы 10 и 11, адресный блок 12, блок 13 управления,управляющие входы-выходы И. .

Устройство работает следующим образом.

Устройство выполняет программируемую перестановку m информационных слов, поступающих через информационные входы 3 последовательно по словам параллельным (-разрядными кодами . Считываемые из накопителя 1 информационной памяти информационные лова на информационных выходах k устройства могут быть переставлены в соответствии с программой (массивом адресов), хранящихся в накопителе 9 управляющей памяти.

Принцип действия устройства в различных режимах работы условно можно представить следующими схемами.

Режим записи (ЗП) постоянного накопителя 1 и считывания (СЧ) оперативного накопителя 9 описывается следующим образом.

В этом режиме по одному и тому же адресу осуществляется запись слова из регистра 2 слова в постоянный накопитель 1 и считывание адреса из оперативного накопителя 9 в регистр 8 адреса.

Режим смитывания постоянного накопителя 1 и записи {ввод массива адресов через вторые адресные входы 10 устройства) оперативного накопителя 9 можно представить так, что в первом режиме пр оизводится естественная адресация ячеек постоянных накопителей t и опера травного накопителя 9 с помощью cчetмикa 6 и дешифратора 7 а so втором режимепринудительная адресация ячеек постоянного накопителя 1 с помощью регистра 8 адреса и дешифратора 7 и ячеек оперативного накопителя 9 с помощью блока 12.

Режимы работы устройства задает блок 13 управления, формирующий различные последовательности сигналов.

Предлагаемое запоминающее устройство является экономичньм и быстродействующим, позволякщим соединить любой временной канал уплотненного информационного входа 3 с любым вре менным каналом уплотненного информа ционного выхода i. Пространственным эквивалентом устройства является запоминающее устройство (прототип), выполняющее пространственные произвольные соединения между m входами и m выходам ин юрмация через которые Передается последовательными кодами. Сравнительная оценка устройства. Сложность накопителя прототипа оценивается сложностью его запоминаю|1цей частиN и сложностью логической части INT, выполняющей функцию коммут ции. Емкость памяти прототипа и число логических схем И - N - т , Кроме того,необходимо иметь в бло Ке связи, либо во внешней памяти, подключаемой к блоку связи, Va mPog m Б и Т памяти для хранения программы коммутации, вводимой в за поминающее устройство (пространствен ный коммутатор). При m В (относительно одинаково быстродействии сравниваемых. устройст общая емкость коммутаторного запоми нающего устройства , V - V 4 Vo W ш е оро, W, но N 4т. Таким образом, прототип имеет , более сложную логическую часть накопителя, дополнительные регистр и дешифратор кода операций и более сложный блок связи. При более быстродействующими является предлагаемое устройство, а при наоборот более высокое .быстродействие имеет прототип. В ре.жиме настройки устройств /ввода программь коммутации) более быстродействующим (с меньшим временем доступа) оказывается предлагаемое устройство благодаря организации непосредственной связи накопителя управляющей памяти с накопителем информационной памяти. Формула изобрете.ния Запоминающее устройство, содержащее накопитель, информационные входы которого соединены с выходами регистра слова, входы которого являются информационными входами устройства, последовательно соединенные счетчик и дешифратор, входы счетчика являются одними адресными входами устройства, а выходы дешифратора подключены к (адресным входам постоянного накопитеря, блок управления, выход которого соединен с управляющими входами счет;чика, регистра слова, регистра адреса и дешифратора, отличающееся тем, что, с целью повышения надежности устройства, оно содержит адресный блок и оперативный накопитель, информационные входы и выходы которого подключены к соответствующим выходам и входам регистра адреса, другие выходы которого подключены к входам дешифратора, выходы которого подключены к одним адресным входам оперативного накопителя, другие адресные входы которого подключены к выходам адресного блока, входы которого являются адресными входами устройства, а управляющие входы адрес-ного блока соединены с выходом блока управлеИсточники информации, принятые во внимание при экспертизе 1.Лвторское свидетельство СССР № гя0392, кл. G 11 С 11/00, 1977. 2.Авторское свидетельство СССР iff 611252, кл. G 11 С 11/00, 1978.

-О

Т Т

.

/

Авторы

Даты

1982-12-15—Публикация

1981-04-24—Подача