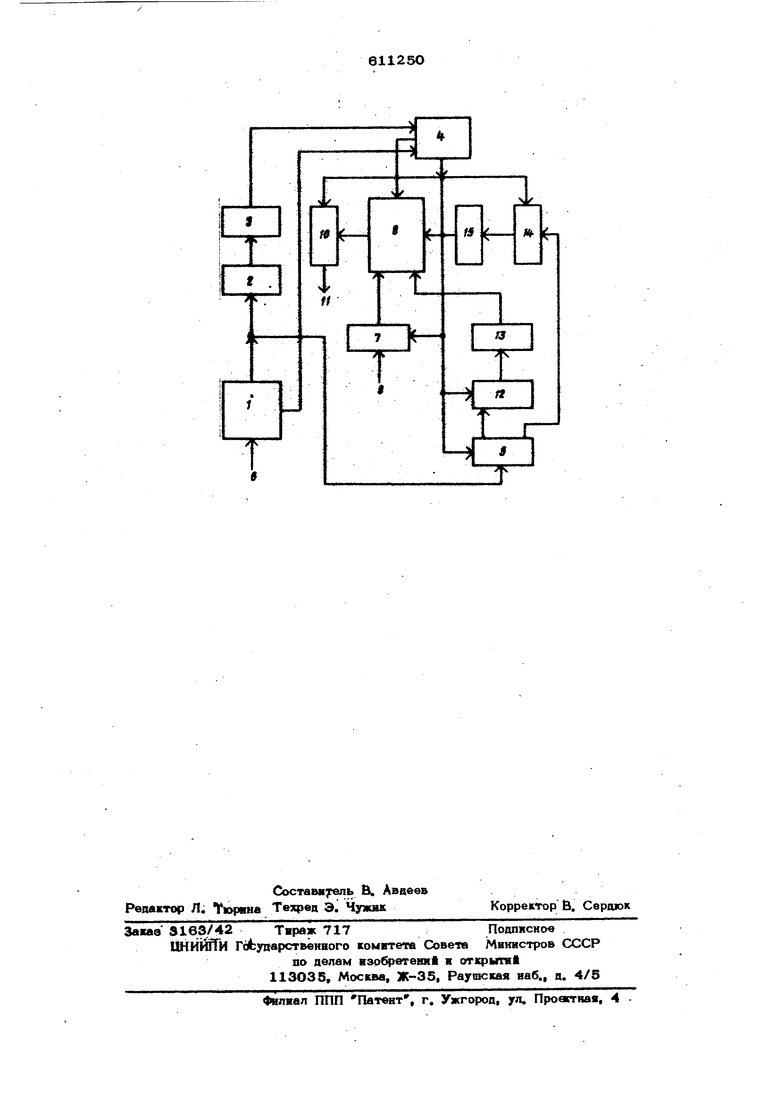

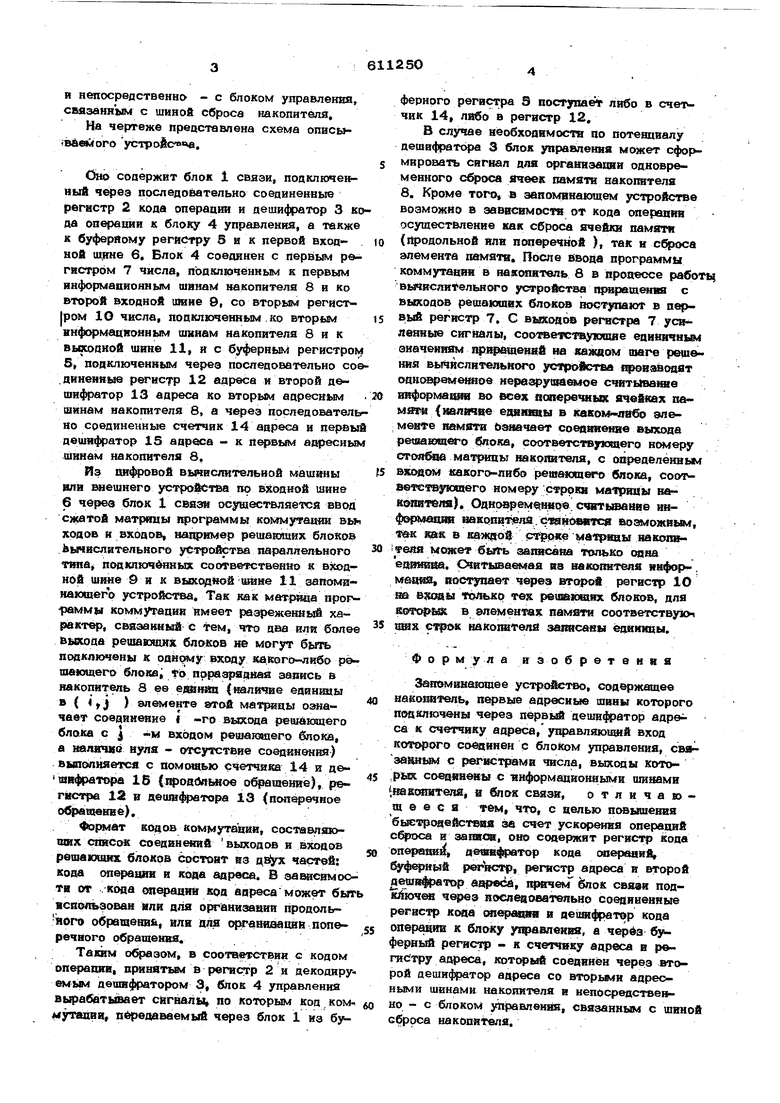

Изобретение относится к вычнслитепьной технике и может быть использовано цля организации произвольных соединений вь ходов и входов вычислительного устройства параллельного типа. Известно устройство коммутации аналоговых блоков, содержащее считывающее уст ройство, выходы которого через дешифратор адреса шагового искателя и блок управ ле{гая подключены к входам блока комм«та ови. Однако Низкое быстродействие известн го устройства вызвано тем, что блок коммутавии вьтол..ен на шаговых искателях. Наиболее близким к изобретению техническим решением запоминающее уст poftcTBo, соаержащее лакопитель, первые аа ресные швны которого подключены через первый дешифратс адреса к счетчику адреса, управляющий вход которого соединен с блоком управления, связанным с регистра ми числа, выходы которых соединены с инфо{Ж1ааионвыми шинами накопителя, и блок связи. Известное устро :тво предназвачево для хранения программы коммуташга БЬКОДОВ л входов интеграторов цифрового аиффереивяального аналваатч и имеет относвтеяьво ввэкое быстроявйст вв при завися в ваксжвтель носввдоватвльяэ ао словам матряаы 1фргрвммы коммутввяи, имеющей разреж 1вый .характер (в кажвой стрсйй или столбце маяжаы может Raxt диться только oa«ia единица). Кроме того, оргвшгзаш1Я сброса накшштелв нутем за писи нулей в ячейки вамятя ореводшт к затратам емвйв, им вжяаим место j уиравленкв перестройкой щюграммы коммуташм. Цель изобретеияя заключаетря в повышении бьютродевст я за счет ускореяия оперений сброса и записи. В мгесьюавмом устройстве это достигается тем, что оно содержит регистр кода операций, дешифратор кода операций, буфериьЛ регистр, регистр адреса и второй дешифратор адреса, прячем блок связи соеаинен через последовательно соединенные регистр кода сжерашпс дешифратор кода операпяи с блоком угфавле ВИЯ, а через буферный регистр - со счетчиком адреса и регистром адреса, которьА соединен через второй дешифратор адреса со вторыми адресными шквамн накопителя я непосредственнсх - с блоком управления, связанным с иганой сброса накопителя. На чертеже прецстввпена схема описы Ъ емого устройс в. Cfeb содержит блок 1 связи, попключе ный чфеэ последовательно соециненвые регистр 2 кода рпераави и дешифратор 3 ко да операции к блоку 4 управления, а также к буферному регистру 8 и к первой входной шине 6. Блок 4 соединен с первым регистром 7 числа, подключенным к первым информационным швнам накопителя 8 и ко второй входной июне 0, со вторым регнст|ром Ю числа, подключенным .ко вторым информационным шинам накопителя 8 и к вьоопиой шине И, и с буферным регистром 5, подключенным через последовательно сое .динеиные регистр 12 адреса и второй дешифратор 13 адреса ко вторьм адресным шинам накопителя 8, а через послед ователь но соединенные счетчик 14 адреса и первьй дешифратор 15 адреса - к aapecHtsO шинам накопителя 8, из пифровой вьтислительной мешены или Ш1ешнего устров т&а по входной шине 6 черев блок 1 связи осуществляется ввод матрицы программы коммуташш В№ ходов и входов, (шяример решагошвх блоков вычислительного устройства параллельного твпа подклю1чдш1ых соответствевно к входной ши«е @ и к швне 11 запоминающего устройс1С в. Так как мвт{мша прог раммы комм)гаоии имеет разреженный характер, связанный с тем, что два ил более Бьосода решавзцщх блонков ке могут бьпъ подключены к одному входу ка.кого-либо решающего блока ; «го прразрадная запись в накопитель 8 ее fнал{{Ч0е единшгы в ( JJ ) элементе атой озиачает соединение t -го выхода рев}вюшего блока с j -м входом решакэшего блока, а налнчко нуля - отсутстаие соедин игя) вьшолняется с помощью счетчика 14 и де шифратора 16 (ояйяьное обращение), регнстра 12 и деиш мэтора 13 (поперечное обещание). Формат коммут ии, составляющих огасок соединений выходов и входоа решающа блоков (состовт из дв1ух частей: кода стерацяи и кода адреса. В зависимос ти от .кода (хп рации код адресаможет быт яспользоваи или для органи аии продол ЕГяого обрвшевв&| или для оргатшации поперечного обрашенвя. Таким , в соответствии с кодом операции, принять&4 в регистр 2 и декодиру вмым дешифратором 3 блок 4 управления выраб;атывает сигналь по которым код ком мутации, передаваемый через блок 1 из б ферного регистра 5 nocTynaet либо в счет чик 14, либо в регистр 12. В случае необходвмоств по потенциалу дешифратора 3 блок уярввления может сфо| мировать сигнал для организаши одновременного сброса ячеек памяти накопителя 8. Кроме того, в запомвнаюшем устройстве возможно в завасвмоств от кода оперетт осуществление как сброса ячейки памяти (продольной или поперечной ), так и сброса элемента памяти. После бвода программы коммутавии в накопитель 8 в проаессе работь; вычислительного устройства приращение с выходов решающвх блоков поступают в перъьА регистр 7. С вьш}аб8 регистра 7 уси ленные сигналы, coor&evsrt VKsaie единичньм значениям прлращеивб на кажаом шаге решения вычислительного yctpoiBcT&a (шят однсмврвменное неразрушаемое счять ва1шв ш{формашя во всех поперездьвс Ячейках памяпрй {нвлачяе в каком-хпвбо элемевфе памяти Ьзначает соедаяенве выхода решэюшего бпока, соответс-гезгюшвго номеру оеояб№& матрицы 1шко1штеля, с определенным шювом какого-либо решающего блока, сооч ветсчв ощего номеру строке мачрииы вакош1«|ш). Одно8рем 1Я1р« с штьюание и1(effMfeam вакопвтеля. (| воэможйьвиг, Фбк я«ак в строже матркаы яакопвУвйя может 6tgtb з&1шсана только оава е{Цй№к&&, Считыва@(4ая из вакотггеяа иифор-. мвавг, KQCTjTnaeT регистр Ю на только тех реш&юшях блоков, для Еоторье в элементах памвти соответствухь Шх нако1гателя заш1савы единицы. формула изобретения Запоминающее устро&;тво, содержоцее наковафель, первые адресные швиы которого подключены через первый дешифратор адре са к счетчику адреса, управляющий вход которого сочинен с блоком управления, связааньы с репютрами числа, выходы кото,р|ж с информационными шивами i Kotmtens, в связи, отличающееся тем, что, с целью псюьпиевия бысфроаейстеоя за счет ускорения операций сброса и захшсн, оно содержит регис1ф кода опера 4 дешвфратор кода сшерааий, буферный регистр, регистр адреса и второй дешифратор аар«са, ёлок свяви подш1юч последовательно соединенные регис К(в (тщ)в«№а я дейшфратор кода операвив к блоку у1 вленвя, а через буферный регистр - к счетчику адреса и регистру агфеса, который соединён через вто рой деши4|)атор адреса со вторьми адресными шинамн накопителя и непосредственно - с блоком управления, связанным с шиной сброса накопиГелЯ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения цифровой вычислительной машины с периферийными устройствами | 1980 |

|

SU962899A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

| Программируемое запоминающее устройство | 1977 |

|

SU736170A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Устройство обмена данными | 1988 |

|

SU1649556A1 |

| Устройство для сопряжения процессора с памятью | 1987 |

|

SU1439605A1 |

| Устройство сопряжения | 1974 |

|

SU519704A1 |

| Запоминающее устройство | 1981 |

|

SU982085A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1019495A1 |

| Устройство для отображения информации | 1984 |

|

SU1251062A1 |

Авторы

Даты

1978-06-15—Публикация

1975-05-11—Подача