(5i) БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1984 |

|

SU1236550A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1034069A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1361632A1 |

| Устройство для сопряжения вычислительной машины с устройством ввода изображения | 1985 |

|

SU1260967A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1297115A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1048516A1 |

| Буферное запоминающее устройство для блоков отображения информации | 1986 |

|

SU1411830A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1251181A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1163358A1 |

| Буферное запоминающее устройство | 1987 |

|

SU1476476A1 |

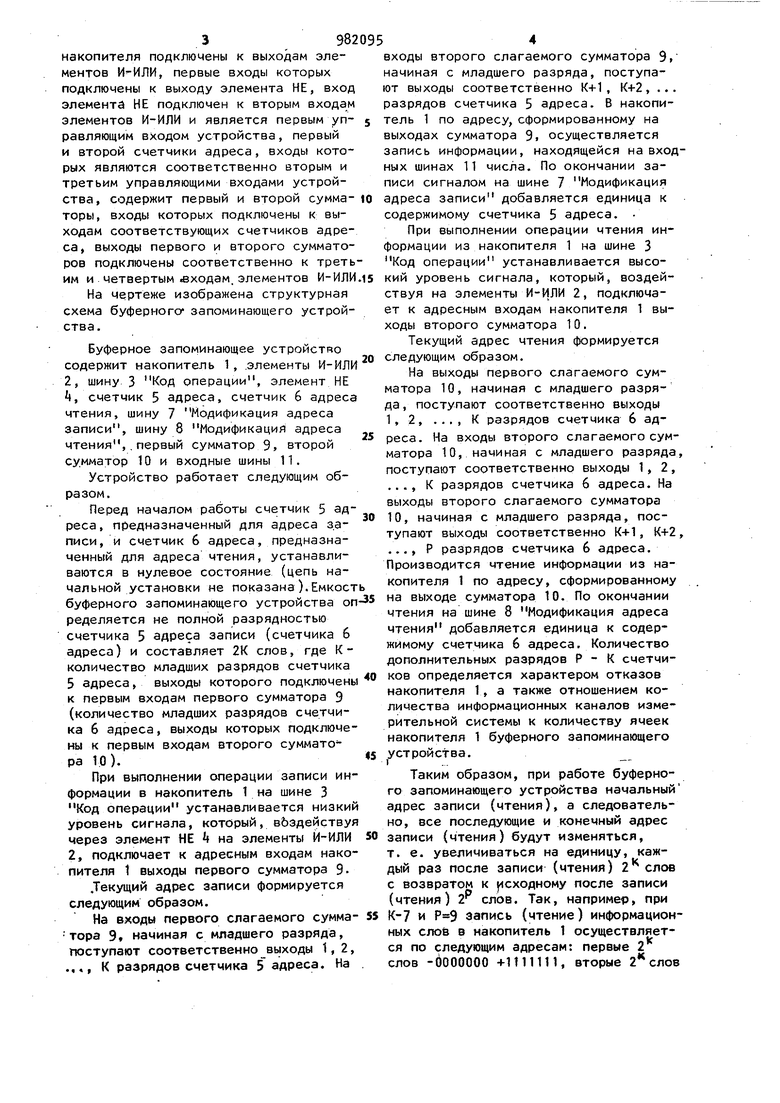

Изобретеийе относится к вычислительной технике и может быть исподьзовано в буферных запоминающих устройствах систем ввода информации многоканальных измерительных комплексов. Известно буферное запоминающее устройство, в котором Используется метод перекрестно-последовательного обращения, позволяющий осуществлять двухсторонний обмен информацией и совмещать процессы ввода в буферное запоминающее устройство и вывода информации из него Недостатком данного устройства является низкая надежность. Наиболее близким техническим решением к изобретению является буферное запоминающее устройство, содержащее накопитель, адресные входы которого подключены к выходам схем И-ЙЛИ, пер вые входы которых соединены с шиной Код операции и входом инвертора, выход которого соединен с вторыми входами схем И-ИЛИ, счетчик адреса записи и счетчик адреса чтения, входы которых соответственно подключены к шинам Модификация адреса Записи и Модификация адреса чтения Г 2. Однако использование этого устройства в системах ввода информации многоканальных измерительных комплексов, когда .последовательность опроса каналов неизменна, а их количество равно или превышает и кратно количеству ячеек буферного запоминающего устройства, отказ одной или нескольких ячеек накопителя приводит к потерям информации от одного или нескольких каналов. Цель изобретения - повышение надежности устройства за смет выравнивания вероятности потерь по каждому из каналов измерительной системы. Поставленная цель достигается тем, что буферное запоминающее устройство, содержащее накопитель, информационные входы и выходы которого являются соответственно информационными входами и выходами устройства, адресные входы 3982 накопителя подключены к выходам элементов , первые входы которых подключены к выходу элемента НЕ, вход элемента НЕ подключен к вторым входам элементов И-ИЛИ и является первым управляющим входом устройства, первый и второй счетчики адреса, входы которых являются соответственно вторым и третьим управляющими входами устройства, содержит первый и второй сумматоры, входы которых подключены к выходам соответствующих счетчиков адреса , выходы первого и второго сумматоров подключены соответственно к третьим и четвертым«входам.элементов И-ИЛИ На чертеже изображена структурная схема буферного- запоминающего устройства. Буферное запоминающее устройство содержит накопитель 1, элементы И-ИЛИ 2, шину 3 Код операции, элемент НЕ 1, счетчик 5 адреса, счетчик 6 адреса чтения, шину 7 Модификация адреса записи, шину 8 Модификация адреса чтения,,первый сумматор 9, второй сумматор 10 и входные шины 11. Устройство работает следующим образом. Перед началом работы счетчик 5 адреса , предназначенный для адреса з.аписи, и счетчик 6 адреса, предназначенный для адреса чтения, устанавливаются в нулевое состояние (цепь начальной установки не показана ).Емкост буферного запоминающего устройства оп ределяется не полной разрядностью счетчика 5 адреса записи (счетчика 6 адреса) и составляет 2К слов, где Кколичество младших разрядов счетчика 5 адреса, выходы которого подключены к первым входам первого сумматора 9 (количество младших разрядов счетчика 6 адреса, выходы которых подключены к первым входам второго сумматора 10). При выполнении операции записи информации в накопитель 1 на шине 3 Код операции устанавливается низкий уровень сигнала, который, вбздействуя через элемент НЕ k на элементы Й-ИЛИ 2, подключает к адресным входам накопителя t выходы первого сумматора 9.Текущий адрес записи формируется следующим образом. На входы первого слагаемого сумматора 9 начиная с младшего разряда, поступают соответственно выходы 1,2, .,., К разрядов счетчика 5 адреса. На входы второго слагаемого сумматора 9, начиная с младшего разряда, поступают выходы соответственно К+1, К+2, ... разрядов счетчика 5 адреса. В накопитель 1 по адресу, сформированному на выходах сумматора 9. осуществляется запись информации, находящейся на входных шинах 11 числа. По окончании записи сигналом на шине 7 Модификация адреса записи добавляется единица к содержимому счетчика 5 адреса. При выполнении операции чтения информации из накопителя 1 на шине 3 Код операции устанавливается высокий уровень сигнала, который, воздействуя на элементы И-ИЛИ 2, подключает к адресным входам накопителя 1 выходы второго сумматора 10. Текущий адрес чтения формируется следующим образом. На выходы первого слагаемого сумматора 10, начиная с младшего разряда , поступают соответственно выходы 1, 2К разрядов счетчика 6 адреса. На входы второго слагаемого сумматора 10, начиная с младшего разряда, поступают соответственно выходы 1, 2, ..., К разрядов счетчика 6 адреса. На выходы второго слагаемого сумматора 10, начиная с младшего разряда, поступают выходы соответственно К+1, К+2, ..., Р разрядов счетчика 6 адреса. Производится чтение информации из накопителя 1 по адресу, сформированному на выходе сумматора 10. По окончании 8 Модификация адреса чтения добавляется единица к содержимому счетчика 6 адреса. Количество дополнительных разрядов Р - К счетчиков определяется характером отказов накопителя 1, а также отношением количества информационных каналов измерительной системы к количеству ячеек накопителя 1 буферного запоминающего ycTpoActsa. Таким образом, при работе буферного запоминающего устройства начальный адрес записи (чтения), а следовательно, все последующие и конечный адрес записи (чтения) будут изменяться, т. е. увеличиваться на единицу, каждый раз после записи (чтения) 2 слов с возвратом к сходному после записи (чтения) 2 слов. Так, например, при К-7 и запись (чтение) информационных слов в накопитель 1 осуществляется по следующим адресам: первые 2 слов -ЬоООООО +1111111, вторые -0000001 +0000000, третьи слов -0000010 +0000001, четвертые 2 слов -0000011 +0000010, пятые 2 слов -0000000 +1111111 и т. д. При этом емкосГ ь буферного запоминающего усТройства составляет 2 128 слов. Тем самым устраняется однозначное соответствие номера информационного канала и номера ячейки буферного запоминающего устройства (накопителя), куда производится запись данных этого канала. Использование предлагаемого устройства позволяет уменьшить вероятность потерь информации одних и тех же каналов, распределяя эти потери равномерно между несколькими каналами. С учетом таких особенностей изме-г рительной информации, как избыточност и периодичность, предлагаемое буферное запоминающее устройство не вносит погрешности в работу системы обработки, исключая в тоже время потери инфор мации одних и тех же каналов. Формула изобретения Буферное запоминающее устройство, содержащее накопитель, информационные входы и выходы которого являются соответственно информационными входами и выходами устройства, адресные входы накопителя подключены к выходам элементов И-ИЛИ, первые входы которых подключены к выходу элемента НЕ, вход элемента НЕ подключен к вторым входам элементов И-ИЛИ и является первым управляющим входом устройства, первый и второй счетчики адреса, входы которых являются соответственно вторым и третьим управляющими входами устройства, отличающееся тем, , что, с целью повышения надежности устройства, оно содержит первый и второй сумматоры, входы которых подключены к выходам соответствующих счетчиков адреса, выходы первого и второго сумматоров подключены соответственно к третьим и четвертым входам элементов И-ИЛИ. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР N758251, кл.С 11 С 9/00, 1978. 2.Авторское свидетельство СССР ff 51515, кл.С 11 С 9/00, 197 {прототип ).

Авторы

Даты

1982-12-15—Публикация

1981-05-22—Подача