Со 4i О

а

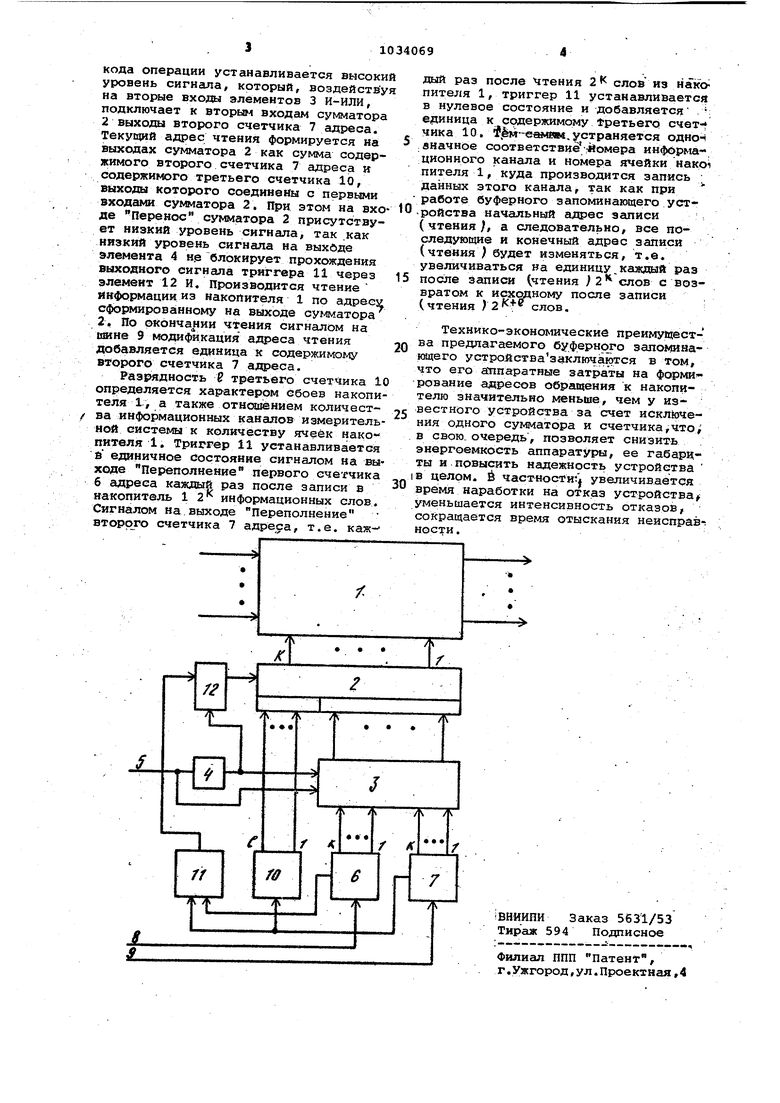

CD Изобретение относится к вычислительной технике и может быть использовано в буферных запоминающих устройствах систем ввода информации многоканальных измерительных комплек сов.« Известно буферное запоминающее устройство, в котором используется метод перекрестно-последовательного о ратания, позволяющий осуществлять двусторонний обмен информацией и сов мещать процессы ввода в буферное запоминающее устройство и вывода инфор мации из него Однако использование известного устройства в системах ввода информации многоканальных измерительных комплексов, когда последовательность опроса каналов неизменна, а их количество равно или кратно и превышает количестйо ячеек буферного.запоминаю щего устройства, отказ одной или нес кольких ячеек накопи-теля приводит к потерям информации от .одного или нес кольких каналов. Наиболее близким к предлагаемому является буферное запоминаияцее устройство, содержащее накопитель,ийформационные входы и выходы которо- . го соответственно являются информационными входами и выходами устройства, сумматор, элементы И-ИЛИ,первые входам которых подключены к выходу элемента НЕ, вход элемента НЕ соединен с вторыми входами элемен тов И-ИЛИ и является первым управ ля jo щим входом устройства, первый и второй счетчики адреса, входы которых являются соответственно вторым и тре тьим управляющими входами устройства :2. Недостатком такого устройства является низкая надежность, обусловлен ная большим количеством о.борудования схем формирования адресов обращения к накопителю. Цель изобретения - повышение надежности устройства за счет его упрощения . Поставленная цель достигается тем, что в буферное запоминанвдее уст ройство, содержащее накопитель, информационные входы и выходы которого являются соответственно информационными входами и выходами устройст ва, сумматор, элементы. И-ИЛИ, первые входы которых соединены с выходом элемента НЕ, вход элемента НЕ соедииен с вторыми входами элементов И-ИЛ и является первым управляющим входом устройства, первый и второй счетчики адреса, входы которых являются соот- ветственно вторым и третьим управляю щими входами устройства, введены .триггер, элемент И, третий счетчик адреса, вход KOTOPOJ O соединен с пер вым входом tpHrrepa и выходом Пере7 полнение второго счетиика адреса, выходы третьего счетчика адреса соединены с одними входами сумматора, другие входы которого соединены с входами элементов И-ИЛИ, третьи и четвертые входы которых соответствен но соединены с -выxoдa « первого и второго-счетчиков адреса, выход Переполнение первого счетчика адреса соединен с вторым входом триггера, выход которого соединен с первым входом элемента И, второй вход которого соединен с-выходом элемента НЕ, а выход элемента И соединен с входом Перенос сумматора, выходы которого соединены с адресными входами накопителя. На чертеже представлена структурная схема буферного запоминающего устройства. Устройство содержит накопитель 1, cyimaiop 2, элементы 3 И-ИЛИ, элемент 4 НЕ, шину 5 кода операции, первый счетчик 6 адреса, второй счетчик 7 адреса,, шину 8 модификации адреса записи, шину 9 модификации адреса чтения, третий счетчик 10 адреса, триггер 11, элемент 12 И. Устройство работает следующим образом. Перед началом --рйботы счетчики 6, 7 и 10 адреса устанавливаются, как и триггер 11, -в нулевое состояние (цепь начальной установки на чертеже не показана ). Емкость буферного зaпo инaющeгo устройства определяется разрядностью первого счетчика б адреса (второго счетчика 7 адреса) и составляет V 2 слов, где К количество разрядов первого счетчика б (второго счетчика 7 адреса). При выполнении операции записи информации в накопитель 1 на шине 5 КОД9 операции устанавливается низкий уровень сигнала, который, воздействуя через элемент 4 НЕ на первые входы элементов 3 И-ИЛИ, подключает к вторьм входам сумматора 2 выходы первого счетчика б- адреса. Текущий адрес записи формируется на выходах сумматора 2 как сумма содержимого первого счетчика 6 адреса и содержимого третьего счетчика 10, выходы которого соединейы с первыми входами сумматора 2, с учетом сигнала на входе Перенос сумматора 2. Высокий уровень сигнала на выходе элемента 4 НЕ, воздействуя на элемент 12 И подключает ко входу переноса сумматора 2 выходной сигнал триггера 11. В накопитель 1 по адресу, сформированнс 1у на выходах сугФ1атора 2, осуществляется запись информации с входных иин числа. По окончании записи сигналом на шине 8 модификация адреса записи добавляется единица к содержимому первого счетчика 6 адреса записи. При выполнении операции чтения информации из накопителя 1 на шине 5

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1983 |

|

SU1101889A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1361632A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1236550A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1361633A2 |

| Буферное запоминающее устройство | 1982 |

|

SU1105940A1 |

| Устройство для сопряжения вычислительной машины с устройством ввода изображения | 1985 |

|

SU1260967A1 |

| Буферное запоминающее устройство | 1981 |

|

SU982095A1 |

| Буферное запоминающее устройство | 1983 |

|

SU1124379A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1048516A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1297115A1 |

БУФЕРНОЕ ЗАПОМИНАЩЕЕ УСТРОПСГВО, содержащее накопитель, информационные входы и выходы которо- . го являются соответственно информационными входами и выходами устройст ва, сумматор, элементы И-ИЛИj,первые входы которых соединены с выходом элемента НЕ, вход элемента НЕ соеди- . йен с входами элементов И-ИЛК и является первым управляющим входом устройства, первый и второй счетчики адреса, входы которого являются соответственно и третьим управляющими входами устройства, отличающееся тем, что, с целью повышения надежности устройства, в него-введены триггер, элемент И, тре тий счетчик адреса, вход которого соединен с первым входом триггера и выходом Переполнение второго счетчика адреса, выходы третьего счетчика адреса соединены с одними входами сумматора, другие входы которого соединены с входами элементов.И-ИЛИ, третьи и четвертые входы которых со.ответственно соединены с выходами первого и второго счетчиков адреса, выход Переполнение первого счетчика адреса соединен с вторым входом 1 триггера, выход которого соединен с первым входом элемента И, второй вход которого соединен с выходом элемента НЕ, а выход элемента И соеС динен с входом Перенос сумматора, выходы которого соединены с адресныQ С ми входами накопителя.

Авторы

Даты

1983-08-07—Публикация

1982-03-26—Подача