Изобретение относится к вычислительной технике и может быть использовано в качестве буферного запоминающего устройства в системах сбора и регистрации измерительной информации.

Цель изобретения - повь шение надежности устройства.

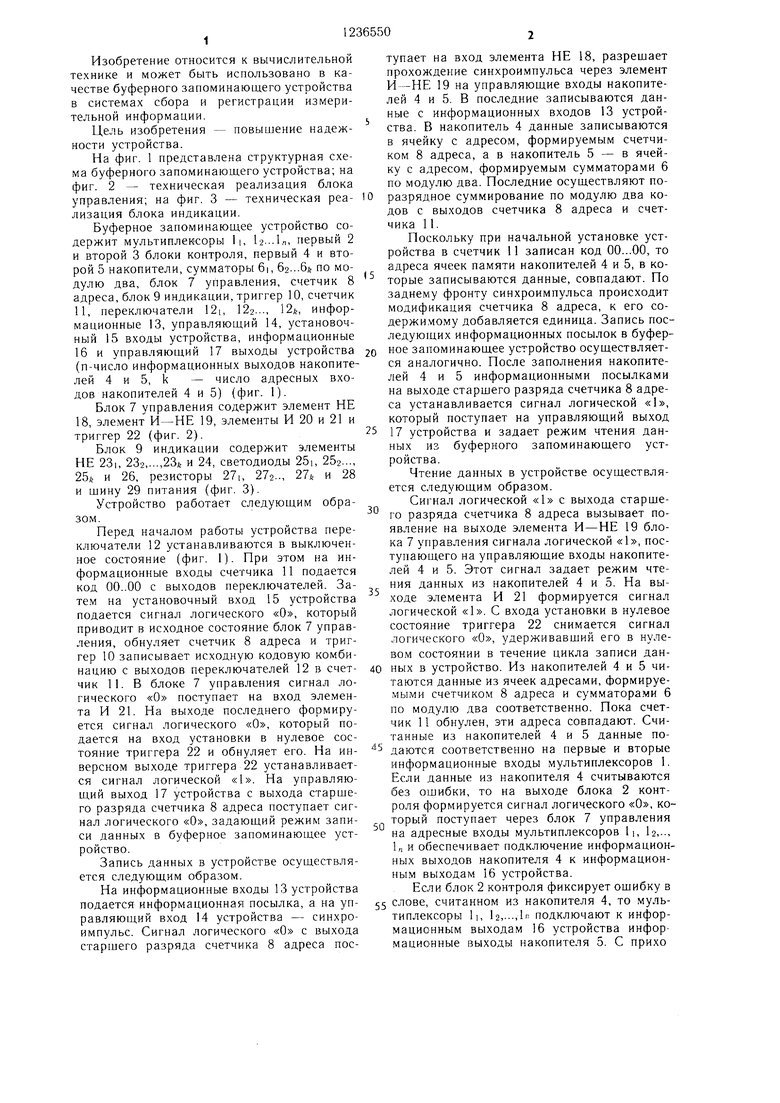

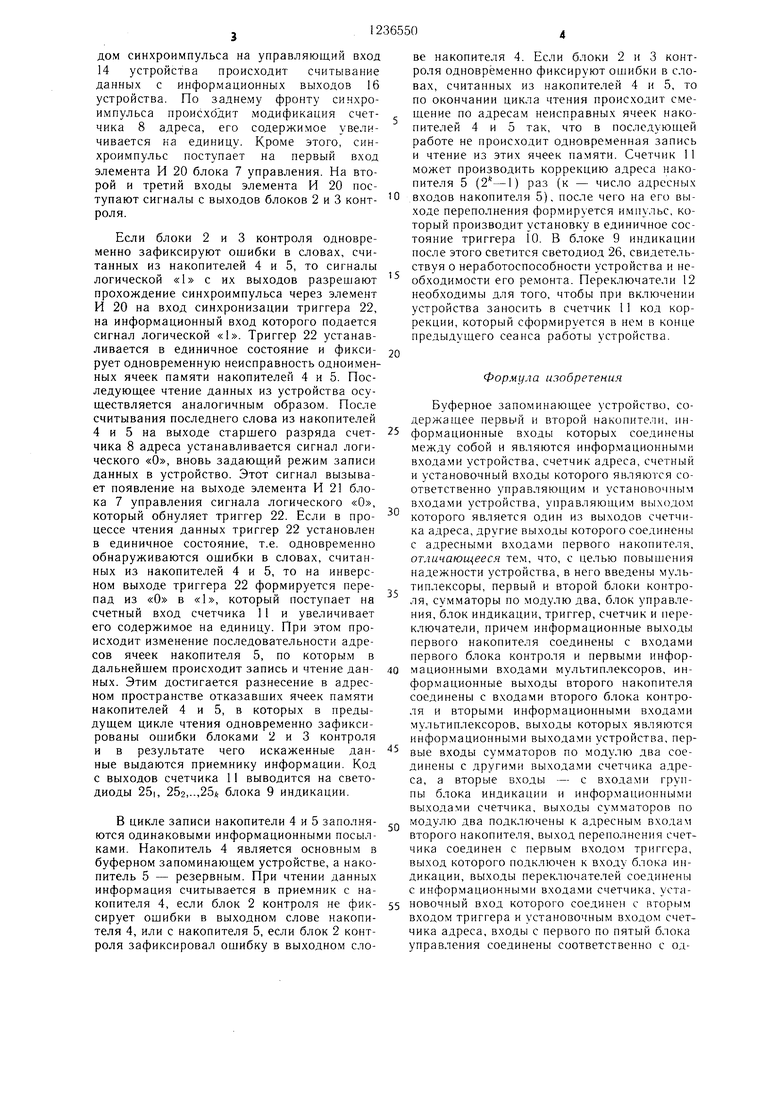

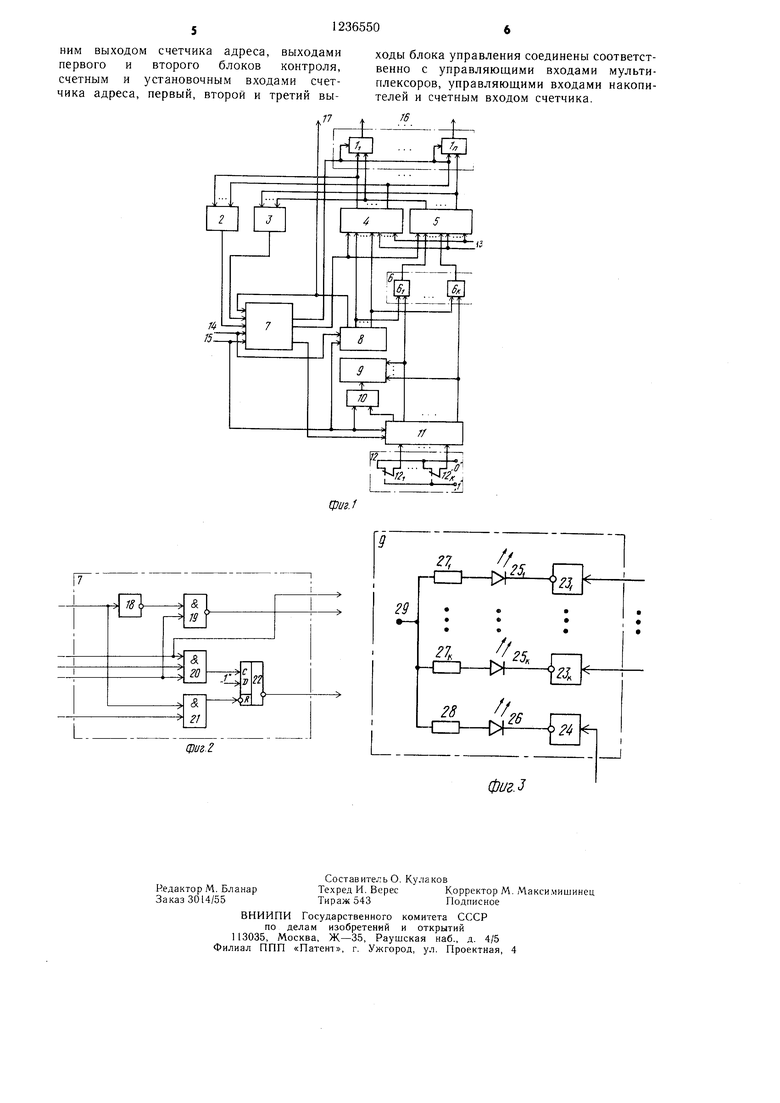

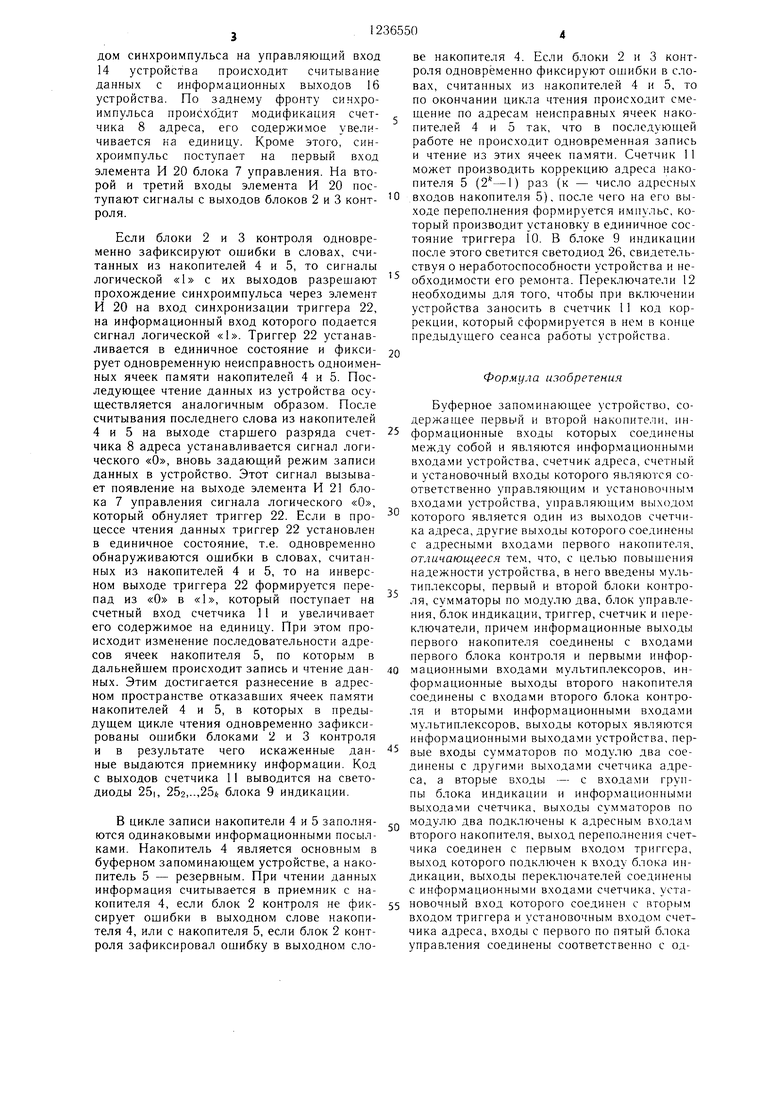

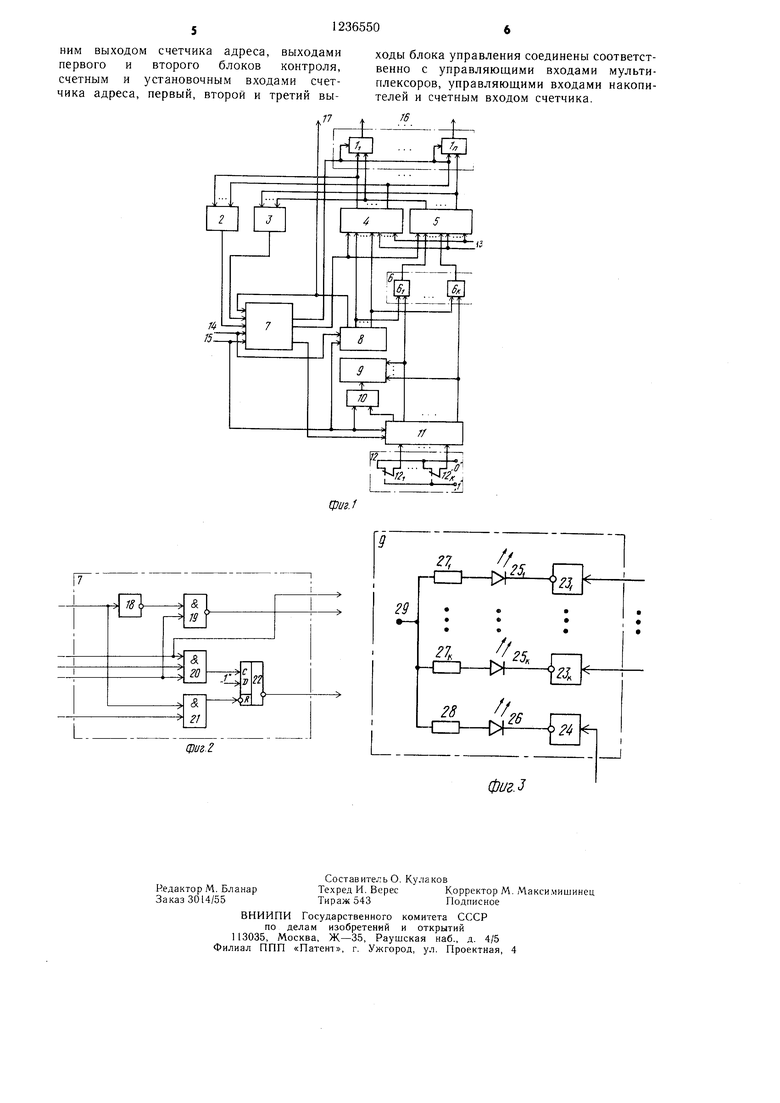

На фиг. 1 представлена структурная схема буферного запоминающего устройства; на фиг. 2 - техническая реализация блока управления; на фиг. 3 - техническая реализация блока индикации.

Буферное запоминающее устройство содержит мультиплексоры 1|, b.-.U, первый 2 и второй 3 блоки контроля, первый 4 и второй 5 накопители, сумматоры 6i, 62...64 по модулю два, блок 7 уг1равления, счетчик 8 адреса, блок 9 индикации,триггер 10, счетчик 11, переключатели 12i, 122..., 12t, информационные 13, управляющий 14, установочный 15 входы устройства, информационные

тупает на вход элемента НЕ 18, разрешает прохождение синхроимпульса через элемент И-НЕ 19 на управляющие входы накопителей 4 и 5. В последние записываются данные с информационных входов 13 устройства. В накопитель 4 данные записываются в ячейку с адресом, формируемым счетчиком 8 адреса, а в накопитель 5 - в ячейку с адресом, формируемым сумматорами 6 по модулю два. Последние осуществляют поразрядное суммирование по модулю два кодов с выходов счетчика 8 адреса и счетчика 11.

Поскольку при начальной установке устройства в счетчик 11 записан код 00...00, то адреса ячеек памяти накопителей 4 и 5, в ко- торые записываются данные, совпадают. По заднему фронту синхроимпульса происходит модификация счетчика 8 адреса, к его содержимому добавляется единица. Запись последующих информационных посылок в буфер10

16 и управляющий 17 выходы устройства 20 ное запоминающее устройство осуществляет(п-число информационных выходов накопителей 4 и 5, k - число адресных входов накопителей 4 и 5) (фиг. 1).

Блок 7 управления содержит элемент НЕ 18, элемент И-НЕ 19, элементы И 20 и 21 и триггер 22 {фиг. 2).

Блок 9 индикации содержит элементы НЕ 23, 232,...,23 и 24, светодиоды 25i, 252..., 25k и 26, резисторы 27i, 272.., 27 и 28 и шину 29 питания (фиг. 3).

Устройство работает следующим образом.

Перед началом работы устройства переключатели 12 устанавливаются в выключенное состояние (фиг. 1). При этом на информационные входы счетчика 11 подается код 00..00 с выходов переключателей. Затем на установочный вход 15 устройства подается сигнал логического «О, которь й приводит в исходное состояние блок 7 управления, обнуляет счетчик 8 адреса и триггер 10 записывает исходную кодовую комбися аналогично. После заполнения накопителей 4 и 5 информационными посылками на выходе старшего разряда счетчика 8 адреса устанавливается сигнал логической «1, который поступает на управляющий выход 25 17 устройства и задает режим чтения данных из буферного запоминающего устройства.

Чтение данных в устройстве осуществляется следующим образом.

Сигнал логической «1 с выхода старще- го разряда счетчика 8 адреса вызывает появление на выходе элемента И-НЕ 19 блока 7 управления сигнала логической «1, поступающего на управляющие входы накопителей 4 и 5. Этот сигнал задает режим чтения данных из накопителей 4 и 5. На выходе элемента И 21 формируется сигнал логической «1. С входа установки в нулевое состояние триггера 22 снимается сигнал логического «О, удерживавший его в нулевом состоянии в течение цикла записи дан30

35

нацию с выходов переключателей 12 в счет- 40 ных в устройство. Из накопителей 4 и 5 чичик II. В блоке 7 управления сигнал логического «О поступает на вход элемента И 21. На выходе последнего формируется сигнал логического «О, который подается на вход установки в нулевое состояние триггера 22 и обнуляет его. На инверсном выходе триггера 22 устанавливается сигнал логической «1. На управляющий выход 17 устройства с выхода старшего разряда счетчика 8 адреса поступает сигнал логического «О, задающий режим записи данных в буферное запоминающее устройство.

Запись данных в устройстве осуществляется следующим образом.

На информационные входы 13 устройства

45

50

таются данные из ячеек адресами, формируемыми счетчиком 8 адреса и сумматорами 6 по модулю два соответственно. Пока счетчик 11 обнулен, эти адреса совпадают. Считанные из накопителей 4 и 5 данные подаются соответственно на первые и вторые информационные входы мультиплексоров 1. Если данные из накопителя 4 считываются без ошибки, то на выходе блока 2 контроля формируется сигнал логического «О, который поступает через блок 7 управления на адресные входы мультиплексоров 1|, Ь,.., In и обеспечивает подключение информационных выходов накопителя 4 к информационным выходам 16 устройства.

Если блок 2 контроля фиксирует ошибку в

подается информационная посылка, а на уп- 55 слове, считанном из накопителя 4, то мульравляющий вход 14 устройства - синхроимпульс. Сигнал логического «О с выхода старшего разряда счетчика 8 адреса постиплексоры li, 12,...,In подключают к информационным выходам 16 устройства информационные выходы накопителя 5. С прихо

тупает на вход элемента НЕ 18, разрешает прохождение синхроимпульса через элемент И-НЕ 19 на управляющие входы накопителей 4 и 5. В последние записываются данные с информационных входов 13 устройства. В накопитель 4 данные записываются в ячейку с адресом, формируемым счетчиком 8 адреса, а в накопитель 5 - в ячейку с адресом, формируемым сумматорами 6 по модулю два. Последние осуществляют поразрядное суммирование по модулю два кодов с выходов счетчика 8 адреса и счетчика 11.

Поскольку при начальной установке устройства в счетчик 11 записан код 00...00, то адреса ячеек памяти накопителей 4 и 5, в ко- торые записываются данные, совпадают. По заднему фронту синхроимпульса происходит модификация счетчика 8 адреса, к его содержимому добавляется единица. Запись последующих информационных посылок в буфер

ное запоминающее устройство осуществляется аналогично. После заполнения накопителей 4 и 5 информационными посылками на выходе старшего разряда счетчика 8 адреса устанавливается сигнал логической «1, который поступает на управляющий выход 17 устройства и задает режим чтения данных из буферного запоминающего устройства.

Чтение данных в устройстве осуществляется следующим образом.

Сигнал логической «1 с выхода старще- го разряда счетчика 8 адреса вызывает появление на выходе элемента И-НЕ 19 блока 7 управления сигнала логической «1, поступающего на управляющие входы накопителей 4 и 5. Этот сигнал задает режим чтения данных из накопителей 4 и 5. На выходе элемента И 21 формируется сигнал логической «1. С входа установки в нулевое состояние триггера 22 снимается сигнал логического «О, удерживавший его в нулевом состоянии в течение цикла записи дан

5

0

таются данные из ячеек адресами, формируемыми счетчиком 8 адреса и сумматорами 6 по модулю два соответственно. Пока счетчик 11 обнулен, эти адреса совпадают. Считанные из накопителей 4 и 5 данные подаются соответственно на первые и вторые информационные входы мультиплексоров 1. Если данные из накопителя 4 считываются без ошибки, то на выходе блока 2 контроля формируется сигнал логического «О, который поступает через блок 7 управления на адресные входы мультиплексоров 1|, Ь,.., In и обеспечивает подключение информационных выходов накопителя 4 к информационным выходам 16 устройства.

Если блок 2 контроля фиксирует ошибку в

слове, считанном из накопителя 4, то мультиплексоры li, 12,...,In подключают к информационным выходам 16 устройства информационные выходы накопителя 5. С прихо

дом синхроимпульса на управляющий вход 14 устройства происходит считывание данных с информационных выходов 16 устройства. По задне.му фронту синхроимпульса происходит модификация счетчика 8 адреса, его содержимое увеличивается на единицу. Кроме этого, синхроимпульс поступает на первый вход элемента И 20 блока 7 управления. На второй и третий входы элемента И 20 поступают сигналы с выходов блоков 2 и 3 конт- роля.

Если блоки 2 и 3 контроля одновременно зафиксируют ошибки в словах, считанных из накопителей 4 и 5, то сигналы логической «1 с нх выходов разрешают прохождение синхроимпульса через элемент И 20 на вход синхронизации триггера 22, на информационный вход которого подается сигнал логической «1. Триггер 22 устанавливается в единичное состояние и фикси- рует одновременную неисправность одноименных ячеек памяти накопителей 4 и 5. Последующее чтение данных из устройства осуществляется аналогичным образом. После считывания последнего слова из накопителей 4 и 5 на выходе старшего разряда счет- чика 8 адреса устанавливается сигнал логического «О, вновь задающий режим записи данных в устройство. Этот сигнал вызывает появление на выходе элемента И 21 блока 7 управления сигнала логического «О, который обнуляет триггер 22. Если в про- цессе чтения данных триггер 22 установлен в единичное состояние, т.е. одновременно обнаруживаются ошибки в словах, считанных из накопителей 4 и 5, то на инверсном выходе триггера 22 формируется перепад из «О в «1, который поступает на счетный вход счетчика 11 и увеличивает его содержимое на единицу. При этом происходит изменение последовательности адресов ячеек накопителя 5, по которым в дальнейшем происходит запись и чтение дан- ных. Этим достигается разнесение в адресном пространстве отказавших ячеек памяти накопителей 4 и 5, в которых в предыдущем цикле чтения одновременно зафиксированы ошибки блоками 2 и 3 контроля и в результате чего искаженные дан- ные выдаются приемнику информации. Код с выходов счетчика 11 выводится на свето- диоды 25|, 252,..,25«, блока 9 индикации.

В цикле записи накопители 4 и 5 заполня

ются одинаковыми информационными посылками. Накопитель 4 является основным в буферном запоминающем устройстве, а накопитель 5 - резервным. При чтении данных информация считывается в приемник с накопителя 4, если блок 2 контроля не фик- сирует ошибки в выходном слове накопителя 4, или с накопителя 5, если блок 2 контроля зафиксировал ошибку в выходно.м слове накопителя 4. Если блоки 2 и 3 контроля одновременно фиксируют ошибки в словах, считанных из накопителей 4 и 5, то по окончании цикла чтения происходит смещение по адресам неисправных ячеек накопителей 4 и 5 так, что в последующей работе не происходит одновременная запись и чтение из этих ячеек памяти. Счетчик 11 может производить коррекцию адреса накопителя 5 () раз (к - число адресных входов накопителя 5), после чего на его выходе переполнения формируется импульс, который производит установку в единичное состояние триггера 10. В блоке 9 индикации после этого светится светодиод 26, свидетельствуя о неработоспособности устройства и необходимости его ремонта. Переключатели 12 необходимы для того, чтобы при включении устройства заносить в счетчик 11 код коррекции, который сформируется в нем в конце предыдущего сеанса работы устройства.

0 5 0 5

5

0

5

Формула изобретения

Буферное запоминающее устройство, содержащее первый и второй накопители, информационные входы которых соединены .между собой и являются информационными входами устройства,счетчик адреса,счетный и установочный входы которого являются соответственно управляющим и установочным входами устройства, управляющим выходом которого является один из выходов счетчика адреса, другие выходы которого соединены с адресными входами первого накопителя, отличающееся тем, что, с целью повышения надежности устройства, в него введены мультиплексоры, первый и второй блоки контроля, сумматоры по модулю два, блок управления, блок индикации, триггер, счетчик и переключатели, причем информационные выходы первого накопителя соединены с входами первого блока контроля и первыми информационными входами мультиплексоров, информационные выходы второго накопителя соединены с входами второго блока контроля и вторыми информационными входами мультиплексоров, выходы которых являются информационными выходами устройства, первые входы су.мматоров по модулю два соединены с други.ми выхода.ми счетчика адреса, а вторые входы - с входами группы блока индикации и информационными выходами счетчика, выходы сумматоров по модулю два подключены к адресным входам второго накопителя, выход переполнения счетчика соединен с первым входом триггера, выход которого подключен к входу блока индикации, выходы переключателей соединены с информационными входа.ми счетчика, установочный вход которого соединен с вторым входом триггера и установочным входом счетчика адреса, входы с первого по пятый блока управления соединены соответственно с одj12365506

ним выходом счетчика адреса, выходамиходы блока управления соединены соответстпервого и второго блоков контроля,венно с управляющими входами мультисчетным и установочным входами счет-плексоров, управляющими входами накопи- чика адреса, первый, второй и третий выталей и счетным входом счетчика.

77

Составитель О. Кулаков

Техред И. ВересКорректор М. Макси.мишинец

Тираж 543Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП «Патен, г. Ужгород, ул. Проектная, 4

плексоров, управляющими входами

талей и счетным входом счетчика.

J6

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1986 |

|

SU1361632A1 |

| Устройство для задания тестовых воздействий | 1988 |

|

SU1541614A1 |

| Запоминающее устройство с тестовым самоконтролем | 1986 |

|

SU1396160A1 |

| Устройство для имитации информационных каналов | 1986 |

|

SU1386996A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1297115A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1312646A1 |

| Буферное запоминающее устройство | 1983 |

|

SU1120407A1 |

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1278981A1 |

| Буферное запоминающее устройство | 1983 |

|

SU1119077A1 |

Изобретение относится к вычислительной технике и может быть использовано в качестве буферного запоминающего устройства в системах сбора и регистрации измерительной информации. Целью изобретения является повышение надежности устройства. Устройство содержит мультиплексоры, блоки контроля, накопители, сумматоры по модулю два, блок управления, счетчик адреса, блок индикации, триггер, счетчик,переключа- тели. В случае если блоки контроля одновременно фиксируют ошибки в словах, считанных из обоих накопителей, по окончании цикла чтения происходит смещение по адресам неисправных ячеек накопителей так, что в посдедующей работе не будет происходить одновременная запись и чтение из этих ячеек памяти. 3 ил. 1чЭ ее О5 сл сл

| Устройство для управления блокомпАМяТи | 1978 |

|

SU809345A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Буферное запоминающее устройство | 1983 |

|

SU1120407A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-06-07—Публикация

1984-12-30—Подача