00 СА9

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1985 |

|

SU1280457A1 |

| Устройство для сопряжения вычислительной машины с устройством ввода изображения | 1985 |

|

SU1260967A1 |

| Буферное запоминающее устройство | 1983 |

|

SU1124379A1 |

| Буферное запоминающее устройство | 1988 |

|

SU1571679A1 |

| Устройство для сопряжения цифровой вычислительной машины с устройством ввода изображений | 1983 |

|

SU1176339A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1297115A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1363308A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1361632A1 |

| Буферное запоминающее устройство | 1990 |

|

SU1783581A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439618A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении си стем отобра- , ження информации в матричном виде с построчным сканированием, совмещающих ввод данных .с переиндексациен каждого сообщения. Устройство содержит блок 1 памяти, блок 2 коррекции координат., счетчики адресов записи 3 и чтения 4, регистры 5, 6 поправок и к координатам, мультиплексоры 7, 8, 11, 12, сумматоры 9, 10, блок 13 уп- р авления. В устройстве осуществляется преобразование поворота координат, что позволяет снять э,ти преобразования с подсистемы обработки при незначительных дополнительных затратах. 1 З.П. ф-лы, 4 ил.

№1 liUll:

дмишДШ

40 W «мм 45 IS

Фnt

№1 liUll:

мишДШ

40 W «мм 45 IS

Изобретение относится к вычислительной технике и может быть исполь- овано при построении систем отобра- |кения информагдии в матричном виде с юстрочным сканированием, совмещающих звод данных с переиндексацией каждого :ообщения.

Цель изобретения - расширение I )ункционапьных возможностей устройст:за за счет осуществле ния поворота координат изображения.

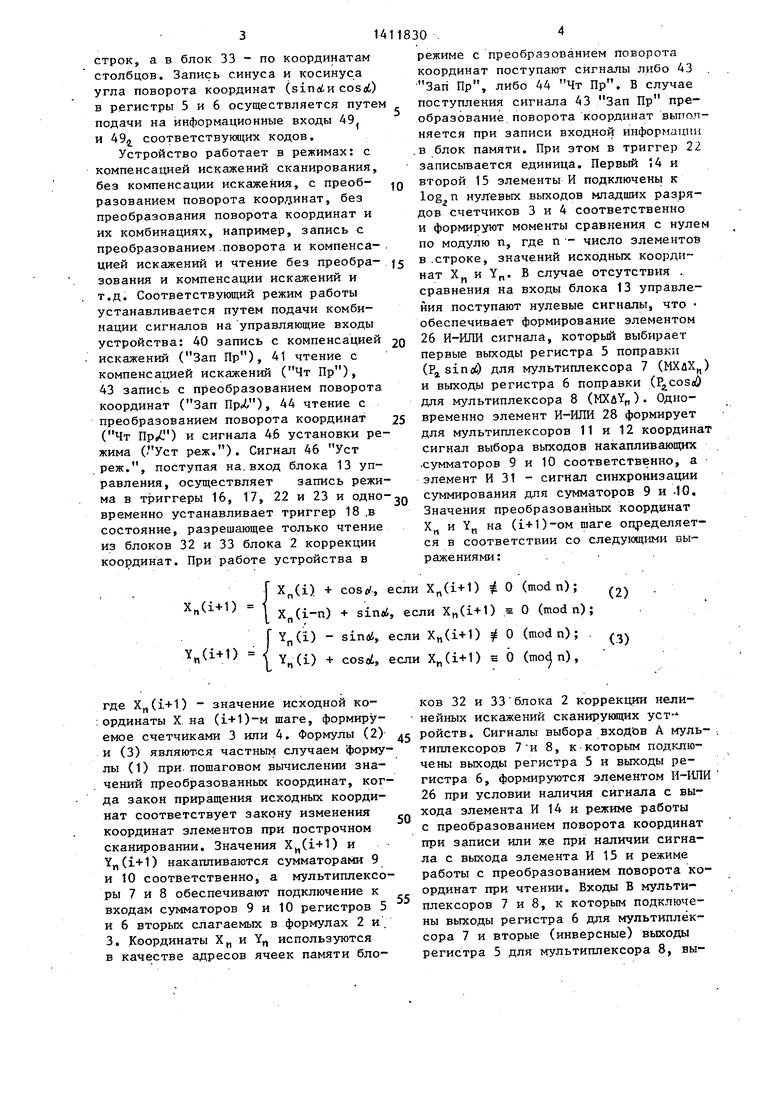

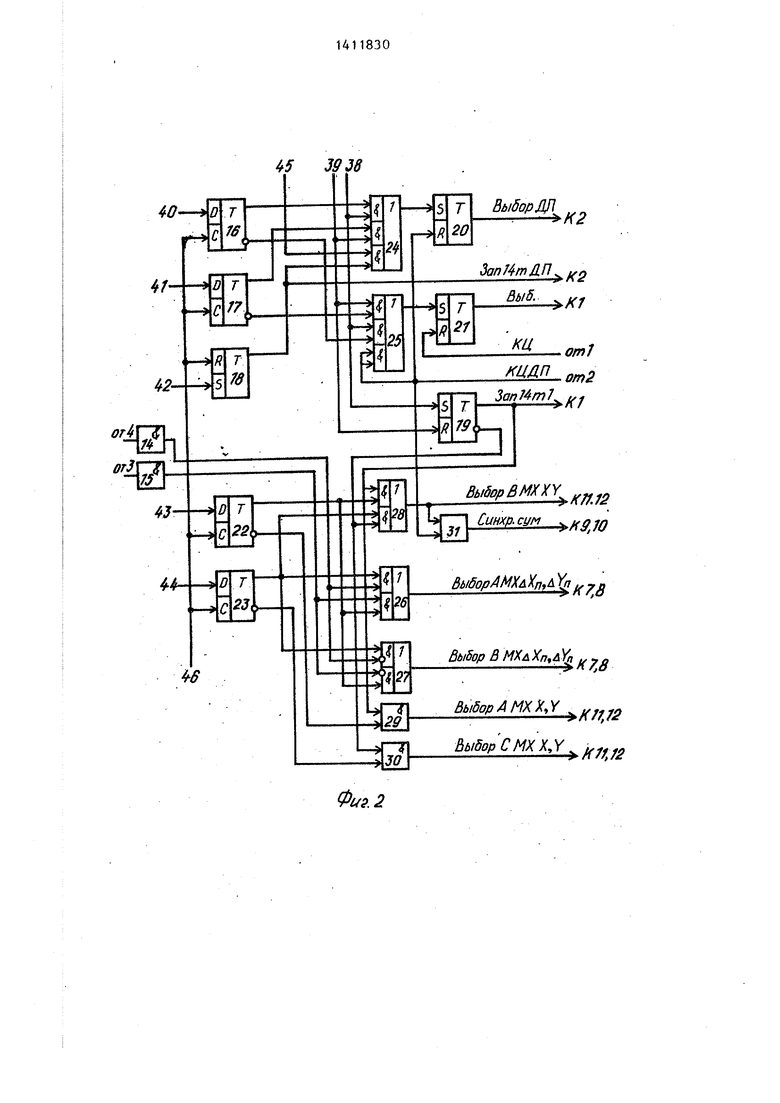

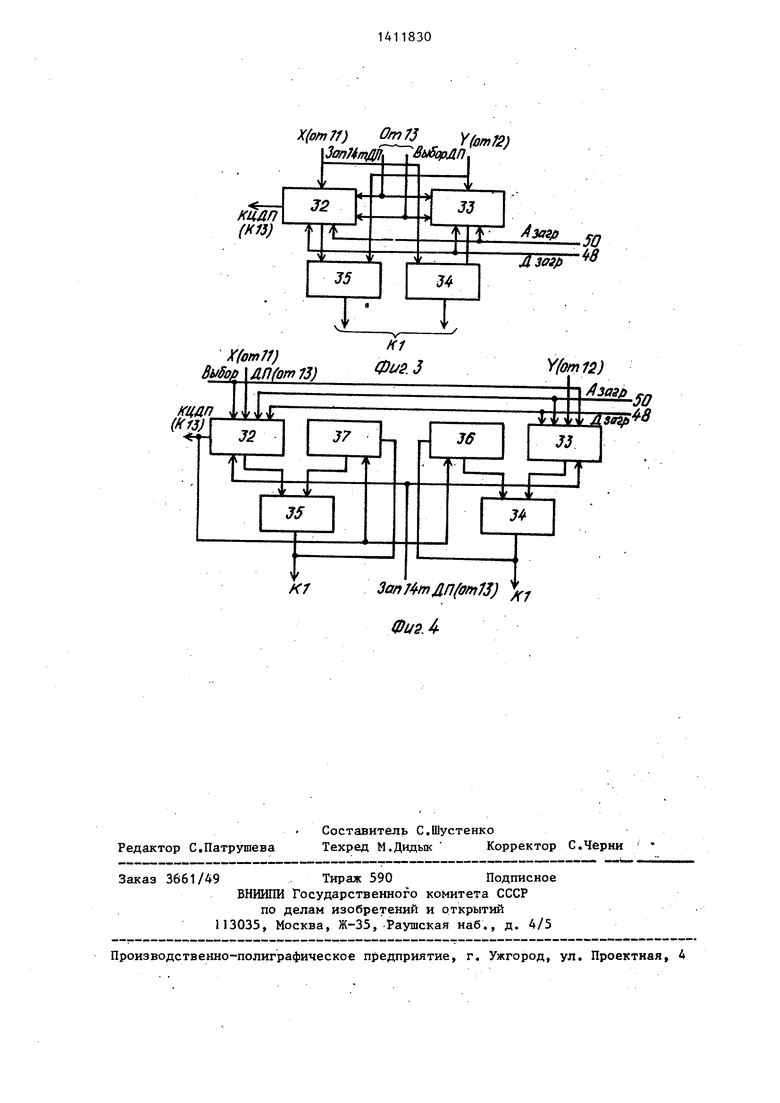

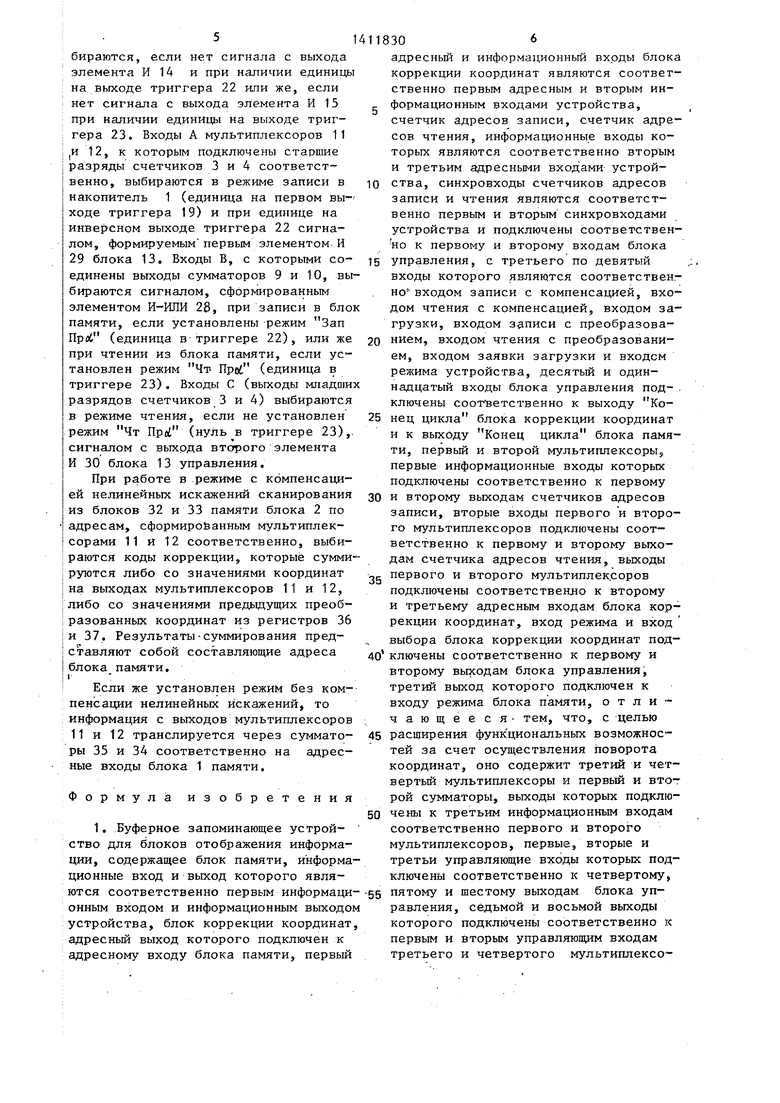

На фиг,1 показана структурная схе- ма устройства; на фиг.2 - функциональная схема блока управления; на ()иг,3 и 4 - варианты реализации блока 1соррекции координат.

Буферное запоминающее устройство |;одержит блок 1 памяти, блок 2 кор- )екции координат, счетчики адресов иаписи 3 и чтения 4, регистры 5 и 6 поправок к координатам ( ei и cos if), мультиплексор 7 (поправки к координате Х„ (МХлХ„)), мультиплексор (поправки к координате У„ (МХдУ„)), ;умматор 9 (преобразованной координа- ы .Х„ ( ) ) , сумматор 10 (преобразованной координаты, У„ ( )), мультиплексор 1Т (координаты столбца МХ)), мультиплексор 12 (координаты строки (МХУ)) и блок 13 управления.

Блок 13 управления содержит эле- i менты И 14 и 15, триггеры 16...23, :1лементы И-РШИ 24...28 и элементы И 29..,31.

Первый вариант блока 2 коррекции 1:оординат содержит дополнительные (|локи 32 и 33 памяти, сумматор 34 (Координаты X), сумматор 35 (координаты у). Второй вариант блока 2 кор- Х екции координат дополнительно содер- 3iJMT .регистр 36 (координаты X) и ре- jl-HCTP 37 (координаты У).

На обозначены вход 38 за- (заявка ЗАЛ), вход 39 чтения (заявка ЧТ), вход 40 записи с компен- 4ацией, вход 41 чтения с компенсаци- 4й, вход 42 загрузки, вход 43 записи ci преобразованием, вход 44 чтения с г реобразованием, вход 45 заявки за- rfpysKH, вход 46 режима, информацион- fibie входы 47...49, адресные входы 50 к( информационные выходы 51.

Первый регистр поправки к исход- tjbiM координатам предназначен для хра- к|ения двоичного кода синуса угла по- EJopoTa координат (sinai), второй ре- г|истр поправки - для хранения двоич- кода косинуса угла поворота координат (созоб). Мультиплексоры поправок служат для под1шючения того или иного регистра поправок к входам на- капливакж1их сумматоров преобразованных координат (Xj, У ) . Суть изобретения заключается в том, что в выражении для вычисления преобразованных координат

Х Х„-со8й6+ Y -sinoi ;

,У„ -Х„-81Пс6+ У„-созо6, (1) где Х, Y - исходные координаты текущего элемента матрицы, образованные соответствуюпщми счетчиками адреса, при построчном сканировании элементов матрищ.1 вторые слагаемые постоянны для всех элементов одной стро ки, и только при переходе со строки на строку увеличиваются при единичном приращении координаты Y на величины sin ei для Xj, и cos оЬ для Y,, а первые слагаемые постоянны для всех элементов одного столбца и увеличиваются на величину cos oi для Х„ и sinci для Y при единичном приращении координаты.Х. Это позволяет заменить операции умножения для вычисления значений Х„ и Y по формуле (1) на рекурентное сложение поправок cosci и sinoi.,

Перед началом работы производится загрузка устройства, режим загрузки устанавливается подачей сигнала на вход 42 Загр.. В результате этого с выхода триггера 18 в блок 2 коррекции координат поступает сигнал, уста навливающий режим записи для допол- нительных блоков 32 и 33 памяти. Загружаемая информация по информационным входам 48 вместе с адресом, .поступающим по адресным входам 50, попадает в блок 2 коррекции координат. Одновременно на вход 45 блока 13 управления поступает синхросигнал сопровождения загружаемых данных Заявка загр, который через элемент 24 И-ИЛИ установит триггер 20 в состояние, разрешающее выбор блоков 32 и 33 памяти. Тем самым обеспечивается запись данных с входа 48 в ячейку блоков 32 и 33 памяти, адрес которой определяется кодом на входе 50. В конце цикла обращения сигналом КЦЦП поступающим на вход блока 13 управления, триггер 20 возвращается в исходное состояние, В дополнительный блок 32 памяти загружаются данные, позволяющие компенсировать искажения сканирующих устройств по координатам

Xj(i) + cosof, если Х„(1+1) 4 О(mod п) ; /„ч

X(i-n) + sinei, если Х„(1+1) sО (mod п);

Y(i) - sinoi, если Х„(1+1) О(mod п) ; /,j4

Y(i) + cosoi, если X(i+1) s О(mod п),

где X(i+1) - значение исходной ко- ; ординаты X на (1+1)-м щаге, формируемое счетчиками 3 или 4. Формулы (2) и (3) являются частным случаем формулы (1) при пошаговом вычислении значений преобразованных координат, когда закон приращения исходных координат соответствует закону изменения координат элементов при построчном сканировании. Значения Х,(1+1) и „(14-1) накапливаются сумматорами 9 и 10 соответственно, а мультиплексоры 7 и 8 обеспечивают подключение к входам сумматоров 9 и 10 регистров 5 и 6 вторых слагаемых в формулах 2 и; 3. Координаты Х, и У„ используются в качестве адресов ячеек памяти бло

ков 32 и 33 блока 2 коррекции нели- нейных искажений сканирующих уст- ройств. Сигналы выбора входов А типлексоров 7 и 8, к-которым под1слю- чены выходы регистра 5 и выходы регистра 6, формируются элементом И-1ШИ 26 при условии наличия сигнала с выхода элемента И 14 и режиме работы с преобразованием поворота координат при записи или же при наличии сигнала с выхода элемента И 15 и режиме работы с преобразованием поворота координат при чтении. Входы В мультиплексоров 7 и 8, к KOTopbiM подключены выходы регистра 6 для мультиплексора 7 и вторые (инверсные) выходы регистра 5 для мультиплексора 8, вы

бираются, если нет сигнала с выхода элемента И 14 и при наличии единицы на вьгходе триггера 22 или же, если нет сигнала с выхода элемента И 15 при наличии единицы на выходе триггера 23. Входы А мультиплексоров 11 ,и 12, к которым подключены старшие разряды счетчиков 3 и 4 соответст- веннр, выбираются в режиме записи в Накопитель 1 (единица на первом выходе триггера 19) и при единице на инверсном выходе триггера 22 сигналом, формируемым первым элементом И 29 блока 13, Входы В, с которыми соединены выходы сумматоров 9 и 10, выбираются сигналом, сформированным элементом И-ИЛИ 28, при записи в блок

памяти, если установлены режим Зап

Проб (единица в триггере 22), или же при чтении из блока памяти, если установлен режим Чт Проб (единица в триггере 23). Входы С (выходы младших разрядов счетчиков 3 и 4) выбираются в режиме чтения, если не установлен режим Чт UptL (нуль в триггере 23),. сигналом с выхода второго элемента И 30 блока 13 управления.

При работе в .режиме с компенсацией нелинейных искажений сканирования из блоков 32 и 33 памяти блока 2 по адресам, сформированным мультиплексорами 11 и 12 соответственно, выбиаются коды коррекции, которые сумми руются либо со значениями координат на выходах мультиплексоров 11 и 12, ибо со значениями предьщущих преобазованных координат из регистров 36 и 37, Результаты-суммирования представляют собой составляющие адреса

блока памяти,

Если же установ.лен режим без компенсации нелинейных искажений, то информация с выходов мультиплексоров 11 и 12 транслируется через сумматоры 35 и 34 соответственно на адресные входы блока 1 памяти.

Формула изобретения

1, Буферное запоминающее устрой- ство для блоков отображения информации, содержащее блок памяти, информационные вход и выход которого являются соответственно первым информационным входом и информационным выходом устройства, блок коррекции координат, адресньй выход которого подключен к адресному входу блока памяти, первый

0

5

адресный и информационный входы блока коррекции координат являются соответственно первым адресным и вторым ин- формационным входами устройства,

счетчик адресов записи, счетчик адресов чтения, информационные входы которых являются соответственно вторым и третьим адресными входами устрой0 ства, синхровходы счетчиков адресов записи и чтения являются соответственно первым и вторым синхровходами устройства и подключены соответствен- но к первому и второму входам блока

5 управления, с третьего по девятый

входы которого являются соответственно входом записи с компенсацией, входом чтения с компенсацией, входом загрузки, входом записи с преобразова0 нием, входом чтения с преобразованием, входом заявки загрузки и входом режима устройства, десятый и одиннадцатый входы блока управления под- . ключены соот ветственно к выходу Ко5 нец цикла блока коррекции координат и к выходу Конец цикла блока памяти, первый и второй мультиш1ексоры5 первые информационные входы которых подключены соответственно к первому и второму выходам счетчиков адресов записи, вторые входы первого и второго мультиплексоров подключены соответственно к первому и второму выходам счетчика адресов чтения, выходы первого и второго мультиплексоров подключены соответственяо к второму и третьему адресным входам блока коррекции координат, вход режима и вход выбора блока коррекции координат под0 ключены соответственно к первому и второму выходам блока управления, третий выход которого подключен к входу режима блока памяти, отличающееся- тем, что, с целью

5 расширения функциональных возможностей за счет осуществления поворота координат, оно содержит третий и чет- вер тьй мультиплексоры и первый и вто-г рой сумматоры, выходы которых подклю0 чены к третьим информационным входам соответственно первого и второго мультиплексоров, первые, вторые и третьи управляющие входы которых подключены соответственно к четвертому, пятому и шестому выходам блока управления, седьмой и восьмой выходы которого подключены соответственно к первым и вторым управляющим входам третьего и четвертого мультиплексо5

ров, входы которых являются информационными входами группы устройства, выходы третьего и четвертого мультиплексоров подключены к входам соот- ветственно первого и второго сумматоров, управляющие входы которых под Ю1ючены к девятому выходу блока управления, двенадцатый и тринадцатый входы которого подключены к третьим выходам соответственно счетчика адресов записи и счетчика адресов чтения.

, Устройство поп,1,отличаю щ е е с я тем, что блок управления js входу установки пятого триггера, высодержит с первого по-восьмой триггеры, с первого по пятый элементы И-ШТИ и с первого по пятый элементы И, выходы первого, второго и третьего элементов И являются соответственно четвертым, шестым и девятым выходами блока управления, информационные входы первого, второго, седьмого и восьмого триггеров являются соответственно третьим, четвертым, шестым и седьмым входами блока управления, вход установки третьего триггера и вход сброса шестого триггера являются соответственно, пятым и одиннадцатым входами блока управления, тактовые входы первого, второго, седьмого и восьмого триггеров объединены и являются девятым входом блока управления, вход установки четвертого триггера подключен к первым входам первого и второго элементов И-ИЛИ и является первым входом блока управления, вход сброса четвертого триггера подключен к вторым входам первого и второго элементов И-ШШ и является вторым входом блока управления, прямой выход четвертого триггера является третьим выходом блока управления и подключен к первым входам пятого элемента ИИЛИ и первого элемента И, второй вход третьего триггера является перкоторого подключен к инверсному выхо- вым выходом блока управления и подду восьмого триггера, прямой выходключен к пятому входу первого элеменкоторого подключен к первым входамта И-ИЛИ, шестой вход которого являтретьего и четвертого элемента И-ИЛИется восьмым входом блока управления.

и к второму входу пятого элемента И-ИЛИ, выход которого является пятым выходом блока управления и подключен к первому входу третьего элемента И, второй вход которого является десятьм входом блока управления и подключен к входу сброса пятого триггера и к третьему входу второго элемента И- ИЛИ, четвертый вход которого подключен к инверсному выходу первого триггера, прямой выход которого подключен к третьему входу первого элемента И-ИЛИ, выход которого подключен к

ход которого является вторым выходом блока управления, инверсный выход четвертого триггера подключен к трет тьему входу пятого элемента И-ИЛИ и

к nepBONry входу второго элемента И, второй вход которого подключен к инверсному выходу восьмого триггера, прямой выход седьмого триггера подключен к вторым входам третьего и

четвертого элементов И-ШТИ и к четвертому входу пятого элемента И-ИШ1, инверсный выход седьмого триггера подключен к второму входу первого элемента И, третьи и четвертые входы

третьего и четвертого элементов И-ШТИ подключены к выходам соответственно четвертого и пятого элементов И, входы которых являются соответственно двенадцатым и тринадцатым входами

блока управления, выходы третьего и четвертого элементов И-ИЛИ являются соответственно седьмым и восьмым вы- ходами блока управления, прямой и инверсный выходы второго триггера подключены соответственно к четвертому входу первого элемента И-ИЛИ и к-пятому входу второго элемента И-ИЛИ, выход которого подключен к входу ус- тановки шестого триггера, прямой. 3928

Фи.2

X() ОтТЗ У(от72)

КЦДП (HIS)

50 &

| Буферное запоминающее устройство | 1983 |

|

SU1119077A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Буферное запоминающее устройство | 1983 |

|

SU1124379A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| f | |||

Авторы

Даты

1988-07-23—Публикация

1986-07-31—Подача