Изобретение относится к вычислительной технике и используется в системах для хранения и обработки двоичных кодов.

Цель изобретения - повышение быст- родействия системы.

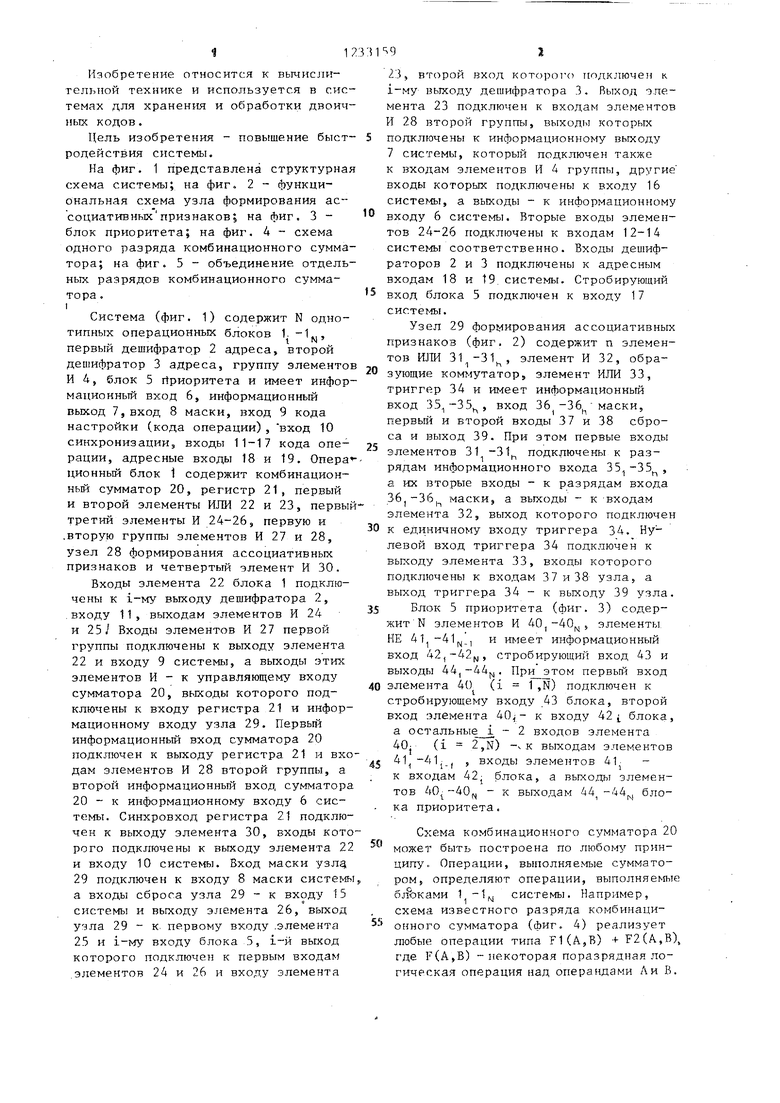

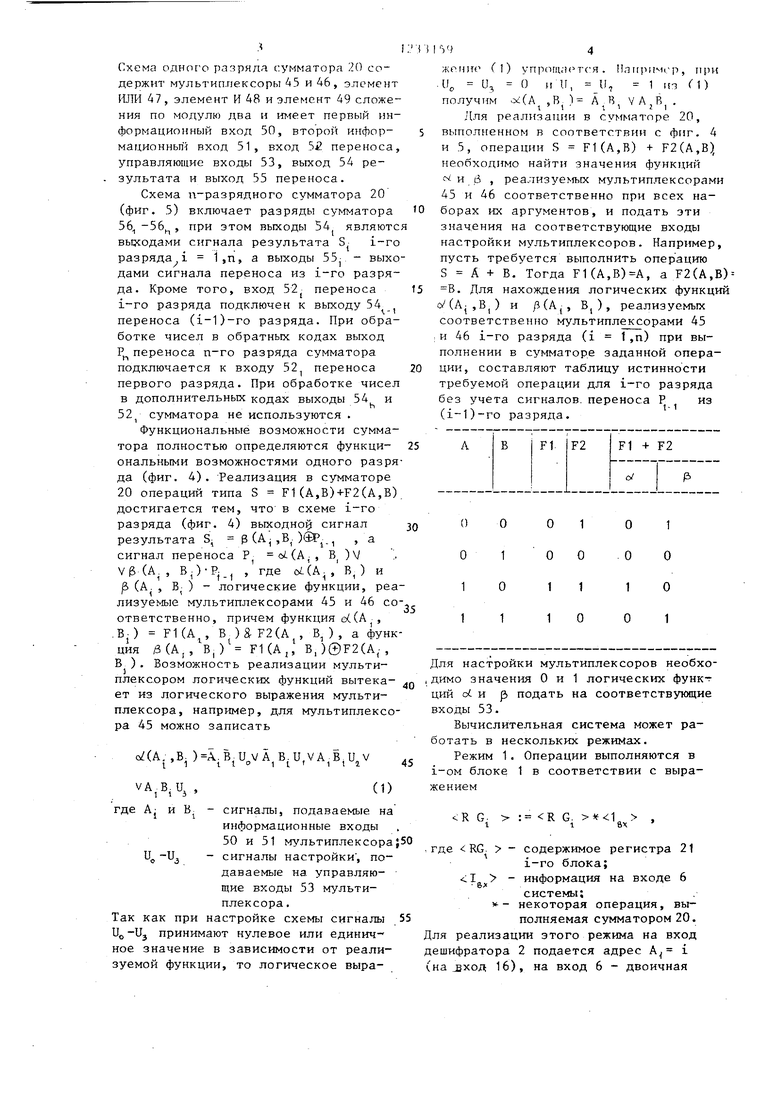

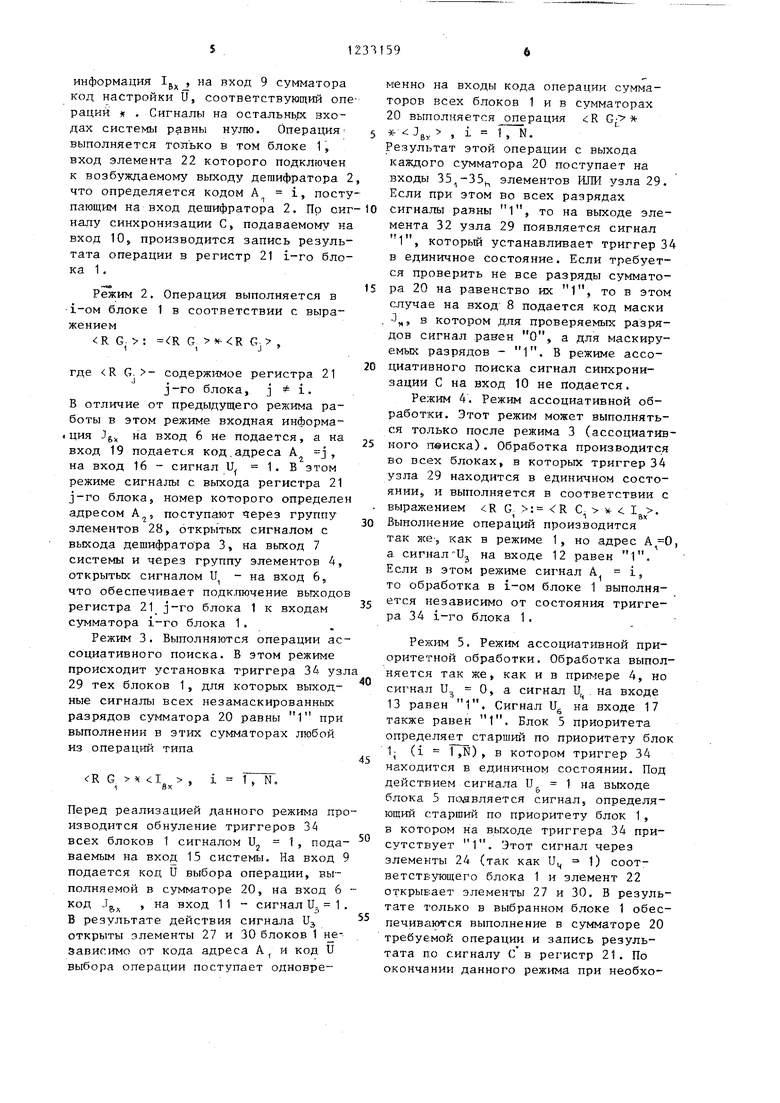

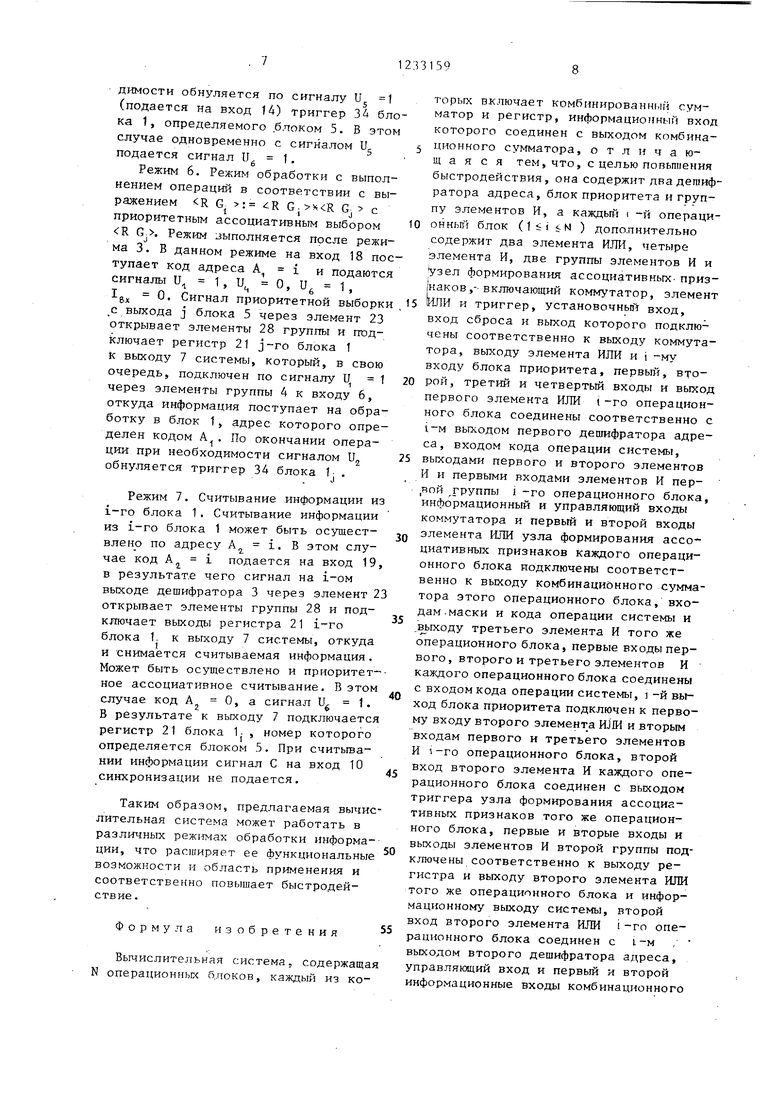

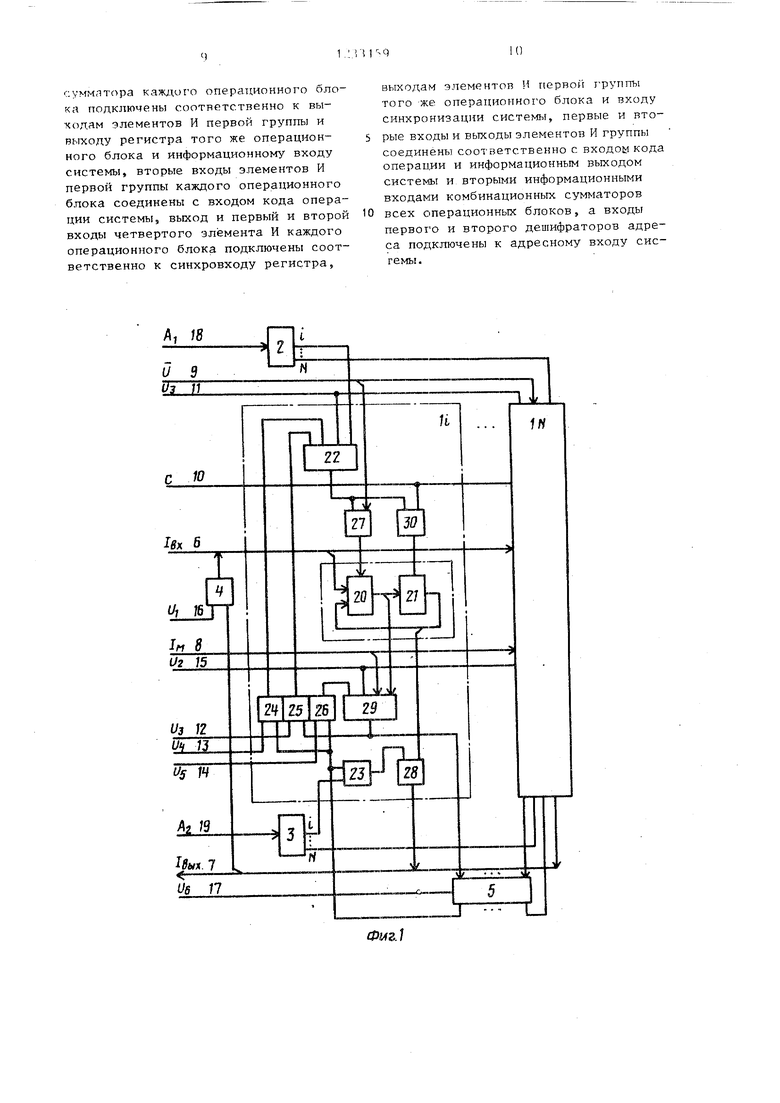

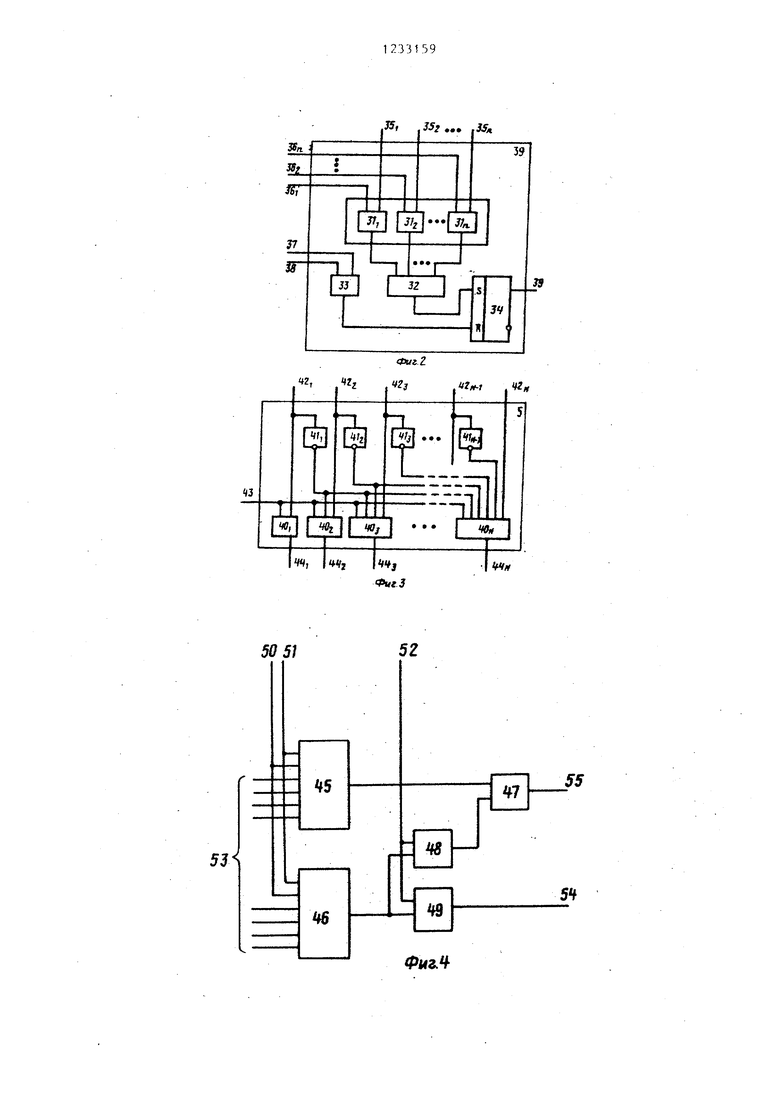

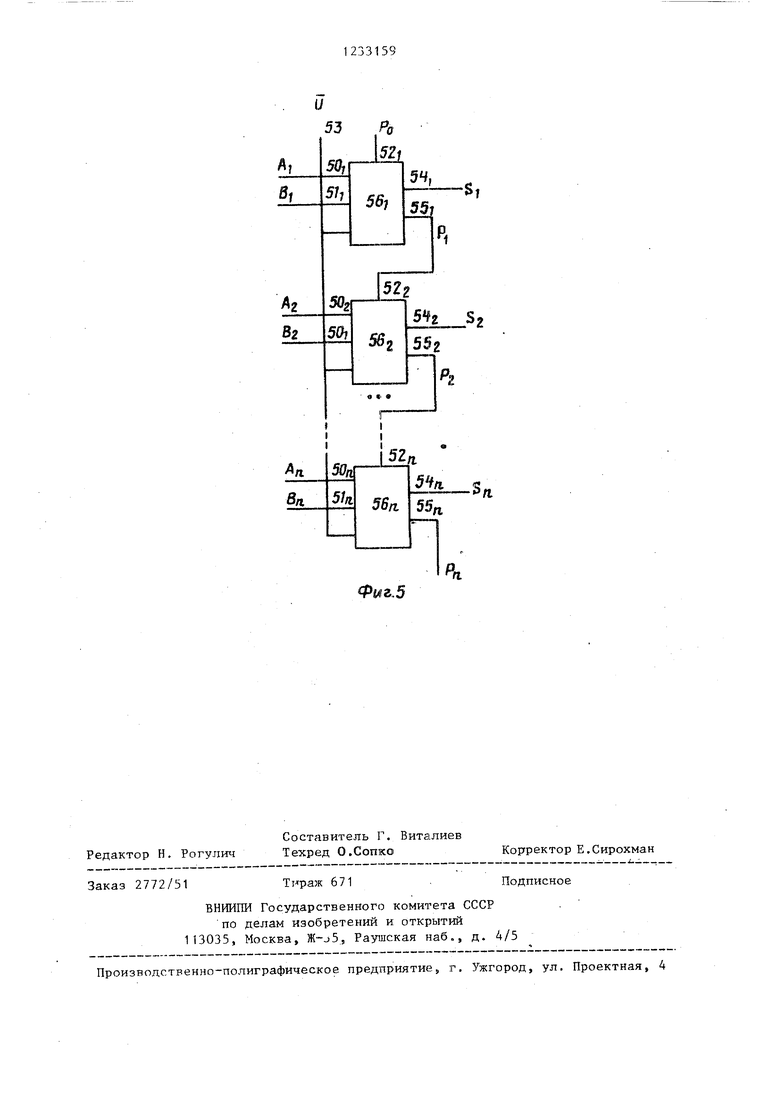

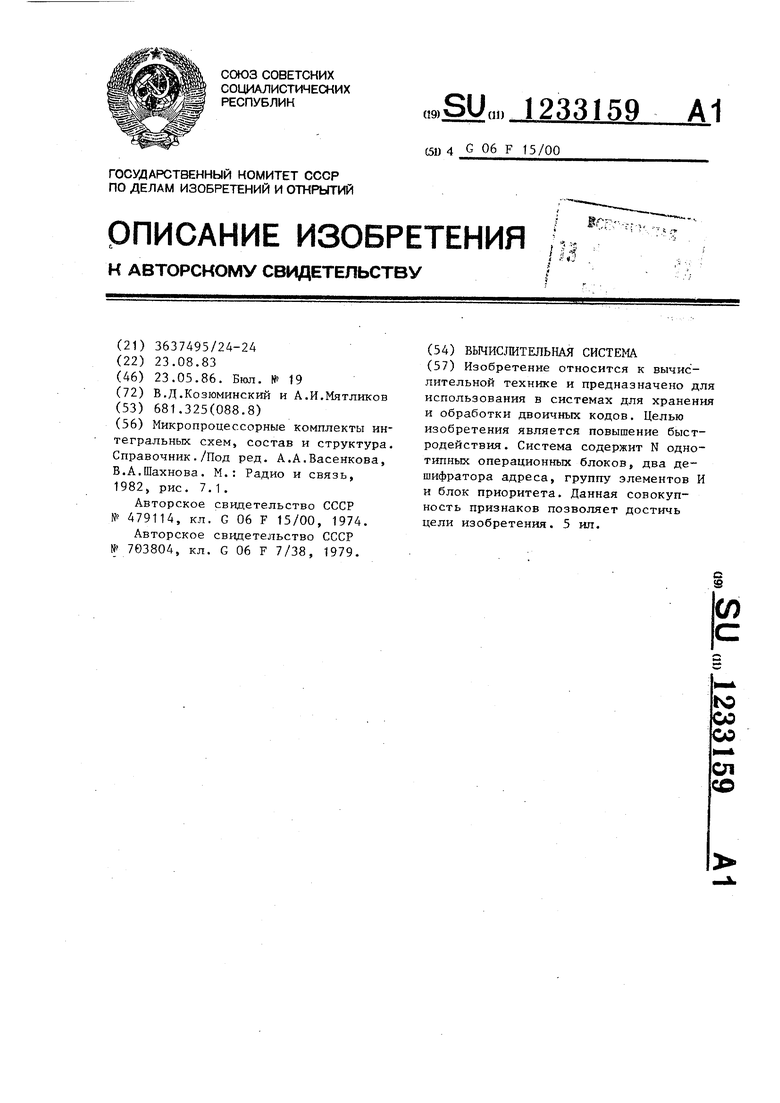

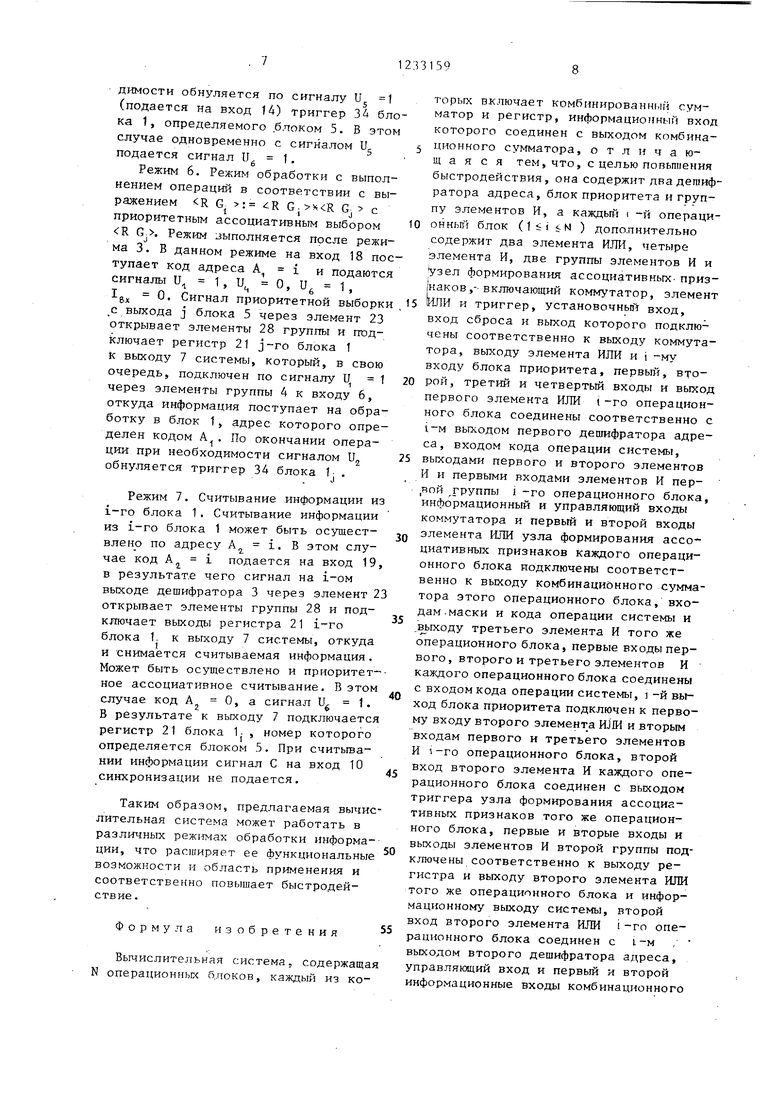

На фиг. 1 представлена структурная схема системы; на фиг. 2 - функциональная схема узла формирования ассоциативных признаков; на фиг. 3 - блок приоритета; на фиг. 4 - схема одного разряда комбинационного сумматора; на фиг. 5 - объединение отдельных разрядов комбинационного сумма

тора, 1

Система (фиг. 1) содержит N однотипных операционных блоков 1. -1.,, первый дешифратор 2 адреса, второй дешифратор 3 адреса, группу элементов И 4, блок 5 йриоритета и имеет информационный вход 6, информационный выход 7, вход 8 маски, вход 9 кода настройки (кода операции), вход 10 синхронизацииэ входы 11-17 кода операции, адресные входы 18 и 19. Опера ционный блок 1 содержит комбинацион- ньй сумматор 20, регистр 21, первый и второй элементы ИЛИ 22 и 23, первый Третий элементы И 24-26, первую и .вторую группы элементо з И 27 и 28, узел 28 формирования ассоциативных признаков и четвертый элемент И 30.

Входьт элемента 22 блока 1 подключены к i-му вькоду дешифратора 2, ,входу 11, выходам элементов И 24 и 251 Входы элементов И 27 первой группы подключены к выходу элемента 22 и входу 9 системы, а выходы этих элементов И - к управляющему входу сумматора 20, выходы которого подключены к входу регистра 21 и информационному входу узла 29. Первый информационный вход сумматора 20 подключен к выходу регистра 21 и входам элементов И 28 второй группы, а второй информационный вход сумматора 20 - к информационному входу 6 системы. Синхровход регистра 21 подключен к выходу элемента 30, входы которого подключены к выходу элемента 22 и входу 10 системы. Вход маски узл4 29 подключен к входу 8 маски систегхы а входы сброса узла 29 - к входу 15 системы и выходу элемента 26, выход узла 29 - к. первому входу .элемента 25 и i-му входу блока 5, i-й выход которого подключен к первым входам

. элементов

24

-6 и входу элемента

s

23,, второй вход которого подключен к i-му выходу дешифратора 3. Выход элемента 23 подключен к входам эл€ ментов И 28 второй группы, выходы которых подключены к информационному выходу 7 системы, который подключен также к входам элементов И 4 группы, другие входы которых подключены к входу 16 систе -ы, а выходы - к информационному входу 6 системы. Вторые входы элементов 24-26 подключены к входам 12-14 системы соответственно. Входы дешифраторов 2 и 3 подключены к адресным входам 18 и 19. системы. Стробирующий вход блока 5 подключен к входу 17 систеГ й.

Узел 29 формирования ассоциативных признаков (фиг. 2) содержит п элементов ИЛИ , элемент И 32, обра0 зующие коммутатор,, элемент ИЛИ 33, триггер 34 и имеет информационный вход 35.,-35, вход 36 -36 маски, первьм и второй входы 37 и 38 сброса и выход 39. При этом первые входы элементов 31 -31 подключены к разрядам информационного входа 35.,-35 , а их вторые входы - к разрядам входа 36,-36| маски, а выходы - к входам элемента 32, выход которого подключен

0 к единичному входу триггера 34. Нулевой вход триггера 34 подключен к выходу элемента 33, входы которого подключены к входам 37 и 38 узла, а выход триггера 34 - к выходу 39 узла. Блок 5 приоритета (фиг. 3) содержит N элементов И 40,-40, элементы НЕ 41. -41,

5

,.| -Tifj.. и имеет информационный вход 42,-42fg, Стробирующий вход 43 и выходы 44, -44|. При этом первый вход 0 элемента 40 (i 1,N) подключен к стробирующему входу 43 блока, второй вход элемента 40|- к входу 42 блока,

а остальныеi - 2 входов элемента

40

5

(1 2,N) -.к выходам элементов , входы элементов

41, к входам 42J блока, а выходы элемен- к выходам 44 -44., блотов 40 40( - ка приоритета.

Схема комбинационного сумматора 20 может быть построена по любому принципу. Операции, выполняемые сумматором, определяют операции, выполняемые б:ёэками 1 -1 системы. Например, схема известного разряда комбинационного сумматора (фиг. 4) реализует любые операции типа F1(A,B) F2(A,B), где F(A,B) - некоторая поразрядная логическая операция над операндами Ли В.

Схема одного разряда сумматора 20 содержит мультиплексоры 45 и 46 , элемент (ШИ 47, элемент И 48 и элемент 49 сложения по модулю два и первый информационный вход 50, второй инфор- мационньш вход 51, вход 5 переноса, управляющие входы 53, выход 54 результата и выход 55 переноса.

Схема п-разрядного сумматора 20 (фиг. 5) включает разряды сумматора 56 56 , при этом выходы 54 являютс вы}содами сигнала результата S i-ro разряда i i,n, а выходы 55 - выходами сигнала переноса из i-ro разряда. Кроме того, вход 52 переноса i-ro разряда подключен к выходу 54 переноса (i-1)-ro разряда. При обработке чисел в обратных кодах выход

Pj переноса п-го разряда сумматора подключается к входу 52 переноса первого разряда. При обработке чисел в дополнительных кодах выходы 54 и 52 сумматора не используются .

Функциональные возможности сумматора полиостью определяются функци- ональными возможностями одного разряда (фиг. 4). Реализация в сумматоре 20 операций типа S F1(A,B)+F2(A,B) достигается тем, что в схеме i-ro разряда (фиг. 4) выходноу сигнал результата S g (А ,В, )(5Р., , а

сигнал переноса

Р. (А,, В, )V

Б. )., , где cyL(A. , В, ) и

V&(A

р (А. , В ) - логические функции, реализуемые мультиплексорами 45 и 46 со-- ответственно, причем функция о.(А , ,Bj) F1(A, вра F2(A, В,), а функция ,в(А,, В,) F1(Aj, B.)®F2(A,. , В ). Возможность реализации мульти111 О

о о

Для настройки мультиплексоров необхо

плексором логических функций вытека- ,димо значения О и 1 логических функ-г

ций Ы и Р) подать на соответствующие входы 53.

ет из логического выражения мультиплексора, например, для мультиплексора 45 можно записать

o/(A.,B).U,VA,B,

VA,.B,U. где А: и В,

(1)

- сигналы, подаваемые на информационные входы 50 и 51 мультиплексораjSO и Uj - сигналы настройки , подаваемые на управляю- щие входы 53 мультиплексора.

Так как при настройке схемы сигналы 55 Uj, -Uj принимают нулевое или единич ное значение в зависимости от реализуемой функции, то логическое выраi;. ;rMS94

жрнио (О упропин тч я. n.iripHMi. p, при .11 и, 0 и и, U, 1 из О) получим (A ,8 ) , VA.,B|.

Для реализации в сумматоре 20, 5 выполненном в соответствии с фиг. 4 и 5, операции S F1(A,B) + F2(A,B), необходимо найти значения функций

45 и 46 соответственно при всех на- борах их аргументов, и подать эти значения на соответствующие входы настройки мультиплексоров. Например, пусть требуется выполнить операцию S А + В. Тогда F1(A,B)A, а F2(A,B) В. Для нахождения логических функций (А. ,В|) и р(А, Bj ), реализуемых соответственно мультиплексорами 45 |И 46 i-ro разряда (i 1,п) при выполнении в сумматоре заданной операции, составляют таблицу истинности требуемой операции для i-ro разряда без учета сигналов, переноса Р, , из (i-1)-ro разряда.

1-1

0О

11 1 О

о о

о о

Для настройки мультиплексоров необхо,димо значения О и 1 логических функ-г

ций Ы и Р) подать на соответствующие входы 53.

Вычислительная система может работать в нескольких режимах.

Режим 1. Операции выполняются в i-oM блоке 1 в соответствии с выражением

R G.

: R G. 1, 1 ex

:где RG - содержимое регистра 21

i-ro блока; ;1 - информация на входе 6

системы;

- некоторая операция, выполняемая сумматором 20. Для реализации этого режима на вход дешифратора 2 подается адрес А i (на JBXOA 16), на вход 6 - двоичная

информация Ijj , на вход 9 сумматора код настройки U, соответствующий операций .л . Сигналы на остальньк ;зхо- дах системы равны Hyjno. Операция выполняется только в том блоке 1, вход элемента 22 которого подключен к возбуждаемому выходу дешифратора 2 что определяется кодом А i, поступающим на вход дешифратора 2. По сигналу синхронизации GS подаваемому на вход 10J производится запись результата операции в регистр 21 i-ro блока 1 ,

Режим 2, Операция выполняется в i-OM блоке 1 в соответствии с выражением

R G. : R G «- R Gj ,

где R G. - содержимое регистра 21

j-го блока, j i,

В отличие от предыдущего режима работы в этом режиме входная информа- ция Jgx на вход 6 не подается, а на вход 19 подается код,адреса А j , на вход 16 - сигнал U 1. В этом режиме сигналы с выхода регистра 21 j-ro блокаJ номер которого определен адресом А, поступают через группу элементов 28, открытых сигналом с выхода дешифратора 3, на выход 7 системы и через группу элементов 4, открытых сигналом Ц - на вход 6, что обеспечивает подключение выходов регистра 21 j-ro блока 1 к входам сумматора i-ro блока 1.

Режим 3. Выполняются операции ассоциативного поиска. В этом режиме происходит установка триггера 34 узл 29 тех блоков 1 , для которьк вьгх:од- ные сигналы всех незамаскированных разрядов сумматора 20 равны 1 при выполнении в этих сумматорах любой из операций типа

1 их

i 1 , N,

Перед реализацией данного режима производится обнуление триггеров 34 всех блоков 1 сигналом U 1, подаваемым на вход 15 системы. На вход 9 подается код U выбора операции, выполняемой в сумматоре 20, на вход 6 - код J , на вход 11 - сигнал U- 1. В результате действия сигнала Uj открыты элементы 27 и 30 блоков 1 независимо от кода адреса А, и код U выбора операции поступает одновре

менно на входы кода операции сумматоров всех блоков 1 и в сумматорах 20 выполняется операция R Gp JB. , i 1, N.

Результат этой операции с выхода каждого сумматора 20 поступает на входы , элементов ИЛИ узла 29. Если при этом во всех разрядах сигналы равны 1, то на выходе элемента 32 узла 29 появляется сигнал 1, который устанавливает триггер 34 в единичное состояние. Если требуется проверить не все разряды суммато

ра 20 на равенство их 1, то в этом случае на вход 8 подается код маски „, в котором для проверяемых разрядов сигнал .равен О, а для маскируемых разрядов - 1. В режиме ассоциативного поиска сигнал синхронизации С на вход 10 не подается.

Режим 4. Режим ассоциативной обработки. Этот режим может выполняться только после режима 3 (ассоциативного п®иска). Обработка производится во всех блоках, в которых триггер 34 узла 29 находится в единичном состо- янии,, и выполняется в соответствии с выражением R G. . Выполнение операций производится так же-, как в режиме 1, но адрес , а сигнал Uj на входе 12 равен 1, Если в этом режиме сигнал А i, то обработка в i-ом блоке 1 выполняется независимо от состояния триггера 34 i-ro блока 1.

Режим 5. Режим ассоциативной приоритетной обработки. Обработка выполняется так же, как и в примере 4, но сигнал U,.j О,

а сигнал U . на входе

Сигнал и, II1II

g на входе 17 Блок 5 приоритета

13 равен 1,

также равен 1

определяет старший по приоритету блок

1j (i 1 ,N) , в котором триггер 34

находится в единичном состоянии. Под

действием сигнала U, 1 на выходе

b

блока 5 появляется сигнал, определяющий старший по приоритету блок 1, в котором на вькоде триггера 34 присутствует 1. Этот сигнал через элементы 24 (так как Иц 1) соот- ветстЕ;ующего блока 1 и элемент 22 открывает элементы 27 и 30. В результате только в выбранном блоке 1 обеспечиваются выполнение в сумматоре 20 требуемой операции и запись результата по сигналу С в регистр 21. По окончании данного режима при необходимости обнуляется по сигналу U 1 (подается на вход 14) триггер 34 блока 1, определяемого блоком 5. В этом случае одновременно с сигналом U подается сигнал U, 1,

О

Режим 6, Режим обработки с выполнением операций в соответствии с выражением R G : iR G с приоритетным ассоциативным выбором R Gj. Режим выполняется после режима 3. В данном режиме на вход 18 поступает код адреса А i и подаются сигналы и 1 и О, и 1, Igjj 0. Сигнал приоритетной выборки с выхода j блока 5 через элемент 23 открывает элементы 28 группы и шэд- 1ключает регистр 21 j-ro блока 1 К выходу 7 системы, который, в свою очередь, подключен по сигналу Ц 1 через элементы группы 4 к входу 6, откуда информация поступает на обработку в блок 1, адрес которого определен кодом А. По окончании операции при необходимости сигналом U обнуляется триггер 34 блока 1- .

.

Режим 7. Считывание информации из i-ro блока 1. Считывание информации из i-ro блока 1 может быть осушест- влево по адресу А i. В этом случае код А. i подается на вход 19, в результата чего сигнал на i-ом выходе дешифратора 3 через элемент 23 открывает элементы группы 28 и подключает выходы регистра 21 i-ro блока 1. к выходу 7 системы, откуда и снимается считываемая информация. Может быть осуществлено и приоритет- ное ассоциативное считывание. В этом

случае код А 0, а сигнал U 1 В результате к выходу 7 подключается регистр 21 блока 1-, номер которого определяется блоком 5. При считывании информации сигнал С на вход 10 синхронизации не подается.

Таким образом, предлагаемая вычислительная система может работать в различных режимах обработки информации, что расширяет ее функциональные возможности и область применения и соответственно повышает быстродействие .

Формула изобретения

Вычислительная система, содержащая N операционных б.локов, каждый из ко5

0 520 25

0

5

0

5

торых включает комбинированнрпй сумматор и регистр, информационный вход которого соединен с выходом комбинационного сумматора, отличающаяся тем, что, с целью повьгагения быстродействия, она содержит два дешифратора адреса, блок приоритета и группу элементов И, а каждый i -и операционный блок (1ь tN ) дополнительно содержит два элемента ИЛИ, четыре элемента И, две группы элементов И и Узел формирования ассоциативных- приз- |наков,--включающий коммутатор, элемент ИЛИ и триггер, установочньй вход, вход сброса и выход которого подключены соответственно к выходу коммутатора, выходу элемента ИЛИ и i -му входу блока приоритета, первый, второй, третий и четвертый входы и выход первого элемента ИЛИ i -го операционного блока соединены соответственно с I-M выходом первого дешифратора адреса, входом кода операции системы, выходами первого и второго элементов И и первыми входами элементов И пер- ,вой группы i -го операционного блока, информационный и управляющий входы коммутатора и первый и второй входы элемента ИЛИ узла формирования ассоциативных признаков каждого операционного блока подключены соответственно к выходу комбинационного сумматора этого операционного блока, входам- маски и кода операции системы и выходу третьего элемента И того же операционного блока, первые входы первого, второго и третьего элементов И каждого операционного блока соединены с входом кода операции системы, i -и выход блока приоритета подключен к первому входу второго элемент а ИЛИ и вторым входам первого и третьего элементов И 1-го операционного блока, второй вход второго элемента И каждого операционного блока соединен с выходом триггера узла формирования ассоциативных признаков того же операционного блока, первые и вторые входы и вькоды элементов И второй группы подключены соответственно к выходу регистра и вьгходу второго элемента ИЖ того же операционного блока и информационному выходу системы, второй вход второго элемента ИЛИ i-го операционного блока соединен с i-м , выходом второго дешифратора адреса, управляющий вход и первый и второй информационные входы комбинационного

суммлтора каждого операционного блока подключены соответственно к выходам элементов И первой группы и выходу регистра того же операционного блока и информационном входу системы, вторые входы элементов И первой группы каждого операционного блока соединены с входом кода операции системы, выход и первый и второй входы четвертого элемента И каждого операционного блока подключены соответственно к синхровходу регистра.

выходам элементов И первоГ: Г руппы того же операционного блока и входу синхронизации системы, первые и вторые входы и выходы элементов И группы соединены соответственно с входоу кода операции и информационным выходом системы и вторыми информационными входами комбинационных сумматоров всех операционных блоков, а входы первог о и второго дешифраторов адреса подключены к адресному входу системы.

Фиг2 tZ34t,t.i «

ф- ф

43

Ч0г W/ I {

w, HV, ФигЗ

5051

--ЧЧн

51

Редактор Н. Рогулич

Составитель Г. Виталиев Техред О.Сопко

Заказ 2772/51

Тираж 671

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-J5, Раушская наб., д. 4/5

Производстренно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Фмг,5

Bi

Корректор Е.Сирохман

Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для реализации логических функций | 1983 |

|

SU1257658A2 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| Многопроцессорная вычислительная система | 1982 |

|

SU1168960A1 |

| Устройство для сжатия данных при обмене между электронными вычислительными машинами | 1983 |

|

SU1118996A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1030801A1 |

| УСТРОЙСТВО ДЛЯ ПАРАЛЛЕЛЬНОЙ ОБРАБОТКИ ДАННЫХ | 1991 |

|

RU2028664C1 |

| Устройство для реализации временных булевых функций | 1985 |

|

SU1290346A1 |

| Устройство для поиска информации в памяти | 1985 |

|

SU1352494A1 |

| Микропрограммный процессор | 1986 |

|

SU1365091A1 |

| Вероятностная вычислительная машина | 1986 |

|

SU1455344A1 |

Изобретение относится к вычислительной технике и предназначено для использования в системах для хранения и обработки двоичных кодов. Целью изобретения является повышение быстродействия. Система содержит N однотипных операционных блоков, два дешифратора адреса, группу элементов И и блок приоритета. Данная совокупность признаков позволяет достичь цели изобретения. 5 ил. кэ оо 00 ел со

| Микропроцессорные комплекты интегральных схем, состав и структура | |||

| Справочник./Под ред | |||

| А.А.Васенкова, В.А.Шахнова | |||

| М.: Радио и связь, 1982, рис | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Ассоциативный параллельный процессор | 1973 |

|

SU479114A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Цифровой автоматический мост следящего уравновешивания | 1978 |

|

SU763804A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-05-23—Публикация

1983-08-23—Подача