Изобретение относится к вычислительной технике и может использоваться припостроении устройств обработки цифровой информации в ЭВМ.

Известно устройство для сложения двоично-десятичных кодов, содержащее сумматоры, схемы переноса и коррекции 1..

Недостатком устройства является то, что оно не реализует операций сложения двоичных кодов и логических операций.

Наиболее близким по технической сущности к предлагаемому является устройство для арифметической и логической обработки двоичных чисел, каждый разряд которого содержит информационные входы и два входа переноса, выход результата и два выхода переноса, управляющие входы, элелюнты И, ИЛИ, ИСКЛЮЧАЮЩЕЕ ИЛИ - выходва мультиплексора i управляющие входы которых попарно объединены и подключены к информационным входам уст.ройства, информационные входы мулытиплексоров являются управляющими входами устройства. Выход первого мультиплегксора соединен с первЕэГми входами первого и второго элементов И и первого элемента ИСКЛЮЧАКЯЦЕЕ ИЛИ и

второй вход которого соединен с.вторым входом первого элемента И и вы- i ходом третьего элемента И/ входы которого попарно объединены с входами второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ И подключены к входам переносаразряда. Выход второго элемента ИСКЛЮ- . ЧАЮЩЕЕ .ИЛИ соединен с вторым входом второго элемента И и первым вхо10дом четвертого элемента И и третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, вторые входы которых объединены и подключены к выходу второго мультиплексора и третьему входу второго элемента И,

15 выход которого соединен с третьим входом первого элемента ИСКЛП- i ЧАЩЕЕ ИЛИ соединен с вторым вхо-. входом первого элемента ИЛИ, другой вход которого соединен с выходом

20 четвертого элемента И. Выходы второго элемента ИЛИ подключены к выходам первого и второго элементов И. Выходы элементов ИЛИ являются выходами переноса, а выход третьего

25 элемента ИСКЛЮЧАЮЩИЕ ИЛИ - выхо- дом результата устройства 2.

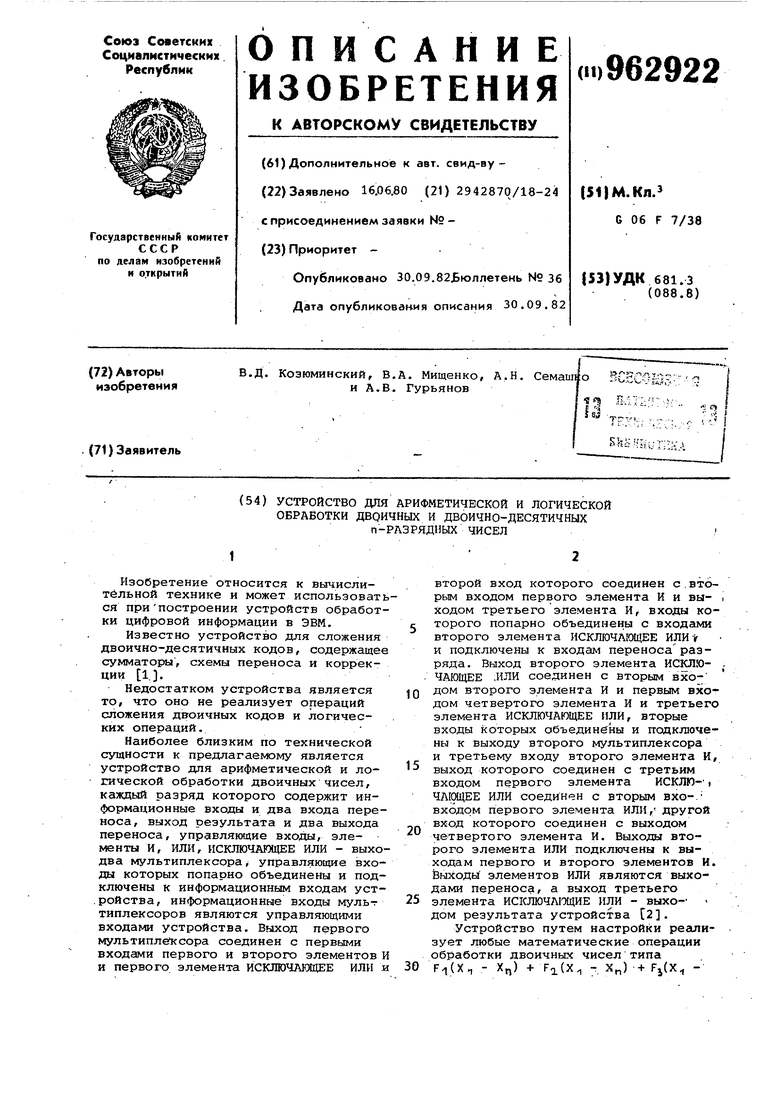

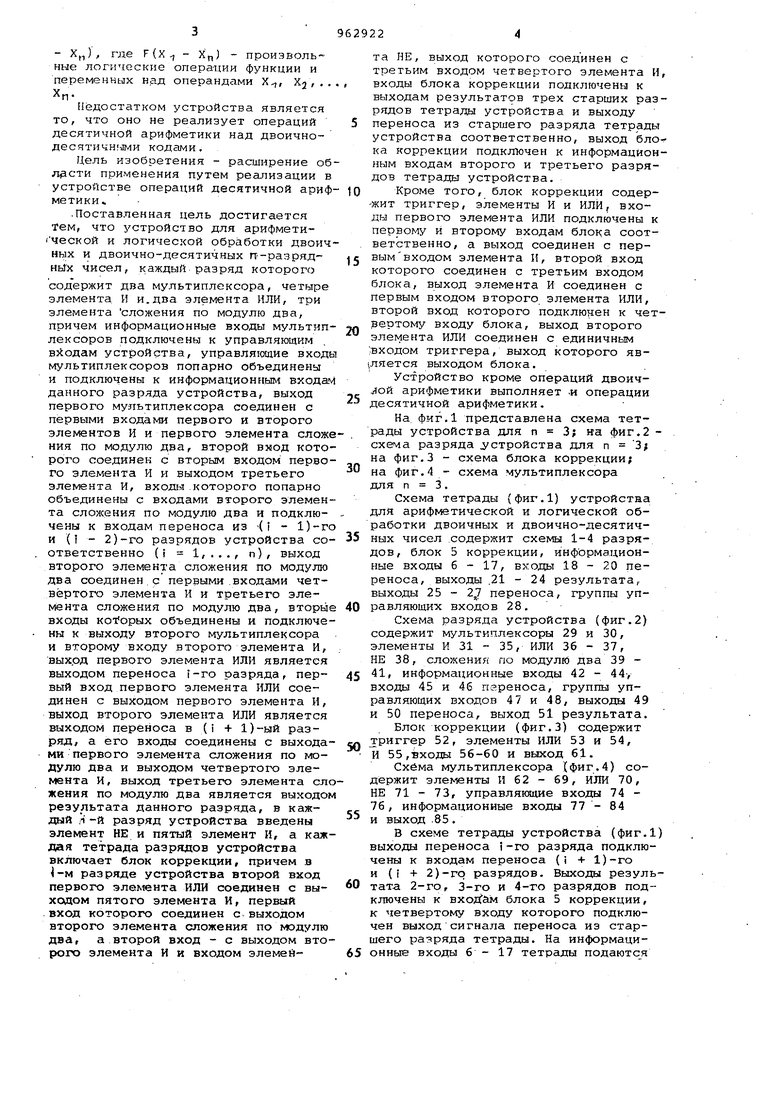

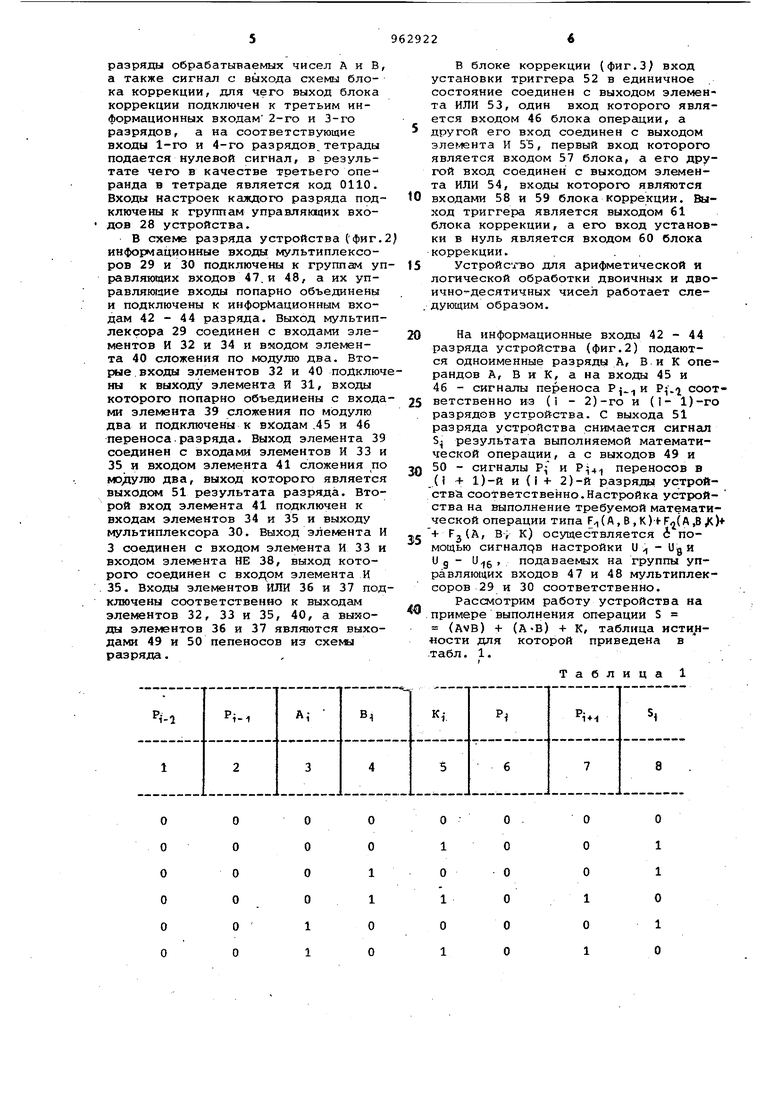

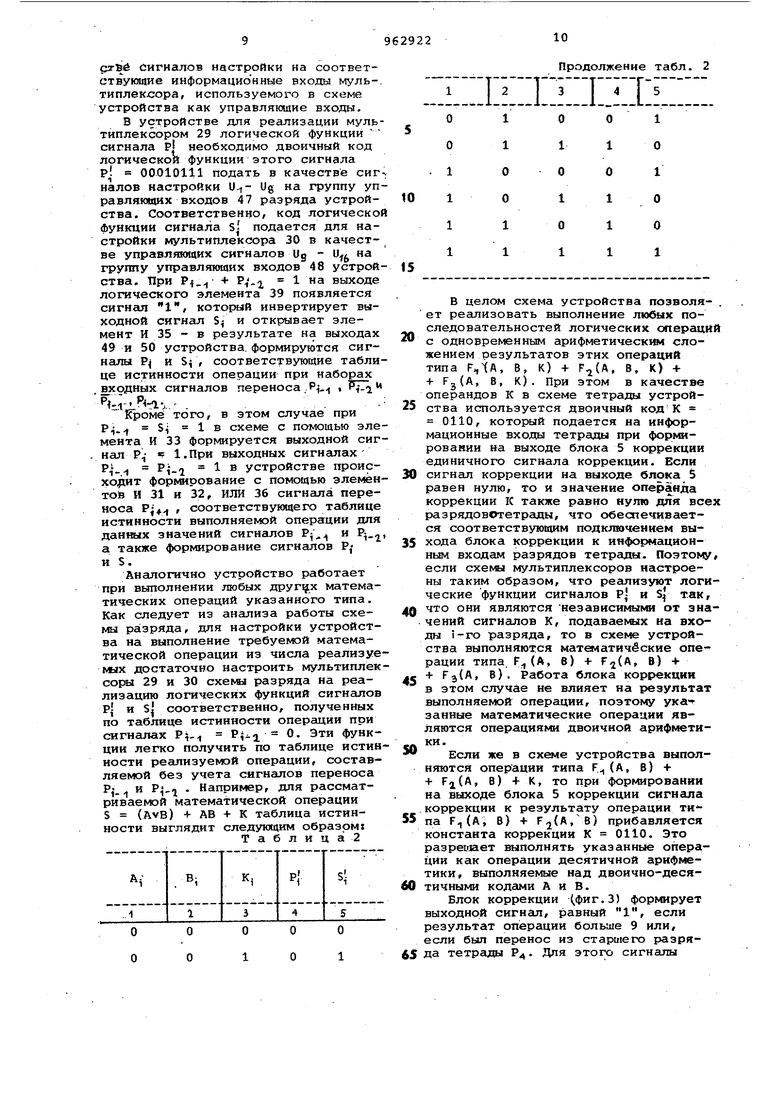

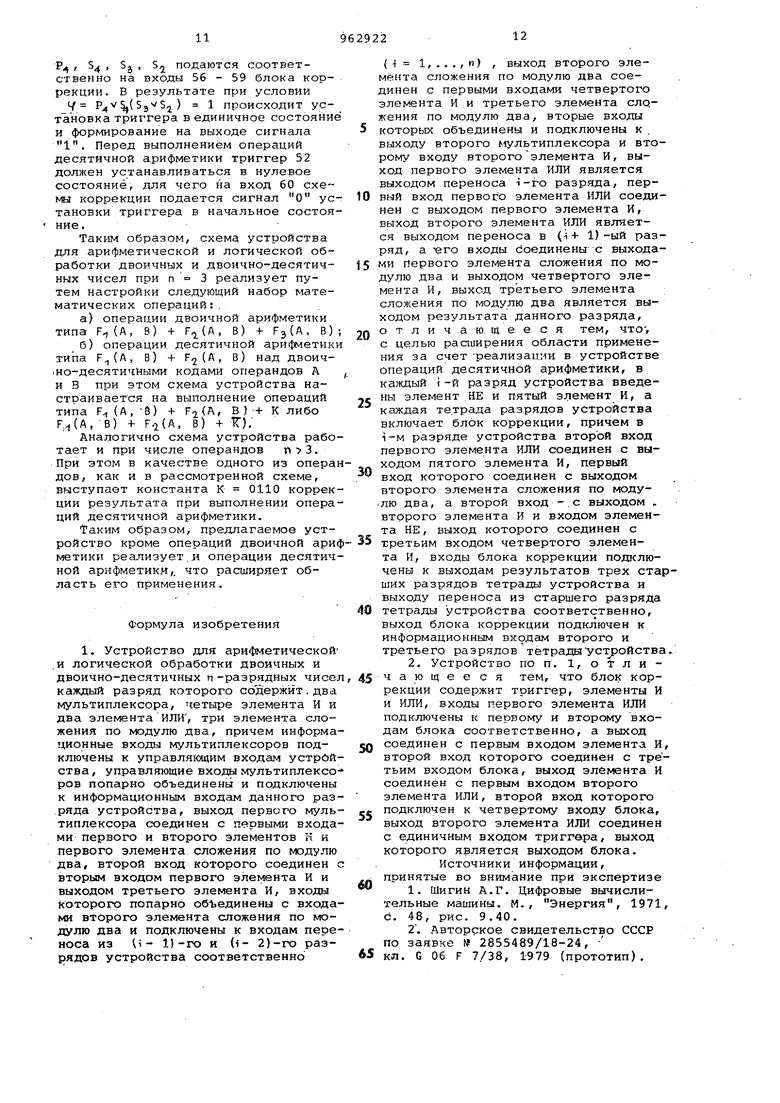

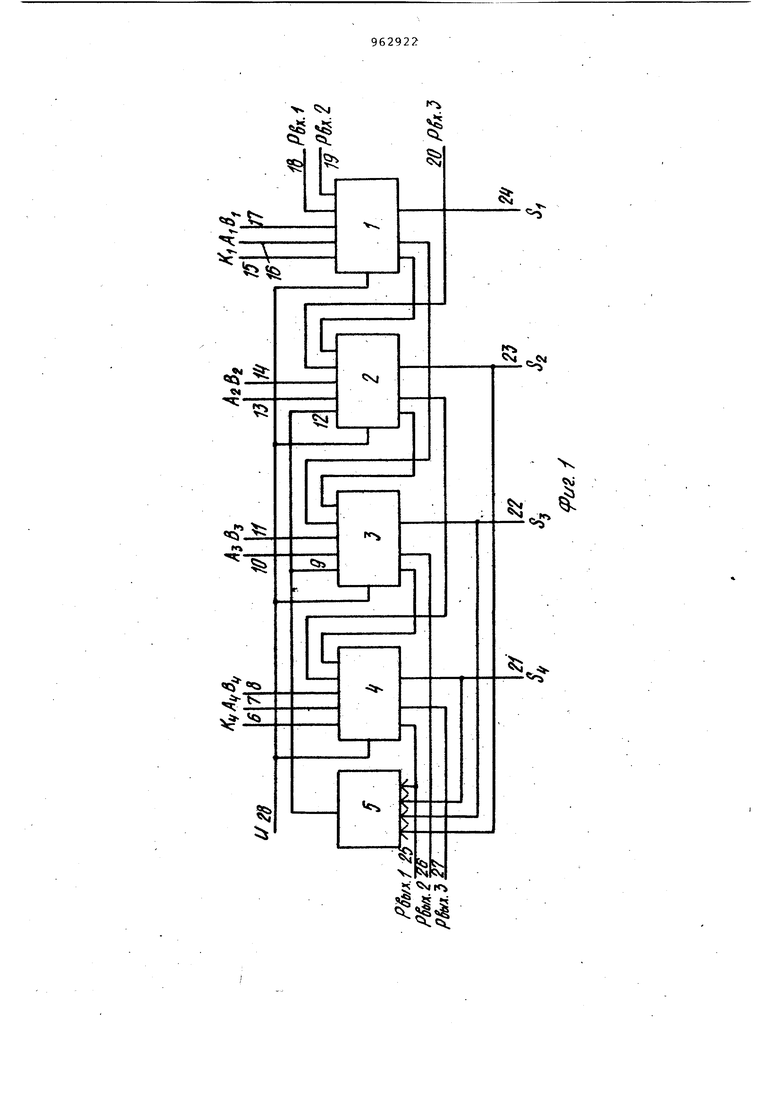

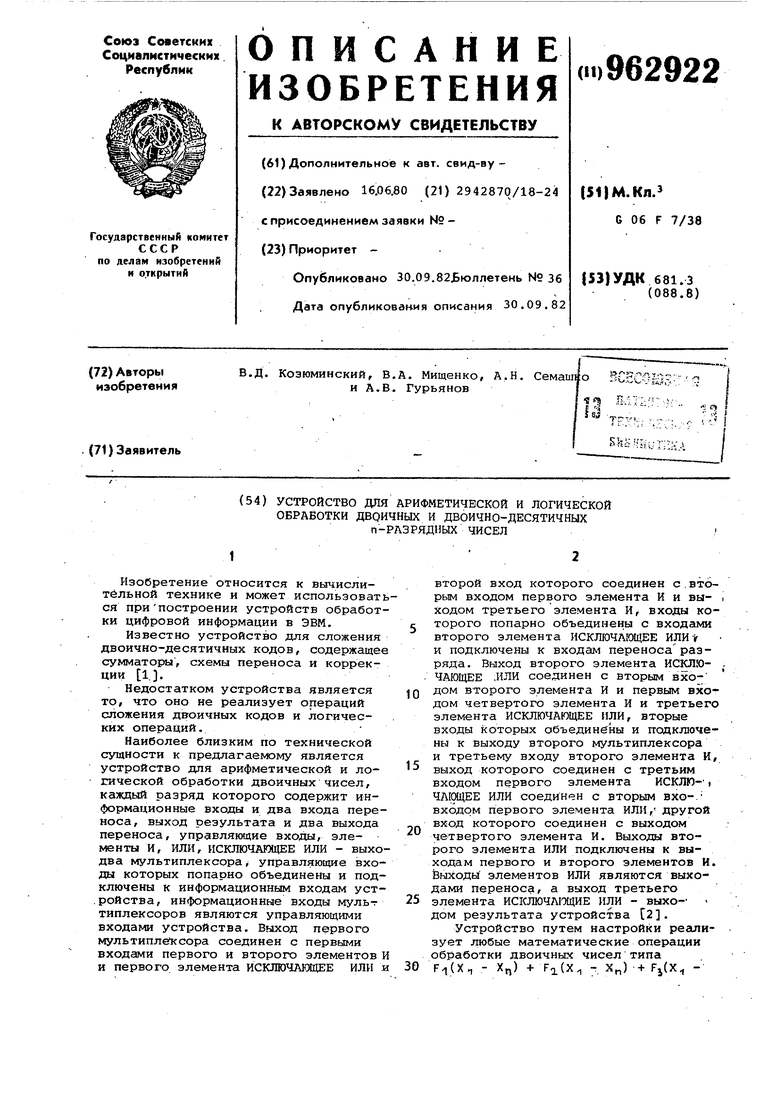

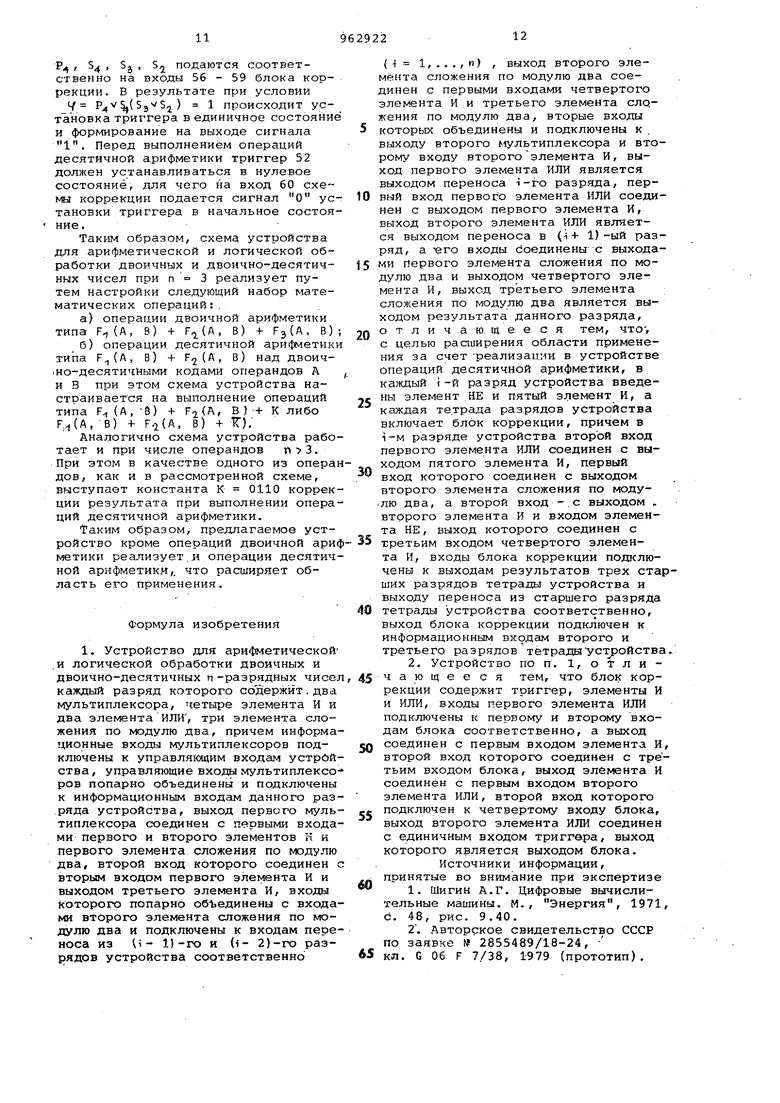

Устройство путем настройки реализует любые математические операции обработки двоичных чисел типа 30 F(XT - Х„) + Fi(X - Хп) + Fj(X - Х„), где F(X - х„) - произвольные логические операции функции и переменных ндд операндами Х, Xj , . Недостатком устройства является то, что оно не реализует операций десятичной арифметики над двоичнодесятнчнглми кодами. Цель изобретения - расширение об лэсти применения путем реализации в устройстве операций десятичной ариф метики .Поставленная цель достигается Тем, что устройство для арифмети 1ческой и логической обработки двоич ных и двоично-десятичных ГР-разрядных чисел, каждый разряд которого содержит два мультиплексора, четыре элемента. И и.два элемента ИЛИ, три элемента сложения по модулю два, причем информационные входы мультиплексоров подключены к управляющим В54одам устройства, управляющие входы мультиплексоров попарно объединены и подключены к инфopмaциoнны t входам данного разряда устройства, выход первого мультиплексора соединен с первыми входами первого и второго элементов И и первого элемента сложе ния по модулю два, второй вход кото рого соединен с вторым входом перво го элемента И и выходом третьего элемента И, входы которого попарно объединены с входами второго элемен та сложения по модулю два и подключены к входам переноса из -(i - 1)-го и (i - 2)-го разрядов устройства со ответственно (i 1,..., п), выход второго элемента сложения по модулю два соединен с первыми входами четвёртого элемента И и третьего элемента сложения по модулю два, вторы входы которых объединены и подключе ны к выходу второго мультиплексора и второму входу второго элемента И, выход первого элемента ИЛИ является выходом переноса -го разряда, первый вход первого элемента ИЛИ соединен с выходом первого элемента И, выход второго элемента ИЛИ является выходом переноса в (i + 1)-ый раэряд, а его входы соединены с выхода ми первого элемента сложения по модулю два и выходом четвертохх) элемента И, выход третьего элемента сл жения по модулю два является выходо результата данного разряда, в каждый л -и разряд устройства введены элемент НЕ и пятый элемент И, а каж дая тетрада разрядов устройства включает блок коррекции, причем в -м разряде устройства второй вход первого элемента ИЛИ соединен с выходом пятого элемента И, первый вход которого соединен с-выходом второго элемента сложения по мэдулю два, а второй вход - с выходом вто рого элемента И и входом элемента НЕ, выход которого соединен с третьим входом четвертого элемента И, входы блока коррекции подключены к выходам результатов трех старших разрядов тетрады устройства и выходу переноса из старшего разряда тетрады устройства соответственно, выход блогка коррекции подключен к информационным входам второго и третьего разрядов тетрады устройства. Кроме того, блок коррекции содержит триггер, элементы И и ИЛИ, входы первого элемента ИЛИ подключены к первому и второму входам блока соответственно, а выход соединен с первымвходом элемента И, второй вход которого соединен с третьим входом блока, выход элемента И соединен с первым входом второго элемента ИЛИ, второй вход которого подключен к четрертому входу блока, выход второго элемента ИЛИ соединен с единичным ;Входом триггера, выход которого явЛяется выходом блока. Устройство кроме операций двоичлоЛ арифметики выполняет -и операции десятичной арифметики. На фиг,1 представлена схема тетрады устройства для п 3; на фиг.2 схема разряда устройства для п 3; на фиг.З - схема блока коррекции; на фиг.4 - схема мультиплексора для п 3. Схема тетрады {фиг.1) устройства для арифметической и логической обработки двоичных и двоично-десятичных чисел содержит схемы 1-4 разрядов, блок 5 коррекции, информационные входы 6-17, входы 18 - 20 переноса, выходы .21 - 24 результата, выходы 25 - 2,7 переноса, группы управляющих входов 28. Схема разряда устройства (фиг.2) содержит мультиплексоры 29 и 30, элементы И 31 - 35, ИЛИ 36 - 37, НЕ 38, сложения по модулю два 39 41, информационные входы 42 - 44-, входы 45 и 46 пареноса, группы управляющих входов 47 и 48, выходы 49 и 50 переноса, выход 51 результата. Блок коррекции (фиг.З) содержит триггер 52, элементы ИЛИ 53 и 54, И 55,ходы 56-60 и выход 61. Схема мультиплексора {фиг.4) содержит элементы И 62 - 69, ИЛИ 70, НЕ 71 - 73, управляющие входы 74 76, информационные входы 77 - 84 и выход .85. В схеме тетрады устройства (фиг.1) выходы переноса i-го разряда подключены к входам переноса (i + 1)-го и (i + 2)-го разрядов. Выходы результата 2-го, 3-го и 4-го разрядов подключены к вхоДам блока 5 коррекции, к четвертому входу которого подключен выход сигнала переноса из старшего разряда тетрады. На информационные входы 6 - 17 тетрады подаются

разряды обрабатываемых чисел А и В, а также сигнгш с выхода схемы блока коррекции, для чего выход блока коррекции подключен к третьим информационных входам 2-го и 3-го разрядов, а на соответствующие входы 1-го и 4-го разрядов тетрады подается нулевой сигнал, в результате чего в качестве третьего операнда в тетраде является код ОНО. Входы настроек каждого разряда подключены к группам управляющих входов 28 устройства.

В схеме разряда устройства (фиг.2 информационные входы мультиплексоров 29 и 30 подключены к группам управляющих входов 47,и 48, а их управляющие входы попарно объединены и подключены к информационным входам 42-44 разряда. Выход мультиплексора 29 соединен с входами элементов И 32 и 34 и входом элемента 40 сложения по модулю два. Вторые .входы элементов 32 и 40 подключны к выходу элемента И 31, входы которого попарно объединены с входами элемента 39 сложения по модулю два и подключены к входам ,45 и 46 переноса.разряда. Выход элемента 39 соединен с входами элементов И 33 и 35 и входом элемента 41 сложения по модулю два, выход которого является выходом 51 результата разряда. Второй вход элемента 41 подключен к входам элементов 34 и 35 и выходу мультиплексора 30. Выход элемента И 3 соединен с входом элемента И 33 и входом элемента НЕ 38, выход которого соединен с входом элемента И 35. Входы элементов ИЛИ 36 и 37 подключены соответственно к выходам элементов 32, 33 и 35, 40, а выходы элементов 36 и 37 являются выходами 49 и 50 пепеносов иэ схегла разряда.

В блоке коррекции (фиг.З) вход установки триггера 52 в единичное состояние соединен с выходом элемента ИЛИ 53, один вход которого является входом 46 блока операции, а другой его вход соединен с выходом И 55, первый вход которого является входом 57 блока, а его другой вход соединен с выходом элемента ИЛИ 54, входы которого являются

0 входами 58 и 59 блока коррекции. Выход триггера является выходом 61 блока коррекции, а его вход установки в нуль является входом 60 блока коррекции.

5 Устройство для арифметической и логической обработки двоичных и двоично-Десятичных чисел работает сле. дующим образом.

0 На информационные входы 42 - 44 разряда устройства (фиг.2) подаются одноименные разряды А, В.и К операндов А, В и К, а на входы 45 и 46 - сигналы переноса .- соответственно из (i - 2)-го и (1- 1)-го . разрядов устройства. С выхода 51 разряда устройства снимается сигнал S- результата выполняемой математической операции, а с выходов 49 и

Q 50 - сигналы Р( и переносов в (i + 1)-й и (i + 2)-и разряды устройства соответственно. Настройка устройства на выполнение требуемой математической операции типа F(A, В ,K)F(A,B)

FjlA, By к) осуществляется 4 помощью сигналов настройки U , - Ug и

J.9подаваемых на группы уп16

равляющих входов 47 и 48 мультиплексоров 29 и 30 соответственно.

Рассмотрим работу устройства на .примере выполнения операции S (AVB) + (А-в) + К, таблица иcти «ости для которой приведена в

.табл. 1.

I

Таблица 1

962922

Продолжение табл. 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Двоично-десятичное арифметико-логическое устройство накапливающего типа | 1981 |

|

SU1024904A1 |

| Устройство для суммирования двоично-десятичных чисел | 1980 |

|

SU1001087A1 |

| Арифметическое устройство с микропрограммным управлением | 1990 |

|

SU1797108A1 |

| Двоично-десятичный сумматор | 1984 |

|

SU1241233A1 |

| Устройство для обработки данных переменной длины | 1986 |

|

SU1675897A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Арифметическое устройство с микропрограммным управлением | 1989 |

|

SU1725216A1 |

| Накапливающий сумматор | 1982 |

|

SU1166096A1 |

| Операционное устройство | 1982 |

|

SU1113805A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1300640A1 |

Для выполнения устройством данной математической операции мультиплексор 29 настраивается на реализа-. цию в нем логической функции Р| из таблицы истинности при значениях входных сигналов переноса, Р. Pj,. О, а мультиплексор 30 - на реализацию логической функции сигг нала таблицы истинности при этих же65 значениях входных сигналов переноса Р. и Р,, . Как следует из схемы мультиплексора (фиг,4), для его настройки на соответствунвдую логическую функцию трех аргументов, подаваемых на его управдяющие входы, достаточно двоичный код этой логической функции ,из таблицы истинности подать в качертВё сигналов настройки на соответствующие информационные входы муль-. типлексора, используемого в схеме устройства как управляющие входы.

В устройстве для реализации мультиплексором 29 логической функций сигнала р| необходимо двоичный код логической функции этого сигнала р 00010111 подать в качестве сигналов настройки Ug на группу управлякхцих входов 47 разряда устройства. Соответственно, код логической функции сигнала s| подается для настройки мультиплексора 30 в качестве управляющих сигналов Ug - U на группу управляющих входов 48 устройства. При Pi + PI-I э выходе логического элемента 39 появляется сигнал 1, который инвертирует выходной сигнал S{ и открывает элемент И 35 - в результате на выходах 49 и 50 устройства, формируются сигналы Р и 5 , соответствующие таблице истинности операции при наборах

входных сигналов переноса Р. . fl-o.

.- .

Кроме того, в этом случае при

PI.-( 1 в схеме с помощью элемента И 33 формируется выходной сигнал Р,- « 1.При выходных сигнзшах pi Р, 1 в устройстве происхо ит форютрование с помощью элеменTOiB И 31 и 32, ИЛИ 36 сигнала переноса ( , соответствующего таблице истинности выполняемой операции для данных значений сигналов Р. и Р;;, а также формирование сигналов Pj и S.

Ансшогично устройство работает при выполнении любых других математических операций указанного типа. Как следует из анализа работы схемы разряда, для настройки устройства на выполнение требуемой математической операции из числа реализуемых достаточно настроить мультиплексоры 29 и 30 cxeNSd разряда на реализацию логических функций сигнгиггов Р- и S| соответственно, полученных по таблице истинности операции при сигналах О- Эти функции легко получить по таблице истинности реализуемой операции, составляемой без учета сигналов переноса Р|. - и Р . Например, для рассматриваемой математической операции S (AVB) + АВ ч- К таблица истинности выглядит следующим образом Таблица 2

Продолжение табл. 2

:ii:: :i::i:i: 3 1415

to

15

в целом схема устройства позволяет ресшизовать выполнение любых последовательностей логических операций с одновременным арифметическим сложением результатов этих операций типа F,,XA, В, К) + F(A. В, К) + + Fg(A, в, к). При этом в качестве операндов К в схеме тетрады устройства используется двоичный код К ОНО, который подается на информационные входы тетрады при формировании на выходе блока 5 коррекции единичного сигнала коррекции. Если

сигнал коррекции на выходе блока 5 равен нулю, то и значение операнда коррекции К также равно нулю для всех разрядовотетрады, что обеспечивается соответствующим подключением выхода блока коррекции к информационным входам разрядов тетрады. Поэтому, если схемы мультиплексоров настроены таким образом, что регшизуют логические функции сигналов Р- и s{ так,

что они являются независимыми от значений сигналов К, подаваемых на входы i-ro разряда, то в схеме устройства выполняются математические операции типа F.|(A, в) +

) Работа блока коррекции в этом случае не влияет на результат выполняемой операции, поэтому уха- занные математические операции являются операциями двоичной арифметики.

Если же в cxaute устройства выполняются операции типа Г(А, В) + + f(P(, В) + К, то при формировании на выходе блока 5 коррекции сигнала коррекции к результату операции ти-па F(Aj В) + Fj(A/B) прибавляется константа коррекции К ОНО. Это разрешает выполнять указанные операции как операции десятичной арифметики, выполняемые над двоично-десяТИЧНЫМИ КОДс1МИ А и В.

Блок коррекции (,фиг.З) формирует выходной сигнал, равный 1, если езультат операции больше 9 или, сли был перенос из старшего разряЗ тетрады Р. Для этого сигналы

подаются соответ f,

ственно на входы 56-59 блока коррекции. В результате при условии Ч Р %( ) 1 происходит установка триггера в единичное состояние и формирование на выходе сигнала 1. Перед выполнением операций десятичной арифметики триггер 52 должен устанавливаться в нулевое состояние, для чего на вход 60 схеNttj коррекции подается сигнал О установки триггера в начальное состояние.

Таким образом, схема устройства для арифметической и логической обработки двоичных и двоично-десятичных чисел при п ° 3 реализует путем настройки следующий набор математических операций;.

а)операции двоичной арифметики типа F(A, В) + F(A, В) + В);

б)операции, десятичной ари(1метики типа F.(A, в) + , в) над двоич.но-десятичНыми кодами операндов А и В при этом схема устройства настраивается на выполнение операций типа Р(А,б) + Fi(A, В) + К либо F,(A, В) + F7(A, в) + 1Г);

Аналогично схема устройства работает и при числе операндов п 3. При этом в качестве одного из операндов, как и в рассмотренной схеме, выступает константа К ОНО коррекции результата при выполнении операций десятичной арифметики.

Таким образом, предлагаемое устройство кроме операций двоичной арифметики реа-пизует .и операции десятичной арифметики,, что расширяет область его применения.

Формула изобретения

(i 1,...,п) , ВЫХОД второго элемента сложения по модулю два соединен с первыми входами четвертого элемента И и третьего элемента сложения по модулю два, вторые входы которых объединены и подключены к . выходу второго мультиплексора и второму входу второгоэлемента И, выход первого элемента ИЛИ является выходом переноса i-ro разряда, первый вход первого элемента ИЛИ соединен с выходом первого элемента И, выход второго элемента ИЛИ является выходом переноса в (i+ 1)-ый разряд, а -его входы соединены с выходами Первого элемента сложения по модулю два и выходом четвертого элемента И, выход третьего элемента сложения по модулю два является выходом результата данного разряда, отличающее ся тем, что с целью расширения области применения за счет реализации в устройстве операций десятичной арифметики, в каждый I-и разряд устройства введены элемент НЕ и пятый элемент И, а каждая тетрада разрядов устройства включает блок коррекции, причем в 1-м раэряде устройства второй вход первого элемента ИЛИ соединен с выходом пятого элемента И, первый вход которого соединен с выходом второго элемента сложения по моду.лю два, а второй вход - с выходом . второго элемента И и входом элемента НЕ, выход которого соединен с третьим входом четвертого элемента И, входы блока коррекции подключены к выходам результатов трех сташих разрядов тетрады устройства и выходу переноса из старшего разряда тетрады устройства соответственно, выход блока коррекции подключен к информационным входам второго и третьего разрядов тетрадыусггройства

2, Устройство по п. 1, о т л и чающее с я тем, что блок коррекции содержит триггер, элементы И и ИЛИ, входы первого элемента ИЛИ подключены к первому и второму входам блока соответственно, а выход соединен с первым входом элемента И второй вход которого соединен с третьим входом блока, выход элемента И соединен с первым входом второго элемента ИЛИ, второй вход которого подключен к четвертому входу блока, выход второго элемента ИЛИ соединен с единичным входом триггера, выход которого является выходом блока.

Источники информации, принятые во внимание при экспертизе

fPt/.2

Авторы

Даты

1982-09-30—Публикация

1980-06-16—Подача