(54) ПРЕОБРАЗОВАТЕЛЬ КОДА В ЧАСТОТУ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой термометр | 1987 |

|

SU1571427A1 |

| Многокоординатное устройство для управления | 1989 |

|

SU1777121A2 |

| Устройство для управления автономным инвертором | 1990 |

|

SU1810973A1 |

| Цифровой экстраполятор | 1983 |

|

SU1126970A1 |

| Устройство для синхронного радиоприема частотно-манипулированных сигналов | 1986 |

|

SU1363517A2 |

| Прибор для измерения частотных характеристик | 1986 |

|

SU1335935A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU961150A1 |

| Цифровой синтезатор частот | 1990 |

|

SU1748251A1 |

| Синтезатор частот | 1984 |

|

SU1293841A1 |

| Цифровой синтезатор частоты | 1986 |

|

SU1356222A1 |

Изобретение относится к тeлeмexal нике, измерительной и вычислительной технике и может быть использовано в системах обработки и передачи информации, а также в измерительной технике в качестве магазина частот.

Известен преобразователь кодчастота, содержащий управляемые делители частоты, регистр входного ко-да, элементы И и элемент ИЛИ tl.

Существенным недостатком этого преобразователя является то, что импульсы выходной частоты следуют неравномерно, а коду пропорциональна усредненная частота. Это существенно снижает область применения устройства.

Известен преобразователь кода в частоту,который содержит генератор опорной частоты, регистр входного кода, счетчик, клапаны и устройство для изменения частоты следования импульсов по закону квадратичной гиперболы C2J .

Введение в преобразователь такого сложного устройства, как устройство для изменения частоты следования импульсов, по закону квадратичной гиперболы снижает надежность работы преобразователя. Данное устрой-.

ство имеет свою погрешность в реализации функции квадратичной гиперболы, что сказывается на точности преобразования кода в частоту импульсов. того, выполнение устройства таким образом, что -код записывается за цикл измерения только один раз - по импульсу выходной частоты, приводит к тому, что при быст10рой вменяющемся коде выходная частота может существенно отличаться от средневзвешенного кода за цикл измерения.

При преобразовании малых значений

15 входного кода продолжительность цикла измерения существенно удлиняется, следовательно, быстродействие преобразователя уменьшается при уменьшении преобразуемого кода, а в случае

20 уменьшения входного кода до нуля преобразователь фактически прекращает свою работу.f

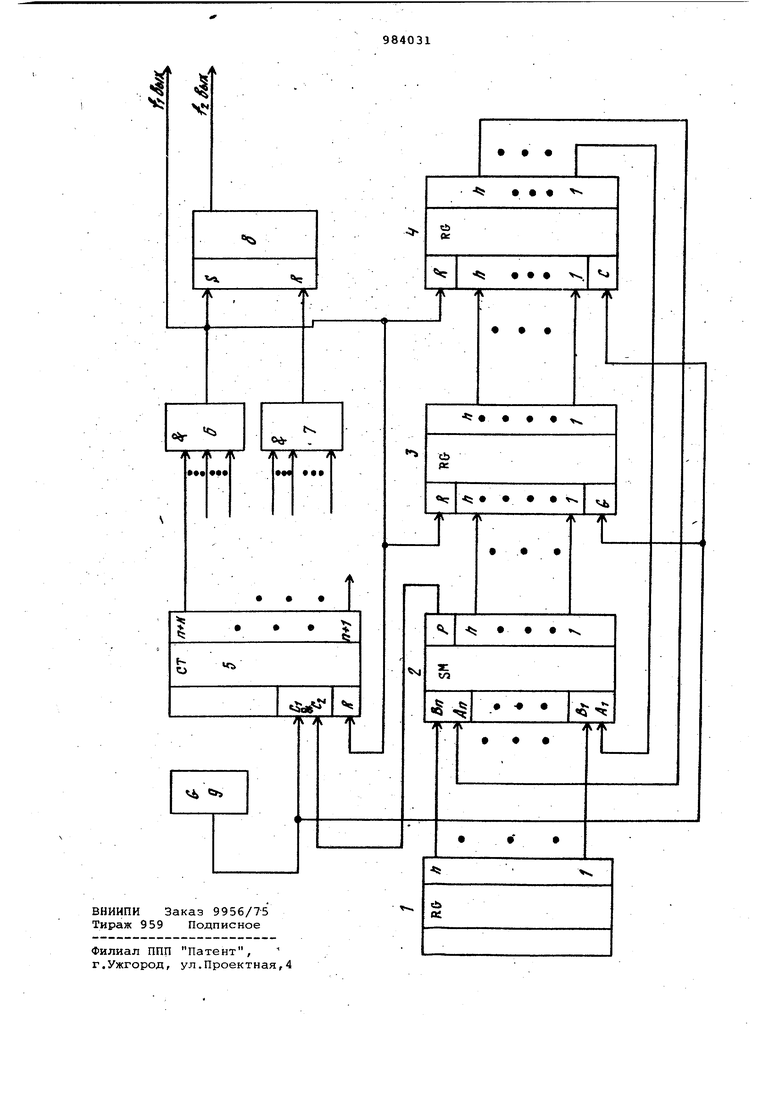

Указанные недостатки ограничивают, область применения этого преоб25разователя в системах обработки и передачи информации, особенно быстродействуюй х с широким диапазоном изменения входного кода, и в других устройствах телемеханики и вычисли30тельной техники. Цель изобретения - повышение точности и быстродействия, а также расширение функциональных возможностей, преобразования кода в частоту. Поставленная цель достигается тем, что Б преобразователь, содержащий генератор опорной частоты, регистр входного кода и счетчик импульсов, введены сумматор, два буферных регистра и первый элемент И, при этом выходы регистра входного кода поразрядно соединены с первыми входами сумматора, выходы разрядов которого соответственно подключены к входам первого буферного регистра выходы которого поразрядно соединены с входами второго буферного регистра выходы которого поразрядно подключены к вторыгл входам сумматора, выход переноса которого соединен со счетным входом счетчика импуль.сов, первая группа выходовкоторого соединена с входами первого элемента И, выход которого подключен к входам сброса счетчика импульсов и буферных регистров, а выход генератора опорной ча-стоты соединен с тактирующим входом счетчика импульсов и тактирующими входами буферных регистров. Кроме того, в преобразователь дополнительно введены второй элемент И и триггер, причем вторая, группа выходов счетчика импульсов соединена с входами второго элемента И, выход которого и выход первого элемента И соединены соответственно с первым и вторым входами уста«овки триггера. На чертеже представлена структурная схема преобразователя. Преобразователь включает регистр 1 входного кода, сумматор 2, буферные регистры 3 и 4, счетчик 5, элементы И б и 7, триггер 8 и генератор 9 опорной частоты. Выходные шины регистра 1 входног кода поразрядно подсоединены к входам сумматора 2, другие входы сумматора 2 также поразрядно подсоединены к входам буферного регистра 4, Выходы сумматора 2 соединены со вхо дами первого буферного регистра 3, а выходы последнего - .со входами бу ферного регистра 4, Выход переноса сумматора 2 соединен с тактируемым входом счетчика 5, а тактирующий вх счетчика 5,как и тактирующие входы регистров 3 и 4, подключены к выходу генератора 9 опорной частоты. Соответствующие выходы счетчика 5 поразрядно подключены к входам элемента И б, выход которого соединен со входами сброса счетчика 5 и буферных регистров 3 и 4, Кроме того, выход элемента И 6 подключен к одно му из установочных входов триггера 8, а другой установочный вход поспеднего соединен с выходом элемента И 7, входы которого соединены с выходами счетчика 5, Работает устройство следующим образом. Входной код NX, содержащийся в регистре 1, поразрядно суммируется в сумматоре 2 с кодом регистра 4 N,, Код NX + N с выхода сумматора 2 по одному сигналу с тактового генератора 9, например по положительному фронту импульса опорной частоты, записывается в регистр 3, а по другому сигналу, например по отрицательйому фронту импульса, записывается в регистр 4. При наличии сигнала переноса на выходе переноса сумматора 2 и сигнала с тактового енератора 9, например по положительному фронту опорной частоты, содержимое счетчика 5 увеличивается на единицу. Если учесть то, что сумма двух п-разрядных чисел не может иметь число разрядов больше, чем п+1, то содержимое счетчика 5 и регистра 3 (запись в регистр 3 и увеличение содержимого счетчика 5 при наличии сигнала на выходе разряда переноса сумматора 2 происходит одновременно) представляет собой К+п разрядную сумму (К - количество разрядов счетчика) содержимого счетчика N (К старших разрядов числа), входного кода и содержимого буферного регистра 4 N , В начальный момент времени содержимое регистров 3,4 и счетчика 5 равно О, Тогда код на выходе сумматора 2 равен N;, по переднему фронту И1 пульса в регистр 3 записывается Ny,a по отрицательному этот же код переписывается в регистр 4, и на выходе сумматора имеем число 2-N;, которое затем снова записывается в регистр 3, и при наличии разряда переноса содержимое счетчика 5 увеличивается на 1, После следующего цикла сложения импульса опорной частоты имеем З-NX и т.д. Таким образом, после К циклов сложения в счетчике 5 и регистре 3 имеем число N4 K-N, При появлении единиц на соответствующих входах счетчика 5, т,е, когда N/ становится равным числу NQ (с точностью до П+1-ГО разряда, причем при определении N учитывают, какие выходы счетчика 5 подключены к входу элемента И 6), на выходе элемента И б появляется импульс, который сбрасывает регистры 3, 4 и счетчик 5 в нуль, и все повторяется сначала. Таким образом, на выходе элемента И 6 импульс появляется тогда, когда N4 NO (с Теочностью до младшего разряда счетчика 5), т,е, NO , 2 N, где N - текущая сумма; KQ - количество циклов сложения при котором N4 NO (с точ ностью до младшего разряда счетчику); Т - время достижения равенства NO N4; t - период следования импульсо генератора 9 опорной частоты или преобразуя 1 fjr „ ГЙ T-f -N 1 X вы) xr где NO - уставка конечной суммы; Т - время достижения конечной суммы NO; fp - частота генератора опорной частоты; вых выходная .частота преобразо вателя; .А - коэффициент пропорциональности А й - входной код. Таким образом, на выходе элемент И 6 меем частоту, пропорционгшьную коду. Второй элемент И 7 и триггер 8 служат для расширения функциональны возможностей преобразователя, а име но для регулирования скважности импульсов. Действительно, при появлен сигнала на выходе первого элемента И б, т.е. когда N NQ, триггер устанавливается в единичное состояние, а остальная схема - в исходное состояние. При достижении суммой N значения NQ NQ , которое -определяется тем, какие разряды счетчик 5 подключены к входам элемента И 7, триггер 8 переводится в нулевое сос тояние .V Таким образом, задавая различные соотношения NQ и , можно изменять скважность выходной частоты в широком диапазоне. Оценим точность предложенного преобразователя. Допустим, K(jNy, NO(I), где . входной код,при котором выполняется тождество (1), а частота равна fg(3| A-N, но так как импульсы на выходе появляются тогда, когда NQ с точностью до младшего разряда счетчика, то частота f... будет соответствовать ьых и такому коду Мх1 + д,что Ko(N(+:д)N,-l.(tл (2) Преобразуя равенство (2), получаем, что абсолютная погрешность преобразователя и тем более т.е. погрешность тем бол ipe, чем больше входной код, и тем меньше чем больше NQ. Относительная погрешность определяется как Таким образом, выбирая No (исходя из максимально возможного N,,,c,x) t можно получить сколь угодно высокую точность преобразования. Более того, считая вес младшего разряда равным 1 и выбирая NO 1, где I jtidx максимально возможное значение входного кода, имеем Л 71-, Л 1 (Nxmax-) Таким образом, задаваясь NQ и f, можно получить требуемую точность преобразования и коэффициент проПОрциональности между входным кодом и выходной частотой. Так как входной код постоянно считывается с регистра входного кода, то выходная частота будет опр еделяться средневзвешенным входным кодом за период между двумя соседними импульсами входной частоты, что повышает точность и быстродействие преобразователя. Формула изобретения 1.Преобразователь кода в частоту, содержащий генератор опорной частоты, регистр входного кода и счетчик импульсов, отличающийся тем, что, с целью повышения точности и быстродействия преобразования, в него введены сумматор, два буферных регистра и первый элемент И, при этом выходы регистра входного кода поразрядно соединены с первыми входами сумматора, выходы разрядов которого соответственно подключены к входам первого буферного регистра, выходы которого поразрядно соединены с входами второго буферного регистра, выходы которого поразрядно подключены к вторым входам сумматора, выход переноса которого соединен со счетным входом счетчика импульсов, первая группа выходов которого соединена с входами первого элемента И, выход которого подключен к входам сброса счетчика имп.ульсов буферных регистров, а выход генератора опорной частоты соединён с тактирующим входом счетчика импульсов и тактирующими входами буферных регистров. 2.Преобразователь по п. 1, о тличающийс я тем, что, с

7 9840318

целью расширения функциональных воз-Источники информации,

можностей, в него введены второйпринятые во внимание при экспертизе элемент И и триггер, причем вторая

группа выходов счетчика импульсов1, Гутников B.C. Интегральная

соединена с входами второго элемен-электроника в измерительных устройта И, выход которого и выход первого 5 ствах. Л., 1980, с. 238-241.

элемента И соединены соответственно, 2. Авторское свидетельство СССР

с первым и вторые входами установки 494847, кл. Н 03 К 13/02,06.07.73

триггера,(прототип).

I

V:

v.

k I г

iГ

Its

e

A

r

«г

Ч;

Ч

JF

I t

vt

I

b W

n.

/I k V

%ч.

«м

V5

Авторы

Даты

1982-12-23—Публикация

1981-04-01—Подача