Изобретение относится к радиотехнике и может использоваться в системах фазовой автоподстройки частоты с малым уровнем частот, кратных частоте сравнения в выходном сигнале.

Цель изобретения - повышение быстродействия.

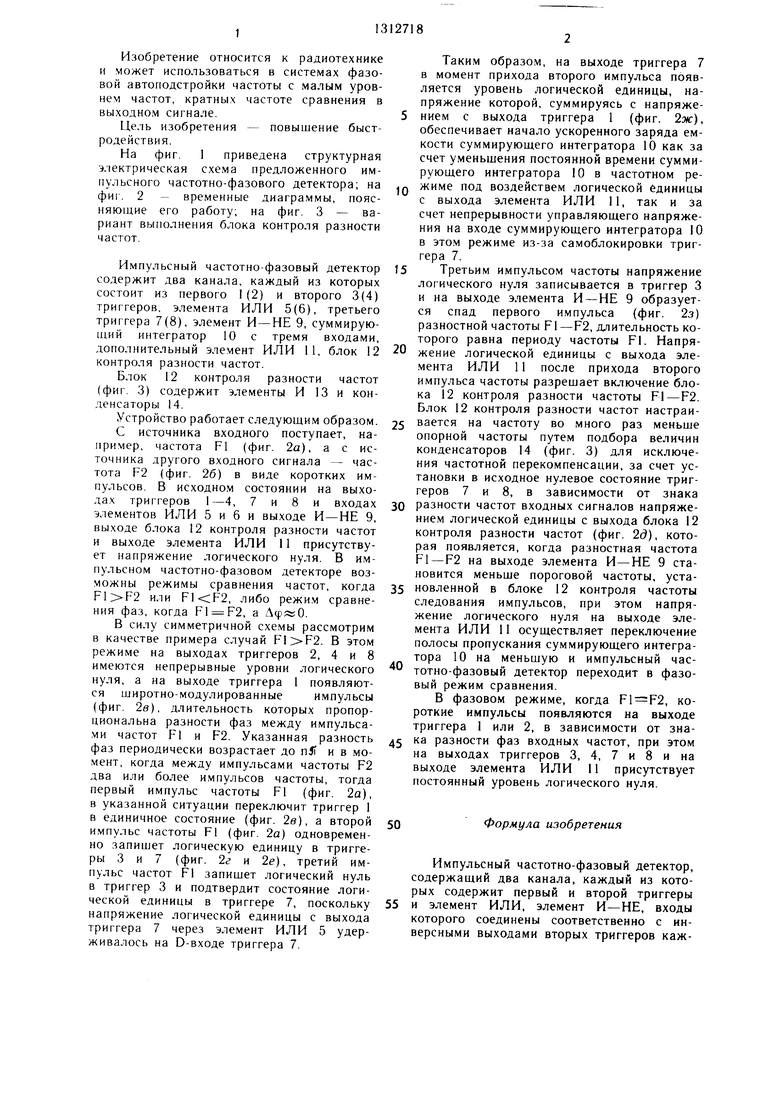

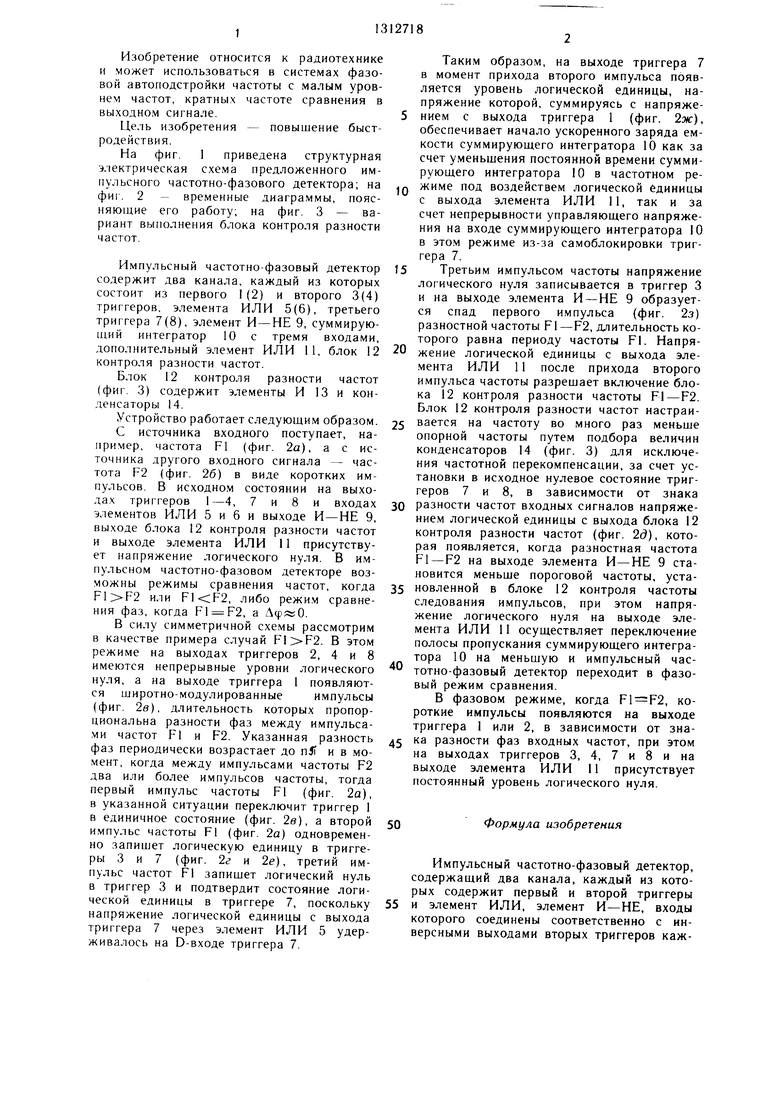

На фиг. 1 приведена структурная электрическая схема предложенного импульсного частотно-фазового детектора; на фиг. 2 - временные диаграммы, поясняющие его работу; на фиг. 3 - вариант выполнения блока контроля разности частот.

Импульсный частотно-фазовый детектор содержит два канала, каждый из которых состоит из первого 1 (2) и второго 3(4) триггеров, элемента ИЛИ 5(6), третьего триггера 7(8), элемент И - НЕ 9, суммирующий интегратор 10 с тремя входами, дополнительный элемент ИЛИ 11, блок 12 контроля разности частот.

Блок 12 контроля разности частот (фиг. 3) содержит элементы И 13 и конденсаторы 14.

Устройство работает следующим образом.

С источника входного поступает, например, частота F1 (фиг. 2а), а с источника другого входного сигнала - частота F2 (фиг. 26) в виде коротких импульсов. В исходном состоянии на выходах триггеров 1-4, 7 и 8 и входах элементов ИЛИ 5 и 6 и выходе И-НЕ 9, выходе блока 12 контроля разности частот и выходе элемента ИЛИ 11 присутствует напряжение логического нуля. В импульсном частотно-фазовом детекторе возможны режимы сравнения частот, когда или , либо режим сравнения фаз, когда , а .

В силу симметричной схемы рассмотрим в качестве примера случай . В этом режиме на выходах триггеров 2, 4 и 8 имеются непрерывные уровни логического нуля, а на выходе триггера I появляются широтно-модулированные импульсы (фиг. 2s), длительность которых пропорциональна разности фаз между импульсами частот F1 и F2. Указанная разность фаз периодически возрастает до n5i ив момент, когда между импульсами частоты F2 два или более импульсов частоты, тогда первый импульс частоты F1 (фиг. 2а), в указанной ситуации переключит триггер 1 в единичное состояние (фиг. 2в), а второй импульс частоты F1 (фиг. 2а) одновременно запищет логическую единицу в триггеры 3 и 7 (фиг. 2г и 2е), третий импульс частот F1 запищет логический нуль в триггер 3 и подтвердит состояние логической единицы в триггере 7, поскольку напряжение логической единицы с выхода триггера 7 через элемент ИЛИ 5 удерживалось на D-входе триггера 7.

Таким образом, на выходе триггера 7 в момент прихода второго импульса появляется уровень логической единицы, напряжение которой, суммируясь с напряже- нием с выхода триггера 1 (фиг. 2ж), обеспечивает начало ускоренного заряда емкости суммирующего интегратора 10 как за счет уменьшения постоянной времени суммирующего интегратора 10 в частотном ре0

жиме под воздеиствем логической единицы

с выхода элемента ИЛИ 11, так и за счет непрерывности управляющего напряжения на входе суммирующего интегратора 10 в этом режиме из-за самоблокировки триггера 7.

5 Третьим импульсом частоты напряжение логического нуля записывается в триггер 3 и на выходе элемента И - НЕ 9 образуется спад первого импульса (фиг. 2з) разностной частоты F1 -F2, длительность которого равна периоду частоты FI. Напря0 жение логической единицы с выхода элемента ИЛИ 11 после прихода второго импульса частоты разрещает включение блока 12 контроля разности частоты FI-F2. Блок 12 контроля разности частот настраи5 вается иа частоту во много раз меньще опорной частоты путем подбора величин конденсаторов 14 (фиг. 3) для исключения частотной перекомпенсации, за счет установки в исходное нулевое состояние триггеров 7 и 8, в зависимости от знака

0 разности частот входных сигналов напряжением логической единицы с выхода блока 12 контроля разности частот (фиг. 2д), которая появляется, когда разностная частота F1-F2 на выходе элемента И-НЕ 9 становится меньще пороговой частоты, уста5 новленной в блоке 12 контроля частоты следования импульсов, при этом напряжение логического нуля на выходе элемента ИЛИ 11 осуществляет переключение полосы пропускания суммирующего интегратора 10 на меньщую и импульсный час тотно-фазовый детектор переходит в фазовый режим сравнения.

В фазовом режиме, когда , короткие импульсы появляются на выходе триггера 1 или 2, в зависимости от зна5 ка разности фаз входных частот, при этом на выходах триггеров 3, 4, 7 и 8 и на выходе элемента ИЛИ 11 присутствует постоянный уровень логического нуля.

50

Формула изобретения

Импульсный частотно-фазовый детектор, содержащий два канала, каждый из которых содержит первый и второй триггеры и элемент ИЛИ, элемент И-НЕ, входы которого соединены соответственно с инверсными выходами вторых триггеров каждого канала, и суммирующий интегратор с тремя входами, первый и второй входы которого соединены соответственно с выходами элементов ИЛИ первого и второго каналов, причем входы синхронизации первых триггеров каждого канала являются входами импульсного частотно-фазового детектора и соединены с входами сброса первых триггеров противоположного канала, инверсные выходы первых триггеров каждого канала

их каналов дополнительный элемент ИЛИ и блок контроля разности частот, выход которого соединен с входами сброса третьих триггеров обоих каналов, первый вход сое- динен с выходом элемента И - НЕ, а второй вход соединен с третьим входом суммирующего интегратора с тремя входами с выходом дополнительного элемента ИЛИ, первый и второй входы которого соединены соответственно с прямыми выходами третьих

соединены D-входам и первых триггеров 0 триггеров первого и второго каналов, при

противоположного канала, а прямые выхо-этом в каждом канале входы синхронизады первых триггеров каждого канала сое-пии второго и третьего триггеров объедидинены с D-входом второго триггера и пер-нены и соединены с входом синхронизавым входом элемента ИЛИ этого же кана-ции первого триггера, прямой выход трела, отличающийся тем, что, с целью тьего триггера соединен с вторым входом

выщения быстродействия, в каждый каналэлемента ИЛИ, а выход элемента ИЛИ соевведен третий триггер и общие для обо-динен с D-входом третьего триггера.

их каналов дополнительный элемент ИЛИ и блок контроля разности частот, выход которого соединен с входами сброса третьих триггеров обоих каналов, первый вход сое- динен с выходом элемента И - НЕ, а второй вход соединен с третьим входом суммирующего интегратора с тремя входами с выходом дополнительного элемента ИЛИ, первый и второй входы которого соединены соот

| название | год | авторы | номер документа |

|---|---|---|---|

| Импульсный частотно-фазовый детектор | 1983 |

|

SU1124424A1 |

| Импульсный частотно-фазовый детектор | 1984 |

|

SU1221710A2 |

| Импульсный частотно-фазовый детектор | 1983 |

|

SU1285558A1 |

| Частотно-фазовый детектор | 1982 |

|

SU1095351A1 |

| Синтезатор частот | 1988 |

|

SU1584105A2 |

| Делитель частоты с переменным коэффициентом деления | 1985 |

|

SU1269255A1 |

| Частотно-фазовый детектор | 1984 |

|

SU1203685A1 |

| Импульсный частотно-фазовый детектор | 1983 |

|

SU1246334A1 |

| Импульсный частотно-фазовый детектор | 1989 |

|

SU1807550A1 |

| Формирователь разностной частоты импульсных последовательностей | 1984 |

|

SU1265985A1 |

Изобретение относится к радиотехнике. Цель изобретения - повышение быстродействия. Детектор содержит триггеры 1, 2, 3, 4, 7 и 8, эл-ты ИЛИ 5, 6 и 11. эл-т И - НЕ 9, суммирующий интегратор (СИ) И) с тремя входами и блок контроля pa.i- ности частот (БКРЧ) 12. Цель дости|-ает- ся введением триггеров 7 и 8, : л--1а ИЛИ 11 и БКРЧ 12, с помощью которых осуществляется переключение нолосы пропускания СИ 10 и перевод детектора из режима сравнения частот в режим сравнения фаз. 3 ил. S (Л Фиг.1

П . п

n ffifg

Фиг.З

Составитель И. Грабилин

Редактор А. ШандорТехред И. ВересКорректор С. Черни

Заказ 1849/55Тираж 902Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

I 13035, Москва, Ж-35, Раушская наб., д. 4/5 Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная. 4

12

т

К RfJ2;

(W

| Импульсный частотно-фазовый детектор | 1984 |

|

SU1221710A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-05-23—Публикация

1985-01-07—Подача