Изобретение относится к радиотехнике и может использоваться в системах фазовой автоподстройки частоты.

Цель изобретения - уменьшение уровня импульсных помех в выходном сигнале, а также повышение .быстродействия при упрощении устройства.

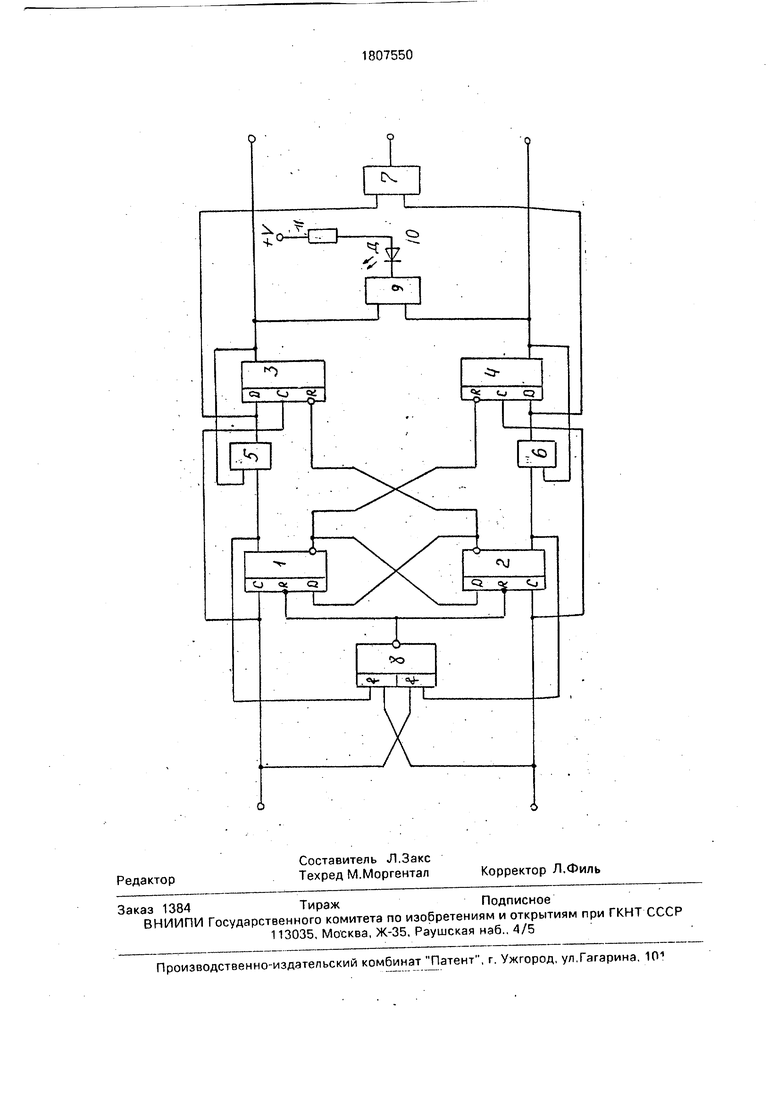

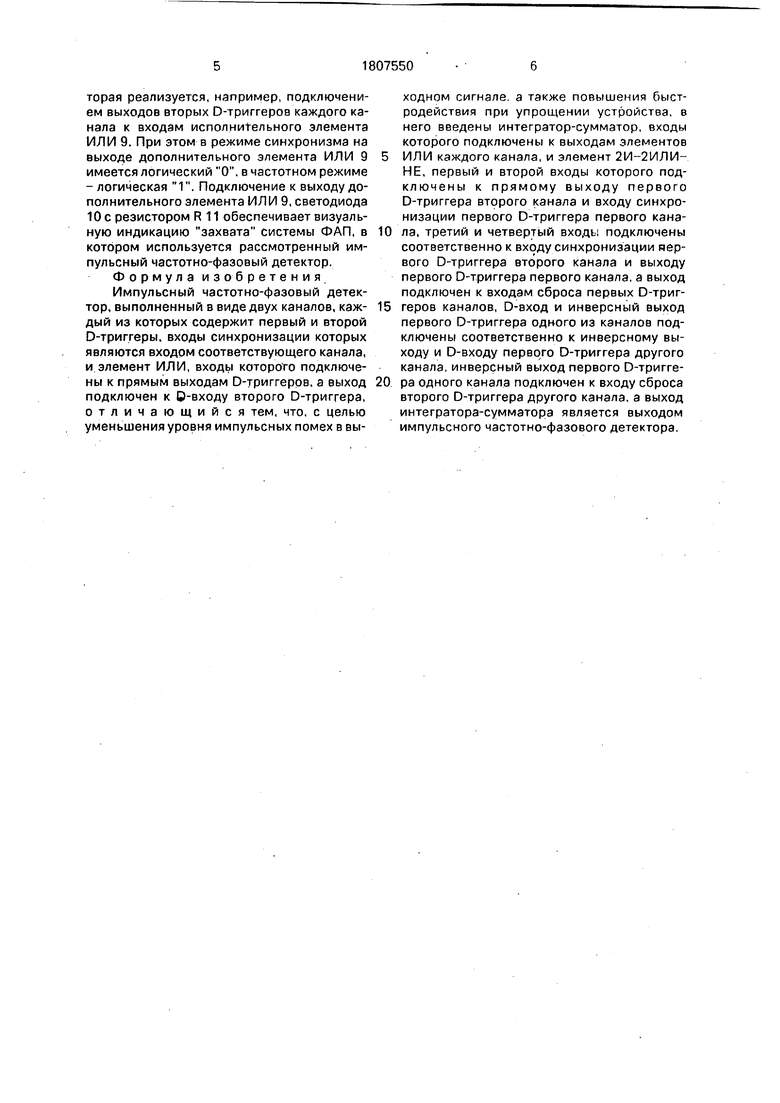

На чертеже представлена структурная электрическая схема детектора.

Импульсный частотно-фазовый детектор содержит первый и второй D-триггеры 1 и 3 первого канала, первый и второй D-триггеры 2 и 4 второго канала, элемент ИЛИ. 5 первого канала, элемент ИЛИ 6 второго канала, интегратор-сумматор 7 и элемент 2 И- 2 ИЛЙ-НЕ 8, а также дополнительный элемент ИЛИ 9, светодиод 10 и резистор 11.

Принцип работы устройства рассмотрим на примере его выполнения на микросхемах ТТЛ-серии.

Импульсный частотно-фазовый детектор (ИЧФД) работает следующим образом.

В исходном состоянии на прямых выходах всех D-триггеров уровни напряжений соответствуют логическому О. Пусть на С-. вход первого D-триггера 1 первого канала поступают импульсы опорной частоты FO, а на вход первого D-триггера 2 второго канала -импульсы контролируемой частоты FL При этим на указанные входы могут поступать импульсы как малой, так и большой (произвольной) длительности.

В ИЧФД возможны режимы сравнения частот, когда Fo Fi или FO FI, либо режим сравнения фаз, когда Fo Fi, но Д/ 0 или Ду. 0, где Д р -разность фаз между опорной и контролируемой частотами. Пусть Fo Fi и элемент 2И-2ИЛИ-НЕ 8 в работе не участвует, при этом на выходе первого D-триггера 2 второго канала формируются широтно-модулированные импульсы, длительность которых пропорциональна разности фаз между частотами FO и FI. Через определенное время (в худшем случае чепез время 1) Fo-Fi, когда Дуэ становится больше

ел

с

со

о VI ел ел о

2 п , между импульсами частоты FI появляются два импульса более высокой частоты. Первый импульс частоты FI в указанной ситуации переключает первый D-триггер 2 второго канала в состояние логической 1, а второй импульс частоты Fi записывает логическую Г из первого D-триггера 2 второго канала в второй D-триггер 4.

Каждым последующим импульсом частоты FI состояние второго D-триггера 4 второго канала подтверждается, поскольку логическая 1 с его прямого выхода через элемент ИЛ И 6 поступает на D-вход второго D-триггера 4 второго канала. Таким образом, на выходе второго D-триггера 4 второго канала фиксируется постоянный уровень логической 1, означающий отрицательный знак частотной расстройки: Fp-Fi 0. Одновременно напряжение логической 1 с выхода элемента ИЛИ 6 второго канала в виде постоянного уровня поступает на вход интегратора-сумматора 7, при этом напряжение на выходе интегратора-сумматора 7 увеличивается с максимальной скоростью, уменьшая тем самым частотную расстройку на входах ИЧФД до момента изменения знака разности фаз частот Fo и FI, После изменения знака разности фаз частот Fo и FI импульсы частотой Fo начинают опережать по фазе импульсы частоты FL В результате первый же опережающий импульс частоты FO переключает первый D-триггер 1 первого канала в единичное состояние, а первый D-триггер 4 второго канала по входу сброса сбрасывается в О напряжением с инверсного выхода первого Ь-триггера 1 первого канала. Таким образом, второй D- триггер .4 второго канала при ) 2 л: от-, ключаётся и на выходах D-триггеров З и 4 фиксируются уровни логического О, означающие режим фазового сравнения входных частот, В этом режиме на выходе элемента ИЛ И 6 второго канала наблюдаются импульсы длительностью, пропорциональной фазовому рассогласованию входных частот Fo и FL На выходе интегратора-сумматора 7 происходит увеличение напряжения, пропорциональное длительности импульсов, поступающих на вход интет- ратора-суммэтрра 7, уменьшающее рассогласование фаз входных сигналов. При нулевом сдвиге фаз между входными сигналами на выходах элементов ИЛИ 5 первого канала и ИЛИ 6 второго канала импульсы отсутствуют, удерживая интегратор- сумматор.7 в закрытом состоянии.

В силу, симметричности схемы ИЧФД его работа в случае Fo FI аналогична работе при Fo FI, с той лишь разницей, что в

состояние логической 1 переключается второй D-триггер З первого канала, напряжение с которого через элемент ИЛИ 5 первого канала воздействует на интегратор-сумматор 7, уменьшая напряжение на его выходе с максимальной скоростью до момента изменения знака фазового рассогласования, при этом второй D-триггер З первого канала сбрасывается в нулевое

0 состояние после переключения первого D- триггера 2 второго канала в единичное состояние первым же импульсом частоты FI после указанной ситуации. Далее наступает режим сравнения фаз входных частот, при

5 котором на выходе первого D-триггера 1 первого канала формируются импульсы длительностью, пропорциональной величине фазового рассогласования частот FO и Fa, FL Наличие же элемента 2И-.2ИЛИ-НЕ 8

0 позволяет работать с входными импульсными сигналами большей длительности. При этом алгоритм работы D-триггеров 1 и 2 несколько отличен. Так, в случае опережения по фазе сигнала частоты FO относительт

5 но сигнала частоты FI первым импульсом по положительному фронту первый D-триггер 1 первого канала взводится в единичное со- о стояние. Логическая 1 с выхода первого D-триггера 1 первого канала поступает на

0 первый вход логического элемента 2И- 2ИЛИ-НЕ 8 (при этом до прихода входных импульсов на выходе элемента 2И-2ИЛИ- НЕ 8 имеется логическая 1), с инверсного же выхода первого D-триггера 1 логический

5 О, поступая на D-вход второго D-триггера 2 второго канала, блокирует его переключение в единичное состояние. Логическая 1, поступающая с прямого выхода первого D- триггера 1 на первый вход элемента 2И0 2ИЛИ-НЕ 8, разрешает тем самым прохождение входного импульса на сбросовые входы D-триггеров 1 и 2. Поэтому в момент прихода импульса FI на выходе элемента 2И-2ИЛИ-НЕ 8 появляется импульс,

5 который сбрасывает первый D-триггер 1 . первого канала. При этом длительность импульса сброса определяется временем задержки элементов 2И.-2ИЛИ-НЕ. 8 и временем переключения D-триггера и поэ0 тому не зависит от длительности импульсов входного сигнала, позволяя тем самым работать с импульсами большей длительности. Поскольку в устройстве взводится лишь один из D-триггеров, формирующий инфор5 мационный сигнал, импульсные помехи во входном сигнале отсутствуют.

К дополнительным преимуществам следует отнести возможность надежной инди- кации режима синхронизма (захват системы фазовой автоподстройки частоты (ФАН). которая реализуется, например, подключением выходов вторых D-триггеров каждого канала к входам исполнительного элемента ИЛИ 9. При этом в режиме синхронизма на выходе дополнительного элемента ИЛИ 9 имеется логический О, в частотном режиме - логическая 1. Подключение к выходу дополнительного элемента ИЛИ 9, светодиода 10с резистором R 11 обеспечивает визуальную индикацию захвата системы ФАП, в котором используется рассмотренный импульсный частотно-фазовый детектор. Формула изобретения Импульсный частотно-фазовый детектор, выполненный в виде двух каналов, каждый из которых содержит первый и второй D-триггеры. входы синхронизации которых являются входом соответствующего канала, и элемент ИЛИ, входы которого подключены к прямым выходам D-триггеррв, а выход подключен к 0-входу второго D-триггера, отличающийся тем, что, с целью уменьшения уровня импульсных помех в выходном сигнале, а также повышения быстродействия при упрощении устройства, в него введены интегратор-сумматор, входы которого подключены к выходам элементов ИЛИ каждого канала, и элемент 2И-2ИЛИ- НЕ, первый и второй входы которого подключены к прямому выходу первого D-триггера второго канала и входу синхронизации первого D-триггера первого кана0 ла, третий и четвертый входы подключены соответственно к входу синхронизации первого D-триггера второго канала и выходу первого D-триггера первого канала, а выход подключен к входам сброса первых D-триг5 геров каналов, D-вход и инверсный выход первого D-триггера одного из каналов подключены соответственно к инверсному выходу и D-входу первого D-триггера другого канала, инверсный выход первого D-тригге0 ра одного канала подключен к входу сброса второго D-триггера другого канала, а выход интегратора-сумматора является выходом импульсного частотно-фазового детектора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Импульсный частотно-фазовый детектор | 1983 |

|

SU1246334A1 |

| Импульсный частотно-фазовый детектор | 1983 |

|

SU1285558A1 |

| Импульсный частотно-фазовый детектор | 1983 |

|

SU1124424A1 |

| Импульсный частотно-фазовый детектор | 1982 |

|

SU1059662A1 |

| Частотно-фазовый детектор | 1984 |

|

SU1203685A1 |

| Импульсный частотно-фазовый детектор | 1984 |

|

SU1221710A2 |

| ИМПУЛЬСНЫЙ ЧАСТОТНО-ФАЗОВЫЙ ДЕТЕКТОР | 1991 |

|

RU2012992C1 |

| Импульсный частотно-фазовый детектор | 1986 |

|

SU1424114A2 |

| Импульсный частотно-фазовый детектор | 1980 |

|

SU985929A1 |

| Устройство для измерения сдвига фаз | 1988 |

|

SU1672382A1 |

Использование: радиотехника системы фазовой автоподстройки частоты. Сущность изобретения; импульсный частотно-фазовый детектор содержит первый и второй D- триггеры первого канала, первый и второй D-триггеры второго канала, элементы ИЛИ и первого и второго каналов соответственно, интегратор-сумматор, элемент 2И- 2ИЛИ-НЕ, а также дополнительный элемент ИЛИ, светодиод и регистр. В устройстве уменьшается уровень импульсных помех в выходном сигнале, поскольку выводится лишь один из D-триггеров, формирующий информационный сигнал, кроме того, небольшое число элементов позволяет повысить быстродействие. 1 ил.

| Патент США № 4764737, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1993-04-07—Публикация

1989-11-09—Подача