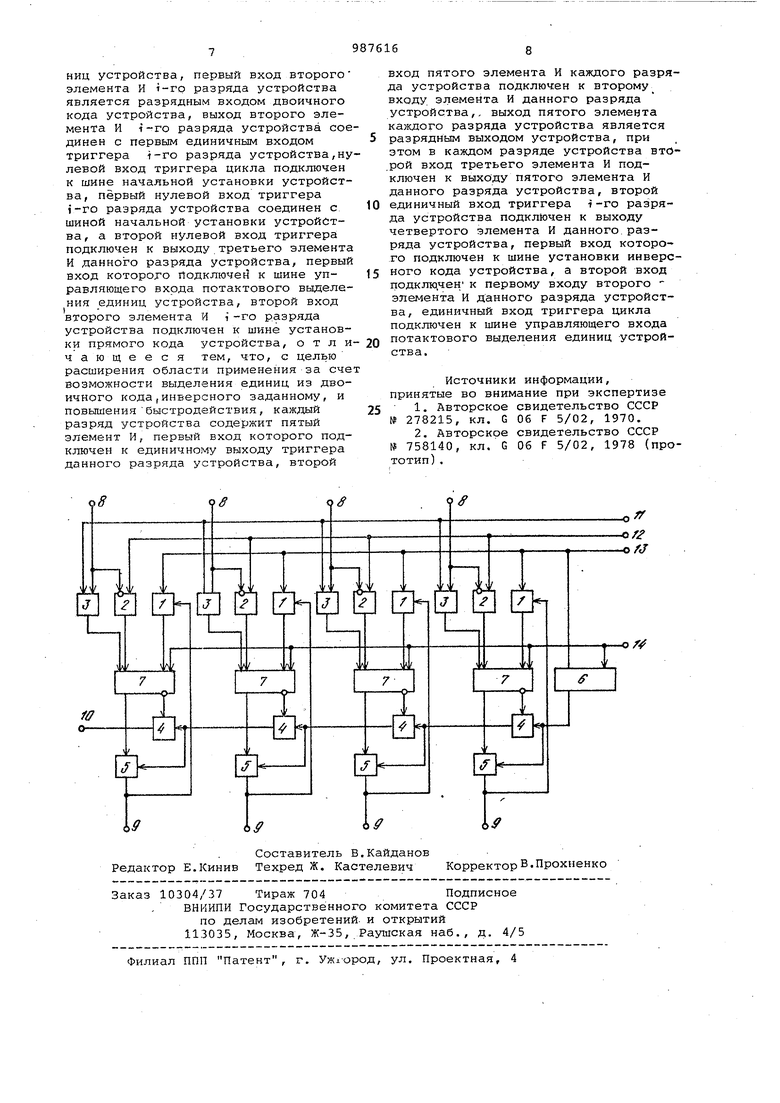

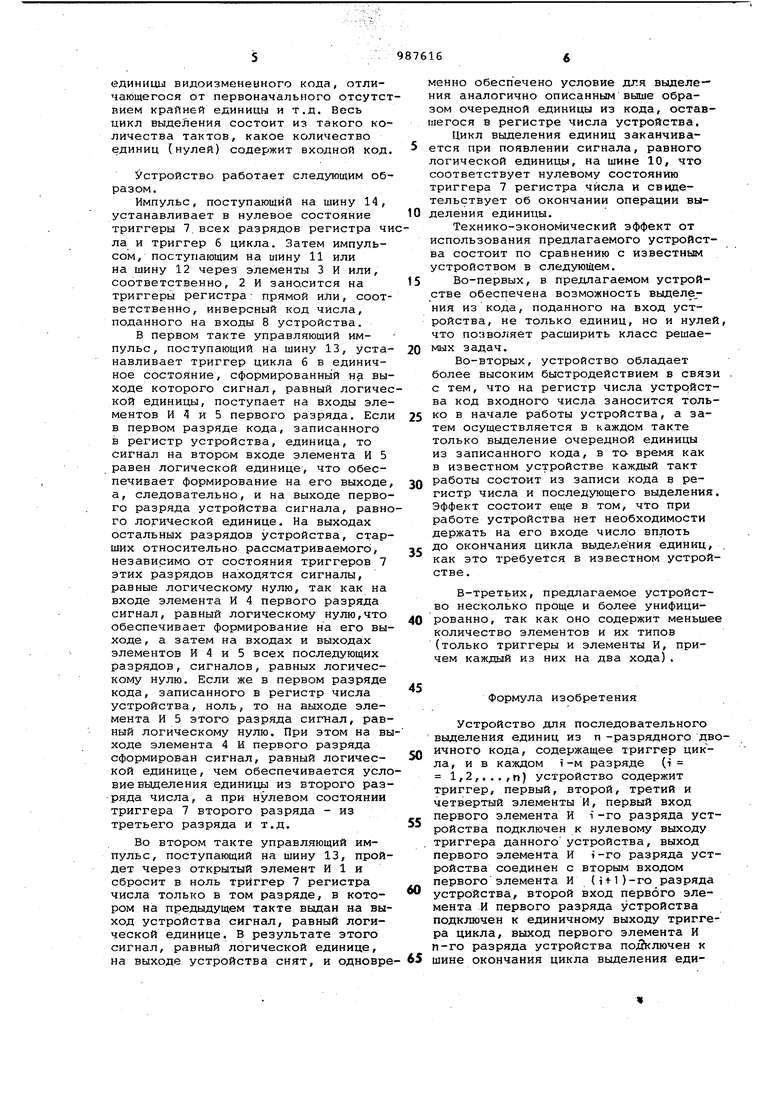

вым входом триггера данного разряда второй вход которого соединен с выходом третьего элемента И данного разряда, второй выход триггера каждо го разряда подключен к первому входу четвертого элемента И,, второй вход которого для j-го разряда соединен с выходом четвертого элемента И (j-l)-ro разряда и со входом элементаНЕ,первый выход триггера является разрядным выходом числа устройства,вы ходчетвертого элемента п-горазряда устройства является выходом окончания цикла выделения единиц, второй выход триггера цикла подключен ко второму входу четвертого элемента И первого разряда устройства 21. Недостатком известного устройства является то, что оно не обеспечивает выделение единиц из кода инверсного поданному на вход устройства, а также то, что оно обладает недостаточно высоким быстродействием, поскольку каждый такт выделения очередной единицы состоит из двух этапов , на первом из которых осуществляется занесение соответствующих еди ничных разрядов в триггеры устройства, а на втором сброс всех разрядов за исключением разряда, содержащего правую крайнюю единицу. Цель изобретения - расширение области применения за счет возможнос ти выделения единиц из двоичного числа инверсного заданному и повышение быстродействия. Поставленная цель достигается тем что в устройстве для последовательного выделения единиц из п -разрядного двоичного кода, содержащем-триг гер цикла, и в кг1ждом i-м разряде ( i 1,2,...,п) устройство содержит триггер, первый, второй, третий,четвертый элементы И, первый вход первого элемента И 1-го разряда устрой ства подключен к нулевому выходу -триггера данного разряда устройства выход первого элемента И i-го разряда устройства соединен с вторым входом первого элемента И (i + 1)-ro разряда устройства, второй вход первого элемента И. первого разряда устройства подключен к. единичному выход триггера цикла, выход первого элемента И п-го разряда устройства под ключен к шине окончания цикла выделе ния единиц устройства, первый вход второго элемента И i-го разряда уст ройства является разрядным входом двоичного кода устройства, выход второго элемента И i-го разряда уст ройства соединен с первым единичным входом триггера i-ro разряда устрой ства , нулевой вход триггера цикла подключен к шине начальной установки устройства, первый нулевой вход триггера i-го разряда устройства соединен с 1г1иной начальной установки устройства, а второй нулевой вход триггера подключен к выходу третьего элемента И данного разряда устройства, первыЧ вход которого подклк чен к шине управляющего входа потактового выделения единиц устройства, второй вход второго элемента И ; -го разряда устройства подключен к шине установки прямого кода устройства, каждый разряд устройства содержит пятый элемент И,первый вход которого подключен к единичному выходу триггера данного разряда устройства,второй вход пятого элемента И каждого разряда устройства подключен к второму входу первого элемента И данного разряда устройства, выход пятого элемента каждого разряда устройства является разрядным выходом устройства, при этом в каждом разряде устройства второй вход третьего элемента И подключен к выходу пятого элемента И данного разряда устройства, второй единичный вход триггера i-го разряда устройства подключен к выходу четвертого элемента И данного разряда устройства, первый вход которого подключен к шине установки инверсного кода устройства, а второй вход подключен к первому входу второго элемента И данного разряда устройства, единичный вход триггера цикла подключен к шине управляЕОщего входа потактового выделения единиц устройства. На чертеже представлена структурная схема устройства на 4 разряда (увеличение количества разрядов осуществляется добавлением элементов, включенных аналогично предыдущим разрядам) . Устройство содержит элементы И 1,2,3,4 и 5, триггер 6 цикла, триггеры 7 регистра -числа, входы 8 числа, выходные шины 9 числа, шину 10 окончания цикла выделения единиц, шину 11 установки прямого кода, шину 12 установки инверсного кода, управляющую шину 13 потактового выделения единиц, шину 14 .начальной установки. Работа устройства начинается с занесения кода на регистр числа устройства. Поданное на вход устройства число может быть занесено на регистр числа либо в прямом коде, либо в инверсном, поэтому в процессе дальнейшей работы на выходе устройства формируются кодл, содержащие только по одному единичному разряду, который соответствует либо выделенной единицы, либо выделенному нулю из кода поданному на вход. Цикл выделения делится на такты. В первом такте происходит выделение крайней правой единицы из кода, записанного в регистр числа. В следующем такте происходит сброс разряда с выделенной единицей и выделение следующей крайней правой единицы видоизмененного кода, отличающегося от первоначального отсутст вием крайней единицы и т.д. Весь цикл выделения состоит из такого количества тактов, какое количество единиц (нулей) содержит входной код Устройство работает следующим образом. Импульс, поступающий на шину 14, устанавливает в нулевое состояние триггеры 7. всех разрядов регистра чи ла и триггер б цикла. Затем импульсом, поступающим на шину 11 или на шину 12 через элементы 3 И или, соответственно, 2 И заносится на триггеры регистра: прямой или, соответственно, инверсный код числа, поданного на входы 8 устройства. В первом такте управляющий импульс, поступающий на шину 13, устанавливает триггер цикла 6 в единичное состояние, сформированный на выходе которого сигнал, равный логичес кой единицы, поступает на входы элементов И и 5 первого разряда. Если в первом разряде кода, записанного в регистр устройства, единица, то сигнал на втором входе элемента И 5 равен логической единице, что обеспечивает формирование на его выходе а, следовательно, и на выходе первого разряда устройства сигнала, равно го логической единице. На выходах остальных разрядов устройства, старших относительно рассматриваемого, независимо от состояния триггеров 7 этих разрядов находятся сигналы, равные логическому нулю, так как на входе элемента И 4 первого разряда сигнал, равный логическому нулю,что обеспечивает формирование на его выходе, а затем на входах и выходах элементов И 4 и 5 всех последующих разрядов, сигналов, равных логическому нулю. Если же в первом разряде кода, записанного в регистр числа устройства, ноль, то на выходе элемента И 5 этого разряда сигнал, равный логическому нулю. При этом на вы ходе элемента 4 И первого разряда сформирован сигнал, равный логической единице, чем обеспечивается усло вие выделения единицы из второго разряда числа, а при нулевом состоянии триггера 7 второго разряда - из третьего разряда и т.д. Во втором такте управляющий импульс, поступающий на шину 13, пройдет через открытый элемент И 1 и сбросит в ноль триггер 7 регистра числа только в том разряде, в котором на предыдущем такте выдан на выход устройства сигнал, равный логической единице. В результате этого сигнал, равный логической единице, на выходе устройства снят, и одновре енно обеспечено условие для выделеия аналогично описанным выше образом очередной единицы из кода, оставегося в регистре числа устройства. Цикл выделения единиц заканчивается при появлении сигнала, равного огической единицы, на шине 10, что соответствует нулевому состоянию триггера 7 регистра числа и свидетельствует об окончании операции выделения единицы. Технико-экономический эффект от использования предлагаемого устройства состоит по сравнению с известным устройством в следующем. Во-первых, в предлагаемом устройстве обеспечена возможность выделе,ния из кода, поданного на вход устройства, не только единиц, но и нулей, что позволяет расширить класс решаемых задач. Во-вторых, устройство обладает более высоким быстродействием в связи с тем, что на регистр числа устройства код входного числа заносится только в начале работы устройства, а затем осуществляется в каждом такте только выделение очередной единицы из записанного кода, в то- время как в известном устройстве каждый такт работы состоит из записи кода в регистр числа и последующего выделения. Эффект состоит еще в том, что при работе устройства нет необходимости держать на его входе число вплоть до окончания цикла выделения единиц, . как это требуется в известном устройстве. В-третьих, предлагаемое устройство несколько проще и более унифицированно, так как оно содержит меньшее количество элементов и их типов (только триггеры и элементы И, причем каждый из них на два хода). Формула изобретения Устройство для последовательного выделения единиц из п-разрядного двоичного кода, содержащее триггер цикла, и в каждом 1-м разряде (i 1,2,...,п) устройство содержит триггер, первый, второй, третий и четвертый элементы И, первый вход первого элемента И i-го разряда устройства подключен к нулевому выходу триггера данного устройства, выход первого элемента И t-го разряда устройства соединен с ВТОРЕЛМ входом первогоэлемента И (iti)-го разряда устройства, второй вход первого элемента И первого разряда устройства подключен к единичному выходу триггера цикла, выход первого элемента И п-го разряда устройства пойслючен к шине окончания цикла выделения единиц устройства, первый вход второго элемента И i-ro разряда устройства является разрядным входом двоичного кода устройства, выход второго элемента И i-ro разряда устройства соединен с первым единичным входом триггера i-ro разряда устройства,нулевой вход триггера цикла подключен к шине начальной установки устройства, первый нулевой вход триггера i-ro разряда устройства соединен с шиной начальной установки устройства , а второй нулевой вход триггера подключен к выходу третьего элемента И данного разряда устройства, первый вход которого Подключен к шине управляющего входа потактового выделения единиц устройства, второй вход второго элемента И i-го разряда устройства подключен к шине установки прямого кода устройства, о т л и чающееся тем, что, с целью расширения области применения за сче возможности выделения единиц из двоичного кода(Инверсного заданному, и повышениябыстродействия, каждый разряд устройства содержит пятый элемент И, первый вход которого подключен к единичному выходу триггера данного разряда устройства, второй

вход пятого элемента И каждого разряда устройства подключен к второму входу элемента И данного разряда устройства,, выход пятого элемента каждого разряда устройства является разрядным выходом устройства, при этом в каждом разряде устройства вто.рой вход третьего элемента И подключен к выходу пятого элемента И данного разряда устройства, второй единичный вход триггера i-ro разряда устройства подключен к выходу четвертого элемента И данного разряда устройства, первый вход которого подключен к шине установки инверсного кода устройства, а второй вход подклю.чен к первому входу второго элемента И данного разряда устройства, единичный вход триггера цикла подключен к шине управляющего входа потактового выделения единиц устройства.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР P 278215, кл. G 06 F 5/02, 1970.

2.Авторское свидетельство СССР

№ 758140, кл. G Об F 5/02, 1978 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметико-логическое устройство | 1983 |

|

SU1176321A1 |

| Устройство для сравнительного анализа п чисел | 1978 |

|

SU736090A1 |

| Устройство для деления чисел | 1980 |

|

SU907544A1 |

| Устройство для деления чисел | 1981 |

|

SU970356A1 |

| Аналого-цифровой преобразователь в кодах с естественной избыточностью | 1986 |

|

SU1381698A1 |

| Пороговое устройство (его варианты) | 1984 |

|

SU1352449A1 |

| Устройство для исследования графов | 1985 |

|

SU1290345A1 |

| Устройство для одновременного выполнения операций сложения над множеством чисел | 1975 |

|

SU558276A1 |

| Последовательное множительное устройство | 1981 |

|

SU1067500A1 |

| Устройство для контроля логических блоков | 1988 |

|

SU1553980A1 |

Авторы

Даты

1983-01-07—Публикация

1981-08-07—Подача