Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах, в блоках контроля и обработки информации. Известно устройство для умножения содержащее регистры множителя и множимого, блок модульного умножения, сумматор, формирователи поправок, блоки вычитания, блоки деления и фор мирователи преобразованньзх множителя и гшожимого tl 3. Недостатками этого устройства для умножения являются его сложность и низкое быстродействие. Известно также устройство для умножения, содержащее два счетчика, две группы элементов И-НЕ, синхронизатор .импульсов, два триггера и сумматор-вычислитель С2 3. Недостатками этого устройства для умножения также являются его сложность и низкое быстродействие. Наиболее близким к предлагаемому является устройство для ундаожения, содержащее регистры первого и второго чисел, группу элементов. И, накапливающий сумматор и четыре схемы согласования фаз, в которых для синх ронизации периодов умножения хранятся коды поразрядной суммы и поразрядного переноса частичного произведения, причем входы управления схем согласования фаз соединены с шинами пере- . носа, сдвига и выдачи Сз. Недостатком этого устройства является его низкое быстродействие. Цель изобретения - повышение быстродействия. Указанная цель достигается тем, что в устройство для умножения, содержащее накапливающий сумматор, группу элементов И, регистры первого и второго чисел, информационные входы которых подключены соответственно к первому и второму информационным входам устройства, управляющий вход которого соединен с входами управления регистров первого и второго чисел, введены блок приоритета, группа дополнительных элементов И, формирователь -импульсов опроса, элемент И и элемент ИЛИ, при этом выходы разрядов накапливающего сумматора подключены соответственно к первым входам элементов И группы, выходы которых соответственно подклачены к выходам устройства, управляющий вход которого подключен к одному из входов элемента ИЛИ и входу обнуления накапливающего сумматора, информационные входы которого соединены соответственно с выходами блока приоритета и первьтми входами дополнительных элементов И группы, выходы которых соединены соответственно с обнуляющими входами разрядов регистра первого числа, выходы разрядов которого соединены соответственно с входами блока приоритета и входами элемента И, выход которого соединен с вторыми входами, элементов И группы и другим входом элемента ИЛИ, остальные входы которого подключены к выходам дополнительных элементов И группы, информационные входы формирователя импульсов опроса подключены соответственно к выходам разрядов регистра второго числа, а управляю-щий вход - к выходу элемента ИЛИ, причем формирователь импульсов опроса содерн(ит регистр, три группы элементов И, элемент И, элемент ИЛИ, элемент НЕ, вход которого соединен с управляющим входом формирователя импульсов опроса и первыми входами элементов И первой группы формирователя импульсов опроса, выход элемента НЕ соединен с пepвы ш входами первых элементов И второй и третьей групп формирователя импульсов опроса, выходы элементов,И первой и второй групп формирователя импульсов опроса соединены с прямым и инверсным входами соответствующих разрядов регистра формирователя импульсов опроса, инверсные выходы разрядов которого соединены с входами элемента И формирователя импульсов опроса, выходы элементов И третьей группы формирователя импульсов.опроса соединены соответственно с первыми входами элементов И второй группы, начиная с второго, формирователя импульсов опроса, первый вход каждого элемента И третьей группы, начиная с второго, соединен ствыходом предыдущего элемента И Третьей группы формирователя импульсов опроса, вторые входы элементов И третьей группы формирователя импульсов опроса соединены с инверсными вEJkoдaми соответствующих разрядов регистра формирователя импульсов опроса, вторые входы элементов И второй группы формирователя импульсов опроса соединены с прямыми выходами соответствующих разрядов регистра формирователя импульсов опроса, а выходы подключены к входам элемента ИЛИ формирователя импульсов опроса, вторые входы элементов И первой группы формирователя импульсов опроса соединены с соответствующими информационными входами формирователя импульсов опроса, выход элемента И и элемента ИЛИ формирователя импульсов опроса, являющиеся

соответственно первым и вторым выходами формирователя импульсов опроса, соединены соответственно с вторыми входами дополнительных элементов И группы и управляющим входом накапливающего сумматора, каждый разряд которого содержит счетный триггер и коммутатор, информационные входы которого соединены с выходом счетного триггера предыдущего разряда и управляющим вх&дом накапливающегосумматора, управляющий вход коммутатора соединен с соответствующим информационным входом накапливающего сумматора, а вьаход - с входом счетного триггера, вход обнуления которого соединен 6 входом обнуления накапливающего сумматора, а выход - с выходом соответствующего разряда накапливающего сумматора.

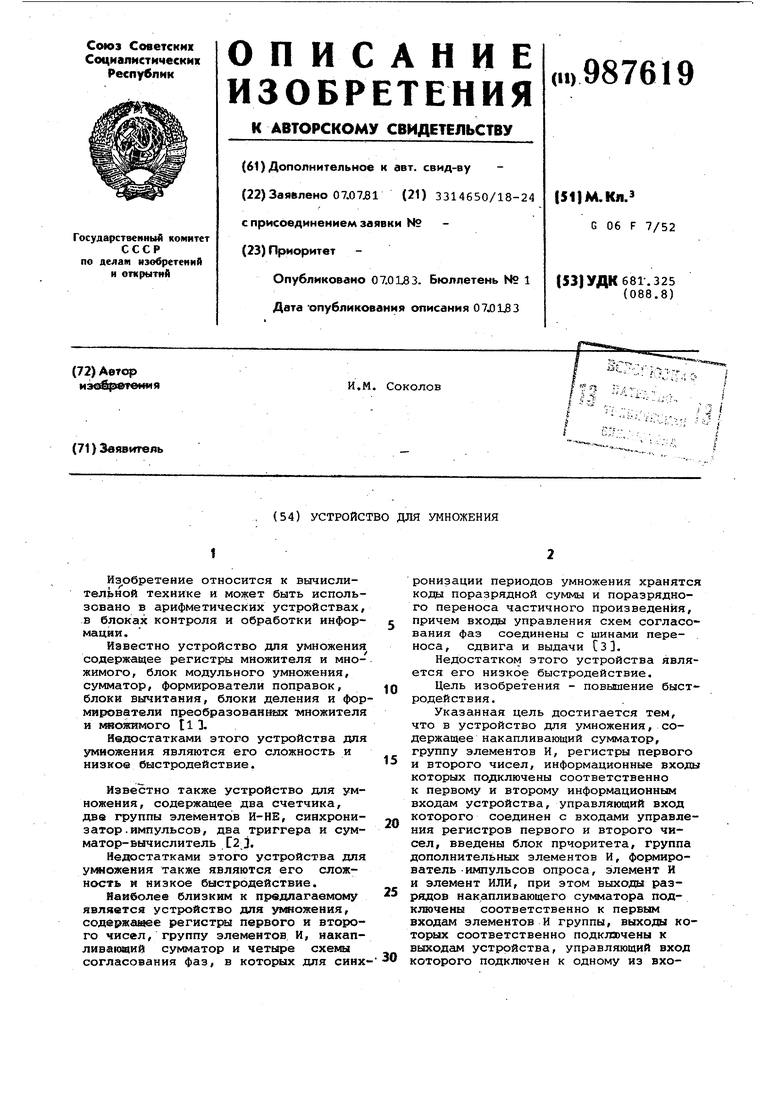

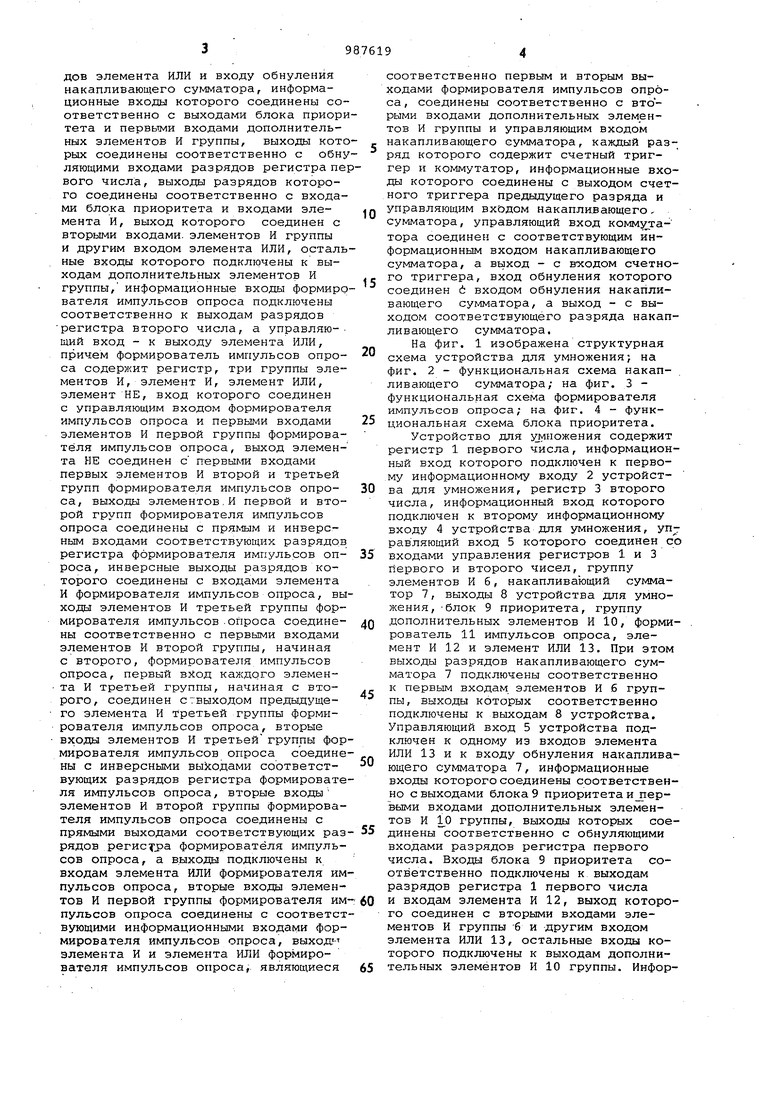

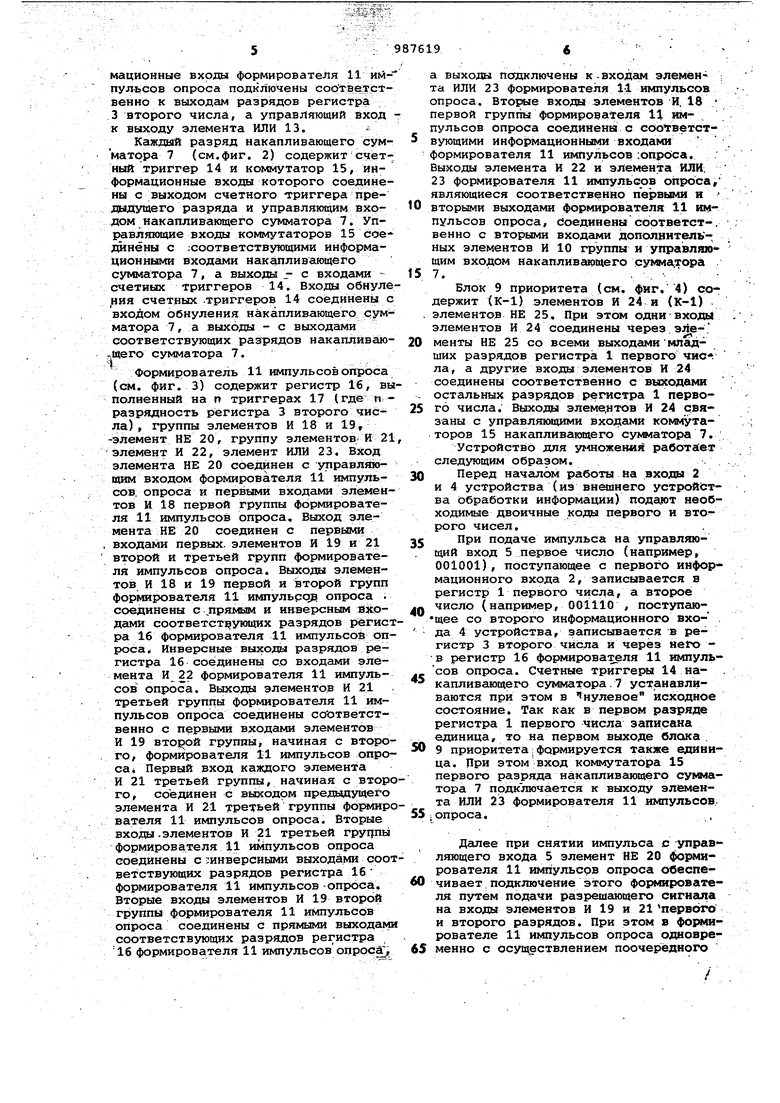

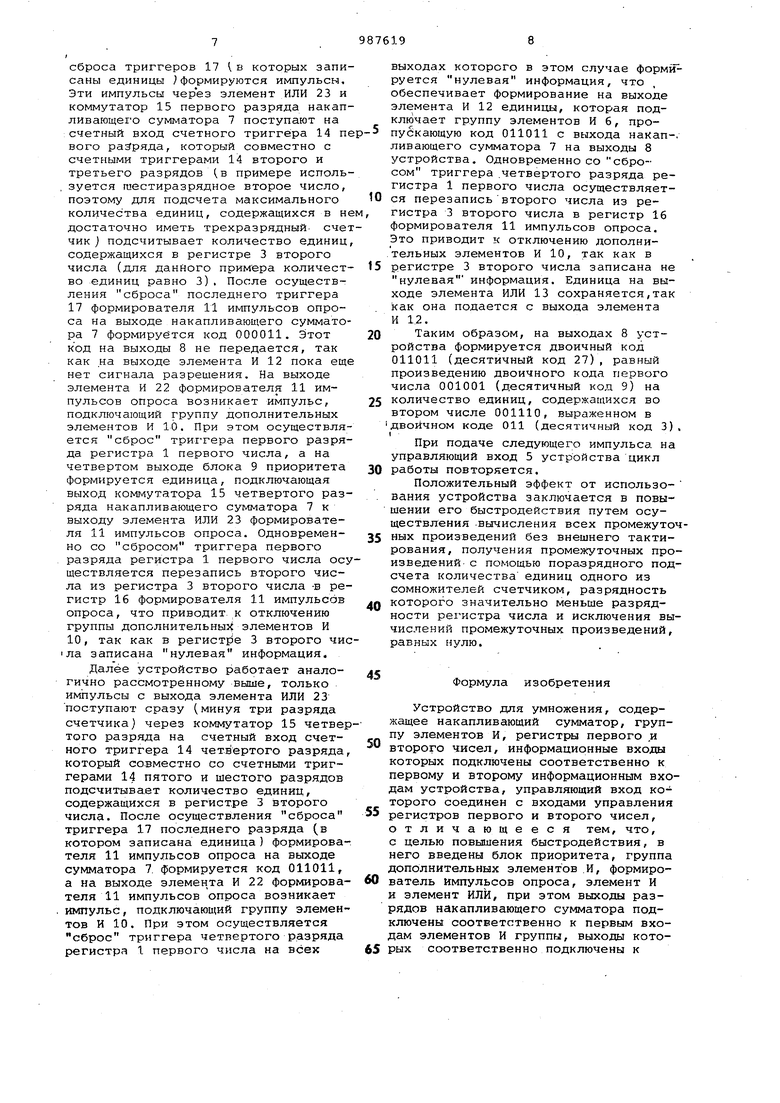

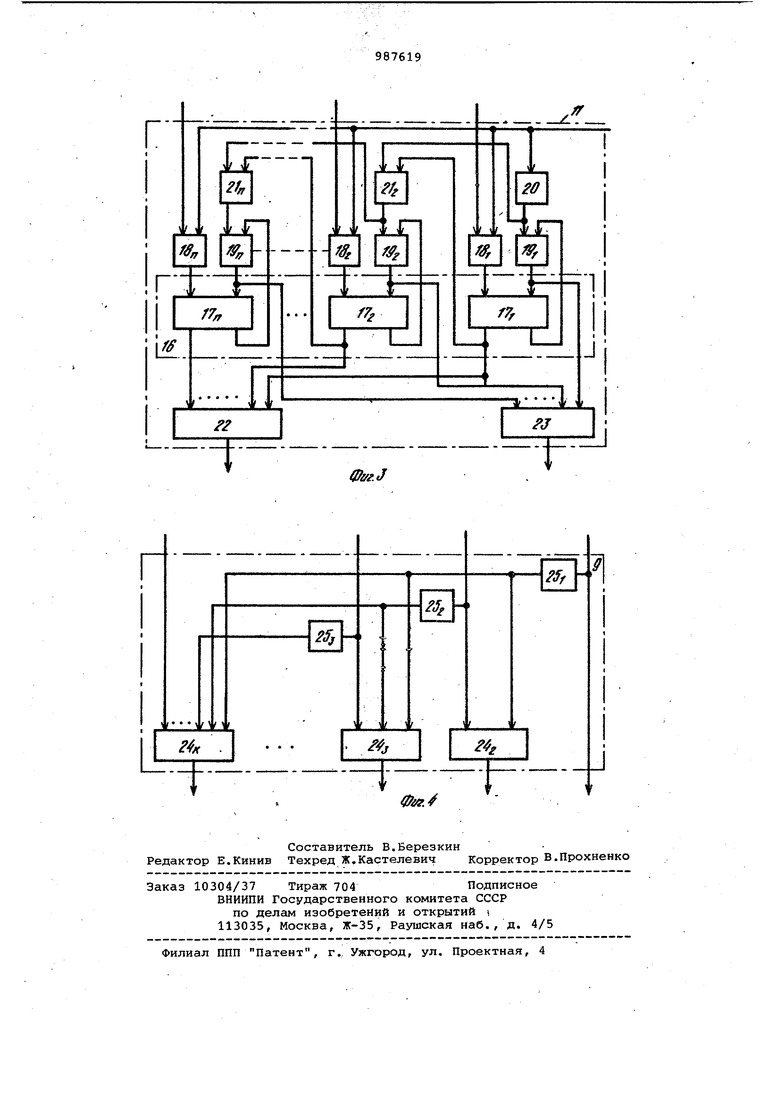

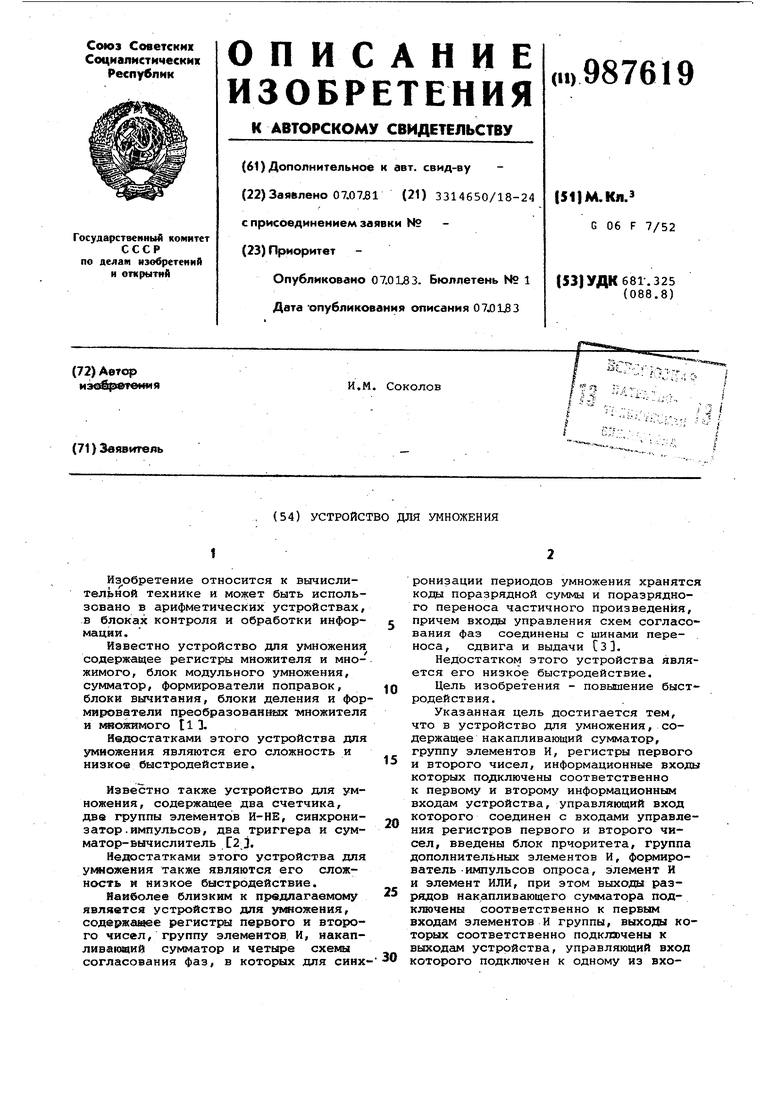

На фиг. 1 изображена структурная схема устройства для умножения на фиг. 2 - функциональная схема накапливающего сумматора; на фиг. 3 функциональная схема формирователя импульсов опроса; на фиг. 4 - функциональная схема блока приоритета.

Устройство для у множения содержит регистр 1 первого числа, информационный вход которого подключен к первому информационному входу 2 устройства для умножения, регистр 3 второго числа, информационный вход которого подключен к второму информационному входу 4 устройства для умножения, уп равляющий вход 5 которого соединен с входами управления регистров 1 и 3 первого и второго чисел, группу элементов И 6, накапливающий сумматор 7, выходы 8 устройства для умножения, -блок 9 приоритета, группу дополнительных элементов И 10, формирователь 11 импульсов опроса, элемент И 12 и элемент ИЛИ 13. При этом выходы разрядов накапливающего сумматора 7 подключены соответственно к первым входам элементов И 6 группы, выходы которых соответственно подключены к выходам 8 устройства. Управляющий вход 5 устройства подключен к одному из входов элемента ИЛИ 13 и к входу обнуления накапливающего сумматора 7, информационные входы которого соединены соответственно с выходами блока 9 приоритета и первыми входами дополнительных элементов И группы, выходы которых соединены соответственно с обнуляющими входами разрядов регистра первого числа. Входы блока 9 приоритета соответственно подключены к выходам разрядов регистра 1 первого числа и входам элемента И 12, выход которого соединен с вторыми входами элементов И группы б и другим входом элемента ИЛИ 13, остальные входы которого подключены к выходам дополнительных элементов И 10 группы. Информационные входы формирователя 11 импульсов опроса подключены соответственно к выходам разрядов регистра .3 второго числа, а управляющий вход к выходу элемента ИЛИ 13.

Каждый разряд накапливающего сумматора 7 (см.фиг. 2) содержит счетный триггер 14 и коммутатор 15, информационные входы которого соединены с выходом счетного триггера предыдущего разряда исправляющим входом накапливающего сумматора 7. Управляющие входы коммутаторов 15 соединены с .соответствующими информационными входси и накапливающего сумматора 7, а выходы j- с входами счетных триггеров 14. Входы обнуления счетных .триггеров 14 соединены с входом обнуления накапливающего сумматора 7, а выходы - с выходами соответствующих разрядов накапливающего сумматора 7.

Формирователь 11 импульсовопроса (сМ. фиг. 3) содержит регистр 16, выполненный на п триггерах 17 (где п разрядность регистра 3 второго числа) , группы элементов И 18 и 19, элемент НЕ 20, группу элементов И 21, элемент И 22, элемент ИЛИ 23. Вход элемента НЕ 20 соединен с управлййои им входом формирователя 11 импульсов опроса и первыми входами элементов И 18 первой группы формирователя 11 импульсов опроса. Выход элемента НЕ 20 соединен с первыми входами первых, элементов И 19 и 21 второй и третьей групп формирователя импульсов опроса. Выходы элементов И 18 и 19 первой и второй групп формирователя 11 импульрод опроса . соединены с прямым и инверсным входгиии соответст ую цих разрядов регистра 16 формирователя 11 импульсов опроса. Инверсные выходу разрядов регистра 16 соединены со входс1ми элемента И 22 формирователя 11 импульсов опроса. Выходы элементов И 21 третьей групцы формирователя 11 импульсов опроса соединены соответственно с первыми входами элементов И 19 второй группы, начиная с второго, формирователя 1-1 импульсов опроса Первый вход каждого элемента И 21 третьей группы, начиная с второго, соединен с выходом предаадущего элемента И 21 третьей группы фо1 шрователя 11 импульсов опроса. Вторые входы .элементов И 21 третьей rpyi|nta формирователя 11 импульсов опроса соединены с инверсными выходами соответствующих разрядов регистра 16 формирователя 11 импульсов -опроса. Вторые входы элементов И 19 второй группы формирователя 11 импульсов опроса соединены с прямыми выходами соответствующих разрядов регистра 16 формирователя 11 импульсов опроса

а выходы подключены к .входам элемен- ; та ИЛИ 23 формирователя li импульсов опроса. Вторые входа элементов И. 18 первой группы формирователя 11 нмпульсов опроса соединены с соотгветствующими информационными входами формирователя 11 импульсов :опрбса. Выходы элемента И 22 и элемента ИЛИ. 23 формирователя 11 импульсов опроса, являющиеся соответственно первыми и

вторыми выходами формирователя 11 импульсов опроса, (Зоединены соответст-. венно с вторыми входами дополнитель-, ных элементов и 10 группы и управляк) щим входом накапливающего сумматора

7. , , -. .

Блок 9 приоритета (см. фиг. 4) содержит (K-l) элементов И 24 и {К-1) . элементов НЕ 25. При этом одни входхы элементов И 24 соединены череэ элементы НЕ 25 со всеми выходами младших разрядов регистра 1 первого чис ла, а другие входы элементов И 24 соединены соответственно с выходами остальных разрядов регистра 1 первого числа. Выходы элемея тов И 24 связаны с управлякнцими входами коммутаторов 15 накапливающего сумматора 7. Устройство для умножения работает следующим образом..

Перед началом работы на входы 2 и 4 устройства (из внетннего устройства обработки информации) подает необходимые двоичные коды перврго и вто рого чисел.

При подаче импульса на управляющий вход 5 первое число (например, 001001), поступающее с первого информационного входа 2, записывается в регистр 1 первого числа, а второе

число (например, 001110 , поступающее со второго информационного входа 4 устройства, записывается в регистр 3 второго числа и через него в регистр 16 формирователя 11 импульсов опроса. Счетные триггеры 14 накапливанмцего сумматора.7 устанавливаются при этом в нулевое исходное состояние. Так как в первом разряде регистра 1 первого числа записана единица, то на первом выходе блока .

9 приоритета;формируется также единица. При этом вход коммутатора 15 первого разряда накапливающего cynwaтора 7 подключается к выходу элемента ИЛИ 23 формирователя 11 импульсов/

опроса.

Далее при снятии импульса с управляющего входа 5 элемент НЕ 20 формирователя 11 импульсов опроса Овеспечивает подключение этого фоцлгарователя путем подачи разрешающего сигнала на входы элементов И 19 и 21 первбго и второго раэрядов. При этом в формирователе 11 импульсов опроса одновременно с осуществлением поочередного сброса триггеров 17 (. в которых запи саны единицы Сформируются импульсы. Эти импульсы через элемент ИЛИ 23 и коммутатор 15 первого разряда накап ливающего сумматора 7 поступают на счетный вход счетного триггера 14 п вого разряда, который совместно с счетными триггерами 14 второго и третьего разрядов (, в примере исполь , зуется гаестиразрядное второе число, поэтому для подсчета максимального количества единиц, содержащихся в н достаточно иметь трехразрядный- сче чик j подсчитывает количество единиц содержащихся в регистре 3 второго числа (для данного примера количест во единиц равно 3), После осуществления сброса последнего триггера 17 формирователя 11 импульсов опроса на выходе накапливающего суммато ра 7 формируется код 000011. Этот код на выходы 8 не передается, так как на выходе элемента И 12 пока ещ нет сигнала разрешения. На выходе элемента И 22 формирователя 11 импульсов опроса возникает импульс, подключающий группу дополнительньтх элементов И 10. При этом осуществляется сброс триггера первого разряда регистра 1 первого числа, а на четвертом выходе блока 9 приоритета формируется единица, подключающая выход коммутатора 15 четвертого разряда накапливающего сумматора 7 к выходу элемента ИЛИ 23 формирователя 11 импульсов опроса. Одновременно со сбросом триггера первого разряда регистра 1 первого числа осу ществляется перезапись второго числа из регистра 3 второго числа -в регистр 16 формирователя 11 импульсов опроса, что приводит к отключению группы дополнительны элементов И 10, так как в perHCTfie 3 второго чис |ла записана нулевая информация. Далее устройство работает аналогично рассмотренному выше, только импульсы с выхода элемента ИЛИ 23 поступают сразу (минуя три разряда счетчика) через коммутатор 15 четвер того разряда на счетный вход счетного триггера 14 четвертого разряда который совместно со счетными триггерами 14 пятого и шестого разрядов подсчитывает количество единиц, содержащихся в регистре 3 второго числа. После осуществления сброса триггера 17 последнего разряда (в котором записана единица ) формирователя 11 импульсов опроса на выходе сумматора 7. формируется код 011011, а на выходе элемен,та И 22 формирователя 11 импульсов опроса возникает импульс, подключающий группу элементов И 10. При этом осуществляется сброс триггера четвертого разряда регистра 1 первого числа на всех выходах которого в этом случае формй руется нулевая информация, что обеспечивает формирование на выходе элемента И 12 единицы, которая подключает группу элементов И б, пропускающую код 011011 с выхода накап-. ливающего сумматора 7 на выходы 8 устройства. Одновременно со сбросом триггера .четвертого разряда регистра 1 первого числа осуществляется перезапись второго числа из регистра 3 второго числа в регистр 16 формирователя 11 импульсов опроса. Это приводит к отключению дополнительных элементов И 10, так как в регистре 3 второго числа записана не нулевая информация. Единица на выходе элемента ИЛИ 13 сохраняется,так как она подается с выхода элемента И 12. Таким образом, на выходах 8 устройства формируется двоичный код 011011 (десятичный код 27), равный произведению двоичного кода первого числа 001001 (десятичный код 9) на количество единиц, содержащихся во втором числе 001110, выраженном в ДВОИЧНОМ коде 011 (десятичный код 3), I При подаче следующего импульса на управляющий вход 5 устройства цикл работы повторяется. Положительный эффект от использования устройства заключается в повышении его быстродействия путем осуществления вычисления всех промежуточных произведений без внешнего тактирования, получения промежуточных произведений- с помощью поразрядного подсчета количества единиц одного из сомножителей счетчиком, разрядность которого значительно меньше разрядности рехистра числа и исключения вычислений промежуточных произведений, равных нулю. Формула изобретения Устройство для умножения, содержащее накапливающий сумматор, группу элементов И, регистры первого ,и второго чисел, информационные входы которых подключены соответственно к первому и второму информационным входам устройства, управляющий вход которого соединен с входами управления регистров первого и второго чисел, отличающееся тем, что, с целью повышения быстродействия, в него введены блок приоритета, группа дополнительных элементов .И, формирователь Импульсов опроса, элемент И и элемент ИЛИ, при этом выходы разрядов накапливающего сумматора подключены соответственно к первым входам элементов И группы, выходы которых соответственно подключены к выходам устройства, управляющий вход которого подключен к одному из входо элемента ИЛИ и входу обнуления накап ливающего сумматора, информационные входы которого соединены соответственно свыходами блока приоритета и первыми входами дополнительных элементов И группы, выходы которых соединены соответственно с обнуляющими входами разрядов регистра первого числа, выходы разрядов которого соединены соответственно с входами блока приоритета и входами элемента И, выход которого соединен с вторыми входами элементов И группы и другим входом элемента ИЛИ, остальные входы которого подключены к выходам дополнительных элементов И группы, инфор.мационные входы формирователя импуль сов опроса подключены соответственно к выходам разрядов регистра второго числа, а управляющий вход - к выходу элемента ИЛИ, причем формирователь импульсов опроса содержит регистр, три группы элементов Иг элемент И, элемент ИЛИ, элемент НЕ, вход которо го соединен с управляющим входом фор мирователя импульсов опроса и первыми входами элементов И первой груп.пы формирователя импульсов опроса, выход элемента НЕ соединен с первыми входами первых элементов И второй и третьей групп формирователя импульсов опроса, выходы элементов И первой и второй групп формирователя импульсов опроса соединены с пря мым и инверсным входами соответствую щих разрядов регистра формирователя импульсов опроса, инверсные выходы разрядов которого соединены с входами элемента И формирователя импульсов опроса, выходы элементов И третьей группы формирователя импульсов опроса соединены соответственно с первыми входами элементов И второй группы, начиная с второго, форми рователя импульсов опроса, первый вход каждого элемента И третьей груп пы, начиная с второго, соединен с вы ходом предыдущего элемента И третьей группы формирователя импульсов опроса, вторые входы элементов И третьей группы формирователя импульсов спроса соединены с инверсными выходами соответствующих разрядов регистра формирователя импульсов опроса, вторые входы элементов И второй группы формирователя импульсов опроса соединены с прямыми выходами соответствующих разрядов регистра формирователя импульсов опроса, а выходы подключены к входам элемента ИЛИ формирователя импульсов опроса, вторые входы элементов И первой группы формирователя импульсов опроса соединены с соответствующими информационными входами формирователя импульсов опроса, выходы элемента И и элемента ИЛИ формирователя импульсов опроса, являющиеся соответственно первым и вторым выходами формирователя импульсов опроса, соединены соответственно с вторыми входами дополнительных элементов И группы и управляющим входом накапливающего сумматора, каждый разряд которого содержит счетный триггер и коммутатор, информационные входы которого соединены с выходом счетного триггера предыдущего разряда и управляющим входом накапливающего сумматора, управлйющий вход коммутатора соединен с соответствующим информационным входом накапливающего сумматора , а выход - с входом счетного триггера, вход обнуления которого соединен с входом обнуления накапливающего сумматора, а выход - с выходом соответствующего разряда накапливающего сумматора. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 579617, кл. G 06 F 7/52, 1975. 2.Авторское свидетельство СССР № 579616, кл. G 06 F 7/52, 1975. 3.Хетагуров Я.А. и др. Основы инженерного проектирования УЦВМ. М., Советское радио, 1972, с. 135, рис. 4.44 (прототип).

8

Г Г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для возведения в степень (его варианты) | 1982 |

|

SU1076905A1 |

| Вычислительное устройство для контроля параметров объекта | 1975 |

|

SU690498A1 |

| Умножитель частоты | 1979 |

|

SU807322A1 |

| Устройство для обработки данных при формировании диаграммы направленности антенной решетки | 1987 |

|

SU1462351A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Устройство для умножения двух @ -разрядных чисел | 1987 |

|

SU1439581A1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

| Устройство для моделирования дискретных систем | 1985 |

|

SU1295411A1 |

| Цифровой генератор | 1986 |

|

SU1347164A1 |

| Устройство для управления многоканальной измерительной системой | 1983 |

|

SU1149255A1 |

//

±

.

V к

fj

aL

фуг

f-

Авторы

Даты

1983-01-07—Публикация

1981-07-07—Подача