Изобретение относится к вычислительной технике и может быть использовано при построении цифровых вычислительных машин последовательного действия.. -

Известно устройство для умножения последов ательного типа, содержащее; регистры множителя, множимого и произведения, одноразрядный сумматор последовательного действия, блок управления, логические элементы И, ИЛИ 1.

Однако принцип работы такого устройства не позволяет использовать . в нем динамические регистры ,с. большой степенью интеграции, что.ограничивает область его применения. . ;,, .

Известно также последовательное . множительное устройство с умнежением на -К разрядов множителя, содержйщёе динамияеские регистры .мно5кимо.г6, частных произвёдений;,: k ;п6сле ДОва- тельных сумматоров (. 2 ., . где ;. п - разрядность сомножителей ), k элементов И 2 ,

Недостатки известного устройства заключаются в невозможности реализации в нем динамического принципа работы, что сужает область его применения, и сложности устройства.

Наиболее близким к предлагаемому является последовательное множительное устройство с умножением на 1 разрядов множителя (3), содержащее динамические регистры множимого, частичных произведений, k последовательных сумматоров (2 i k п, где п - разрядность сомножителей), 4 элементов И, причем выходы элементов И соот10ветственно подключены к первым вхо дам последовательных сумматоров, динамический регистр множителя, (k+1) элемент И, два элемента запрета, элемент ИЛИ, причем второй.вход пер15вого последовательного сумматора соединен. с выходом первого элемента запрета, выход каждого последовательного сумматора соединен с вторым входом следующего последовательного

20 сумматора, .выход k-ro последовательнопбсумматора соединен с .входом динамического регистра частичных произведений, выход которого подключен к первому входу (k+1)-го элемента И, а

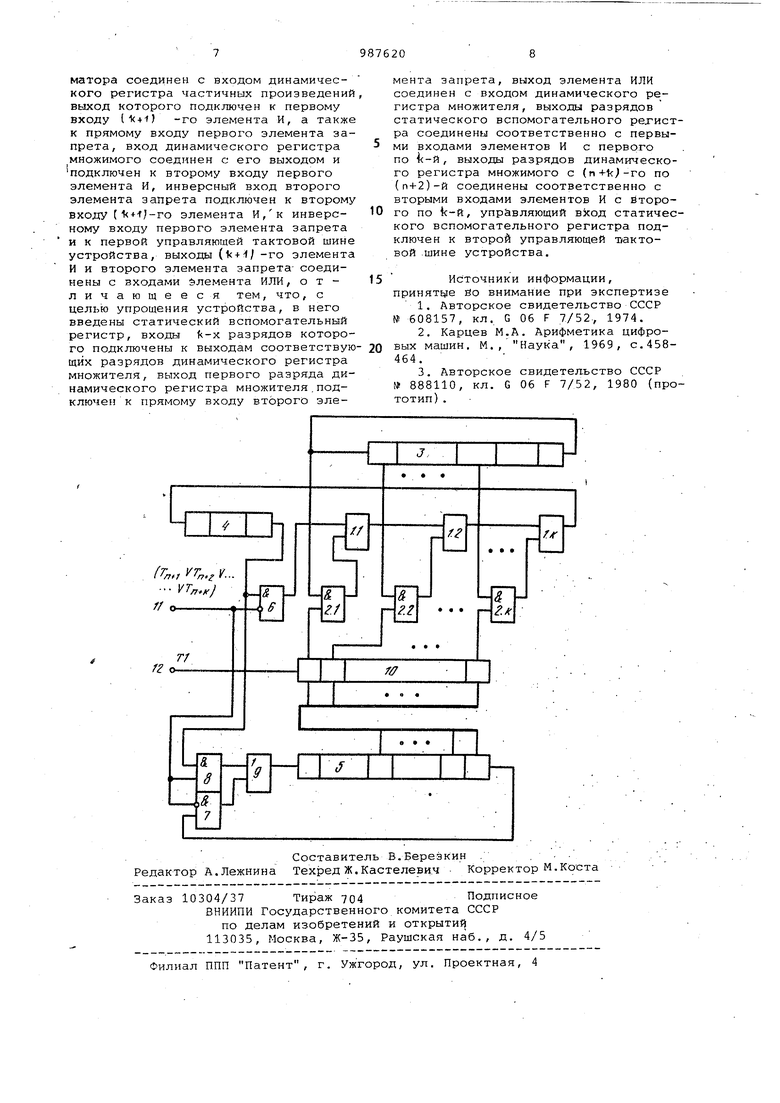

25 также к прямому входу первого элемента запрета, вход динамического регистра множимого соединен с его выходом и подключен к второму входу первого элемента И, инверсный вход вто30 ;р6го элемента запрета подключен к второму входу (kfl)-ro элемента И и к инверсному входу первого элемента запрета, а также к первой управляющей тактовой шине устройства, выходы (k+l)ro элемента И и второго элемей та запрета соединены со входами элемента ИЛИ 3 . К недостаткам этого устройства от носятся большие аппаратурные затраты и большое число внешних связей. Цель изобретения - упрощение устройства. . Поставленная цель достигается тем, что в устройство, содержащее ди намические регистры множимого, множителя и частичных произведений, i последовательных сумматоров (2 fn , где п - разрядность сомножителей , два элемента запрета,элемент. ИЛИ, (k+1) элементов И,причем выходы элементов И с первого по k-й подключены к первым входам соответствующих последовательных сумматоров, динамический регистр мно жителя, второй вход первогопоследовательного- сумматора соединен с выхо дом первогоэлемента запрета, выход каждого последовательного сумматора соединен с вторым входом последующего последовательного сумматора, выход -го последовательного сумматора соединен с входом динамического регистра частичных произведений, выход которого подключен к первому входу (ic+l)-ro элемента И, а также к прямому входу первого элемента запрета , вход динамического регистра множимого соединен с его выходом и подключен к второму входу первого элемента И, инверсный вход второго элемента запрета подключен к второму входу )-го элемента И,, к инверсному входу первого элемента запрета и к первой управляющей, тактовой шине устройства, выходы ()-ro элемента И и второго элемента запрета соединены с входамиэлемента ИЛИ введены статический вспомогательныйрегистр, входы k-x разрядов которого подключены к выходам соответствующих разрядов динамического регистра , множителя, выход первого разряда динамического регистра множителя подключен к прямому входу второго элемента запрета, выход элемента ИЛИ соединен с входом динамического реги стра множителя, выходы разрядов статического вспомогательного регистра соединены с первыми входами элементов И с первого по fc-й, выходы разря дов динамического регистра множимого с (п+)-го по (п+2)-й соединены соответственно с вторыми входами эле Ментов И с второго по , управляющий вход статического вспомогательного регистра подключен к второйуправляющей тактовой шине -устройства. На чертеже представлена функциональная схема последовательного множительного устройства. Устройство содержит 1 последовательных сумматоров 1.1; 1.2;. .. Д.й; k элементов И 2.1; 2.2 ;. , . ,2.1,{п+) - , разрядный динамический регистр 3 множимого (п - разрядность сомножителей) , п-разрядный динамический регистр 4 частичных произведений, празрядный динамический регистр 5 множителя, элемент б запрета, элемент 7 запрета,элемент И 8,элемент ИЛИ 9 k-разрядный статический .регистр 10, первую управляющую тактовую шину 11 и вторую управляющую тактовую шину 12.. Выходы элементов И 2.1/ 2.2/... 2.1 соответственно подключены к первым входам последовательных сумматоров 1.1; 1.2;...l.t. Второй вход первого последовательного сумматора 1.1 соединен с выходом элемента б запрета, выход каждого последовательного сумматора Соединен с вторым входом следующего последовательного сумматора. Выход k-ro последовательного сумматора 1.1 соединен с входом динамического регистра 4 частичных произведений, выход которого подключен к первому входу элемента И 8, а также к прямому входу элемента б запрета. Вход динамического регистра 3 множимого соединен с его выходом и с вторым входом элемента И 2.1. Инверсный вход элемента 7 запрета подключен к второму входу элемента И 8 и к инверсному входу элемента б запрета, а также к управляющей тактовой шине 11. Выходы элементаИ 8 и элемента 7 запрета соединены с входами элемента ИЛИ 9.k информационных входов статического вспомогательного регистра 10 подключены к соответствующим выходам к разрядов динамического регистра 5 множителя, а (k+1)-и выход динамического регистра 5 множите-ля подключен .к прямому входу элемента 7 запрета. Выход элемента ИЛИ 9 связан с входом динамического регистра 5 множителя. 1 выходов статического вспомогательного регистра 10 связаны соответственно с первыми входами элементов И 2.1; 2. 2,-. . .;2.k. Выходы разрядов с (п+1)-го по (п+2)-й включительно динамического регистра 3 множимого связаны соответственно с вторыми входами элементовИ 2,2; 9 т. 9 / .j,. ...i. Управляющий вход статического вспомогательного регистра 10 подсоединен к управляющей тактовой шине 12.Устройство работает по циклам. Длительность каждого цикла равна (n+k) тактам, так как при умножении п-разрядноуо множимого на k очередных, цифр множителя получается частичное произведение, имеющее разрядность (n+k), а для получения одной цифры частичного произведения нужен один такт. Считаемf что, когда на выходах пе вых разрядов динамических регистров в режиме хранения находятся первые разряды записанных в.них чисел, на управляющей тактовой шине 12 появляется сигнал 1, соответствующий началу цикла. В исходном состоянии (такт Т1 пер вого цикла) в п первых разрядах регистра 3 находится множимое, а в регистре 5 - множитель. В регистре 10 записаны младшие . цифр множителя. В остальных разрядах регистра 3 и в ре гистре 4 записаны нули. Рассмотрим цикл работы устройства. В такте Т1 каждого цикла в регистр 10 записываются t очередных разрядов множителя, наукоторых в дан ном цикле будет производиться умножение. Цикл циркуляции динамических регистров 5 и 4 меньше длительности циклов циркуляции всего устройства, равной, (n+k) тактов, и обеспечивает в каждом цикле сдвиг содержимого регистров 5 и 4 на i разрядов вправо. Цикл циркуляции регистра 3 равен циклу циркуляции устройства. На сумматоре 1.1 в каждом цикле осуществляется сложение сформированной в предыдущих циклах и сдвинутой на ic разрядов вправо суммы частичны произведений и кода множимого, умно ,енного на младший из k очередных разрядов множителя. На сумматоре 1.2 осуществляется сложение сформированного на выходе сумматора 1.1 числа и сдвинутого на один разряд влево множимого,умноженного на вторую цифру группы разрядов множителя. Аналогичным образом осуществляется сло жение на остальных сумматорах.Сдвиги множимого влево обеспечиваются выдачей задержанного кода множимого с соответствующего выхода регистра 3 и подачей его на выходы сумматоров 1.2,...l.k. Л Управление подачей кода Множимого на входы сумматоров 1.1;...1.k через элементы И-2.1;...2.{с (умножение на цифру множителя) осуществляет ся разрядами с первого по регист ра 10. На выходе сумматора 1.1 за (n+li) тактов формируется очередная сумма частичных произведений, при«leM в первых k тактах определяются 1с очередных (начиная с младших) цифр произведения. В последних тактах формируется текущая п -разрядная сум ма частичных произведений. К концу такта предощущая сумма частичных произведений полностью выдвинется из регистра 4, а в его k младших разрядах будет находиться k очередных цифр произведения. Поэто му, начиная с такта Т -го, по сигналу на управляющей тактовой шине 11 выдача кода из регистра 4 на сумматор 1.1 через элемент 6 запрета блокируется, разрывается цепь циркуляции регистра 5 с выхода первого разряда и открывается цепь циркуляции регистра 5 через элемент. И 8 и. в течение тактов Т„.,,... ,Т„.у в регистр 5 принимаются k очередных разрядов произведения. После последне.го (, такта каждого цикла состояние регистров устройства следующее. Регистр 3 множцмого находится в исходном состоянии. В регистре 4 находятся п старших разрядов очередного частичного произведения. .В старших (i-l)-k разрядах регистра 5 находятся полученные (где 1- номер цикла) младшие разряды произведения, а в младших n-(i-l)-k разрядах регистра 5 - те цифры множителя, которые еще не принимают участия в умножении. 3 регистре 10 находятся k очередных цифр множителя.После последнего такта последнего цикла в регистре 5 находятся старшие цифры произведения, а в регистре 5 - млгщшие .разряды произведения. По сравнению с известным устройством, содержащим два (n+k -разрядных регистра, один п -разрядный регистр и.один (k-1)-разрядный регистр, предлагаемое устройство сод ержит один (n+k)-разрядный регистр, два п -разрядных регистра. Если считать, что затраты на реализацию k триггеров в известном устройстве и k-разрядного статического регистра в предлагаемом одинаковы,то выигрыш в оборудовании в предлагаемом устройстве составит (2 k-1) разрядов. Упрощение предлагаемого устройства достигается тем,- что в известном устройстве число внешних связей равно (k+1), в предлагаемом 2. Формула изобретения Последовательно множительное устройство, содержащее динамические регистры.множимого, множителя и частичных произведений. It последовательных сумматоров (2 k 1Г , где п -разрядность сомножителей ), два элемента запрета, элемент ИЛИ, (k+1) элементов И, причем выходы элементов И, с первого по k-й подключены к первым входам соответствующих последовательных сумматоров, динамический per гистр множителя, второй вход первого последовательного сумматора соединен с выходом первого элемента запрета, выход каждого последовательного сумматора соединен с вторым входом последующего последовательногоа сумматора,выход последовательного сумматора соединен с входом динамического регистра частичных произведений выход которого подключен к первому входу (1 + 1J -го элемента И, а также к прямому входу первого элемента запрета, вход динамического регистра множимого соединен с его выходом и подключен к второму входу первого элемента И, инверсный вход второго элемента запрета подключен к второму входу 1 - -f/-го элемента И,к инверсному входу первого элемента запрета и к первой управляющей тактовой шине устройства, выходы ()/ -го элемента И и второго элемента запрета- соединены с входами Элемента ИЛИ, отличающееся тем, что, с целью упрощения устройства, в него введены статический вспомогательный регистр, входы -к разрядов которого подключены к выходам соответствую щих разрядов динамического регистра множителя, выход первого разряда динамического регистра множителя.подключен к прямому входу второго элемента запрета, выход элемента ИЛИ соединен с входом динамического ре гистра множителя, выходы разрядов статического вспомогательного ретистра соединены соответственно с первыми входами элементов И с первого по -й, выходы разрядов динамического регистра множимого с ( по (п+2)-й соединены соответственно с вторыми входами элементов И с второго по k-й, управляющий вход статического вспомогательного регистра подключен к второй управляющей т/актовой -шине устройства. Источники информации, принятие йо внимание при экспертизе 1.Авторское свидетельство СССР № 608157, кл. G 06 F 7/52-, 1974. 2.Карцев М.А. Арифметика цифровых машин. М., Наука, 1969, с.458464. 3.Авторское свидетельство СССР № 888110, кл. G 06 F 7/52, 1980 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Последовательное множительное устройство | 1980 |

|

SU888110A1 |

| Устройство для умножения чисел | 1980 |

|

SU920713A1 |

| Устройство для умножения чисел | 1979 |

|

SU817702A1 |

| Устройство для умножения в избыточной двоичной системе | 1982 |

|

SU1059568A1 |

| Устройство для умножения | 1981 |

|

SU1007101A1 |

| Параллельный сумматор | 1981 |

|

SU1018114A1 |

| Устройство для умножения чисел в @ -кодах Фибоначчи | 1980 |

|

SU1137459A1 |

| Устройство для умножения | 1981 |

|

SU1018115A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Последовательное устройство для умножения | 1987 |

|

SU1444754A1 |

Авторы

Даты

1983-01-07—Публикация

1981-06-12—Подача