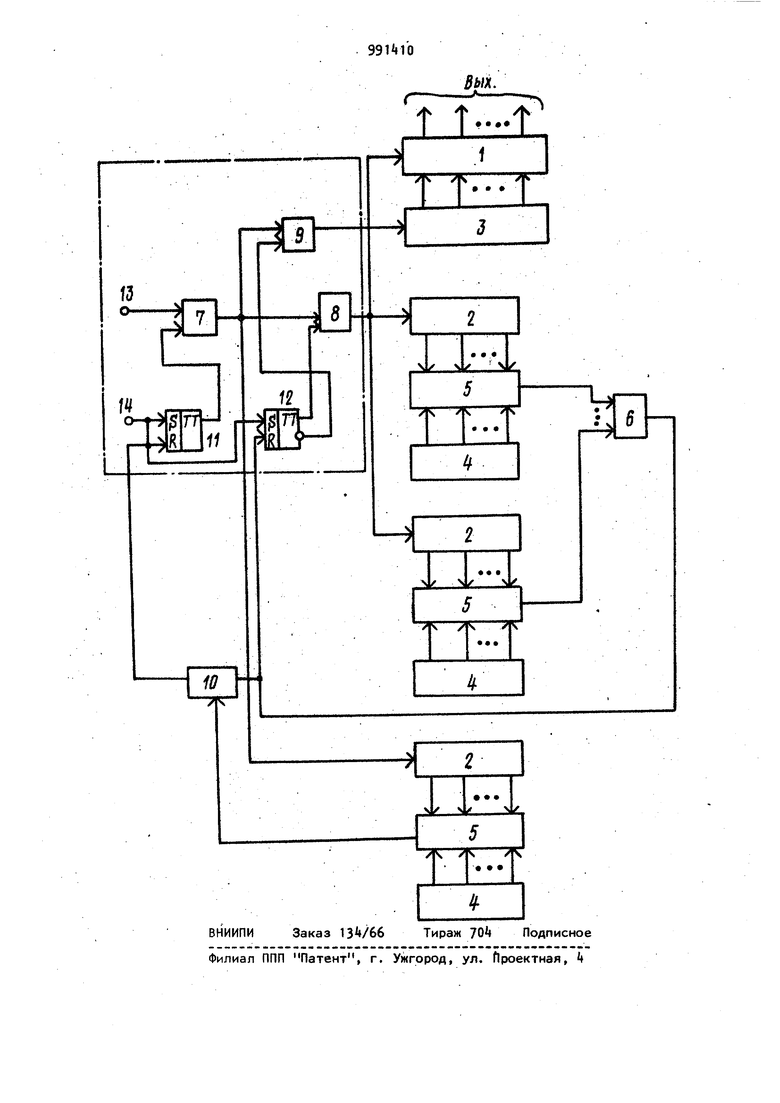

Изобретение относится к вычислительной технике и может быть использовано для сопряжения с вычислительными устройствами, фунюдионирушчими в СОК, 3 таюяе в аппаратуре передачи данных, использующей коды СОК. Известно устройство для преобразования чисел из кода СОК в двоичный код, содержащее многовходовую схему И, по числу оснований системы СОК суммирующие счетчики, входы которых подключены к выходам блока управления и .к входу накапливающего счетчика tl Недостатгам такого преобразователя является то, что до подачи счет ных импульсов в счетчики по модулю необходимо вносить значения аддитивных инверсий остатков кодового слова СОК по соответствующим основаниям что в первую очередь обуславливает необходимость вычисления аддитивных инверсий и, как следствие, приводит к увеличению времени преобразования Наиболее близким к предлагаемому, устройству по технической сущности и достигаемому результату являетсяустройство, содержащее суммирующие счетчики по числу оснований систем14, выходы которых подключены к Первым группам входов схем сравнения состояний , вторые группы входов которых соединены с соответствущими выходами приемных регистров, двоичный накапливающий счетчик, элемент И, выход которого подключен к первому входу триггера,выход которого подключен к первому входу вентиля, второй вход которого соединен с шиной подачи тактовых импульсов С2 . Недостаток устройства - низкое быстродействие. Целью изобретения является повышение быстродействия. Поставленная цель достигается тем, что устройство для преобразования числа из системы остаточных классов в позиционный код, содержащее суммирующие счетчики, входные регистры и схемы сравнения по основаниям системы остаточных классов (СОК), двоичны накапливающий счетчик, выход которог является выходом устройства , первый триггер, первый и второй элементы И причем входы первого элемента И подключены соответственно к выходам схе сравнения, кроме схемы сравнения по наибольшему основанию СОК, счетные входы двоичного накапливающего счетч ка и суммирующих счетчиков, кроме суммирующего счетчика по наибольшему основанию СОК, объединены между С бой , выходы каждого входного регистpa подключены к первым группам входов соответствующих схем сравнения, вторые rpynrw входов которых подключены к выходам соответствующих суммирующих счетчиков по основаниям СОК первый вход второго элемента И является входом тактовых импульсов уст-, ройства, первый вход первого триггера является входом Пуск устройства содержит элемент задержки, второй триггер, третий, четвертый и пятый элементы И, причем выход третьего элемента И подключен к счетному входу двоичного накапливающего счвтчика, а первый вход .подключен к первому входу четвертого элемента И, к выходу второго элемента И и к Учетному входу суммирующего счетчика по наибольшему основанию СОК, второй вход третьего элемента И подключен к единичному выходу второго триггера, нулевой выход которого подключен к второму входу четвертого элемента И, первый вход второго триггера подключен к первому входу первого триггера второй вход которого подключен i выходу пятого элемента И, единичный выход первого триггера подключен к второму входу второго элемента И, второй вход второго триггера и первы вход пятого элемента И объединены и подключены к выходу первого элемента И, второй вход пятого элемента И подключен к выходу схемы сравнения п наибольшему основанию СОК. На чертеже представлена структурная схема устройства. Устройство содержит двоичный накапливающий счетчик 1, суммирующие счетчики 2 по основаниям СОК, элемент 3 задержки, входные регистры по основаниям СОК, схемы 5 сравнения по основаниям СОК,, первый, второй, третий, четвертый и пятый элеменТЫ и 6-10, первый и второй триггеры 11 и 12, вход 13 тактовых импуль- сов устройства, вход 1 Пуск устройства. Устройство работает следующим образом. 8 начальный момент времени накапливающий счетчик 1 и суммирующие счетчики 2 по модулям находятся в нулевых состояниях, триггеры 11 и 12 установлены в нулевые состояния. Во входные регистры записываются остатки преобразуемого числа в СОК. , Импульс запуска устройства, поданный по входу 14, переводит триггеры 11 и 12 в единичное состояние. Потенциал логической 1 с выхода триггера 11 разрешает прохождение тактовых импульсов, подаваемых по входу 13 через элемент И 7, на счетный вход суммирующего счетчика 2, соответствующего наибольшему по величине основанию выбранной СОК и на вход элемента И 8, а потенциал логической 1 с выхода триггера 12 разрешает прохождение тактовых импульсов через элемент И 8 на счетные входы накапливающего счетчика 1 и суммирующих счетчиков 2, соответствующих первым двум остаткам преобразуемого числа в СОК. Под действием тактовых импульсов накапливающий счетчик 1 и суммирующие счетчики 2 начинают изменять свое состояние на единицу с поступлением каждого тактового импульса, В момент равенства состояний первых суммирующих счетчиков 2 и соответствующих им входных регистров k на выходах соответствующих им схем 5 сравнения появляются потенциалы 1, которые вызывают появление на выходе элемента И б логической 1, которая устанавливает триггер 12 в нулевое состояние, запрещая тем самым поступление тактовых импульсов на входы накапливающего счетчика 1 и первых суммирующих счетчиков 2. Сигнал 1, поступивший с нулевого выхода триггера 12, открывает элемент И 9, разрешая тем самым поступление тактовых импульсов через элемент 3 задержки на счетные входы триггеров накапливающего счетчика 1, причем поступление одного тактового импульса на вход элемента 3 задержки должно вызывать увеличение состояния накапливающего счетчика 1 на величину, равную произведению первых двух оснований систеьш, выбранной СОК. Та ким образом, поступление одного так- тового импульса на вход суммирующего счетчика 2, соответствующего наиболь шему основанию, вызывает:увеличение его состояния на единицу, а действие этого же тактового импульса вызывает увеличение состояния накапливающего счетчика 1 на величину, равную произ ведению первых оснований выбранной СОК. В момент совпадения состояний сум мирующего счетчика 2, соответствующего наибольшему по величине основанию, с содержанием соответствующего ему входного регистра k на выходе- со ответствующей схемы сравнения появля ется сигнал 1, который вызывает по явление сигнала 1 на выходе элемен та И 10, который устанавливает триггер 11 в нулевое состояние, тем самым и элемент И 7. На этом преобразо вание числа из СОК в двоичный код за канчивается и результат преобразования находится на счетчике 1. Максимальное число тактов, требуемых для преобразования числа из СОК с основаниями Р, Pj,..., Р в двоич1 1Й код составляет пи N П р. + Р„ - 2, что в Pjl,pa3 меньше, чем у известного устройства. Таким образом, введение в состав устройства элемента задержки, второго триггера, трех элементов И и соответствующих связей позволяет существенно повысить быстродействие. Формула изобретения Устройство для преобразования числа из системы остаточных классов в позиционный код, содержащее суммирующие счетчики, входные регистры и схемы сравнения по основаниям системы остаточных классов, двоичный накапливающий счетчик, выход которого является выходом устройства, первый триггер, первый и второй элементы И, причем входы первого элемента И подклсчены соответственно к выходам схем сравнения, кроме схеьм сравнения по наибольшему основанию системы остаточных классов, счетные входы двоичного накапливающего счетчика и суммирующих счетчиков, кроме суммирующего счетчика по наибольшему основанию системы остаточных классов, 6бт единены между собой, выходы каждого входного регистра подключены к первым группам входов соответствующих схем сравнения, вторые группы входов которых подключены к выходам соответствующих суммирующих.счетчиков по основаниям системы остаточных . .классов, первый вход вTopofo элемента И является входом тактовых импульсов устройства, первый вход первого триггера является входом Пуск устройства, отличающееся тем, что, с целью повышения быстродействия , оно содерймт элемент задержки второй триггер, третий, четвертый и пятый элементы И, причем выход третьего элемента И подключен ксчетному входу двоичного накапливающего счетчика, а первый вход подключен к первому входу четвертого элемента И, к выходу второго элемента И и к счетному входу суммирующего счетчика до на1йбольшему основанию системы ос-таточных классов, второй вход третьего элемента И подключен к единичному выходу BTOpqi o триггера, нулевой выход которого подключен к второму входу четвертого элемента И, первый вход второго триггера подкличенк первому входу первого триггера, второй вход которого подключен к выходу пятого элемента И, единичный выход первого триггера подключен к второму входу второго элемента И, второй вход второго триггера и первый вход пятого элемента И объединены н подключены к выходу первого элемента И, второй вход пятого элемента И подключен к выходу схемы сравнения- по на1 ольшему основанию системы остаточных классов. Источники информации, принятые во внимание при экспертизе 1.Обнаружение и исправление ошибок в дискретных устройствах. Под ред. B.C. Толстякова. М,, Советское радио, 1972, с. 55. 2.Авторское свидетельство СССР 6б50б, кл. G 06 F 5/02, 1975 (прототип).

t T...t

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь непозиционного кода в двоичный код | 1982 |

|

SU1083179A1 |

| Преобразователь кода числа из системы остаточных классов в напряжение | 1982 |

|

SU1069155A1 |

| Аналого-цифровой преобразователь | 1982 |

|

SU1034170A1 |

| Преобразователь кода системы остаточных классов в двоичный код | 1983 |

|

SU1133669A1 |

| Устройство для преобразования чисел из кода системы остаточных классов в позиционный код с контролем ошибок | 1991 |

|

SU1797119A1 |

| Устройство для преобразования чисел из кода системы остаточных классов в двоичный код | 1972 |

|

SU466506A1 |

| Устройство для прямого и обратного преобразования кода системы остаточных классов в двоичный код | 1982 |

|

SU1075254A1 |

| Обратимый преобразователь двоичных кодов в код системы остаточных классов | 1983 |

|

SU1141398A1 |

| Преобразователь непозиционного кода в двоичный код | 1984 |

|

SU1179547A1 |

| Преобразователь кода из системы остаточных классов в позиционный код | 1980 |

|

SU928339A1 |

Авторы

Даты

1983-01-23—Публикация

1981-10-27—Подача