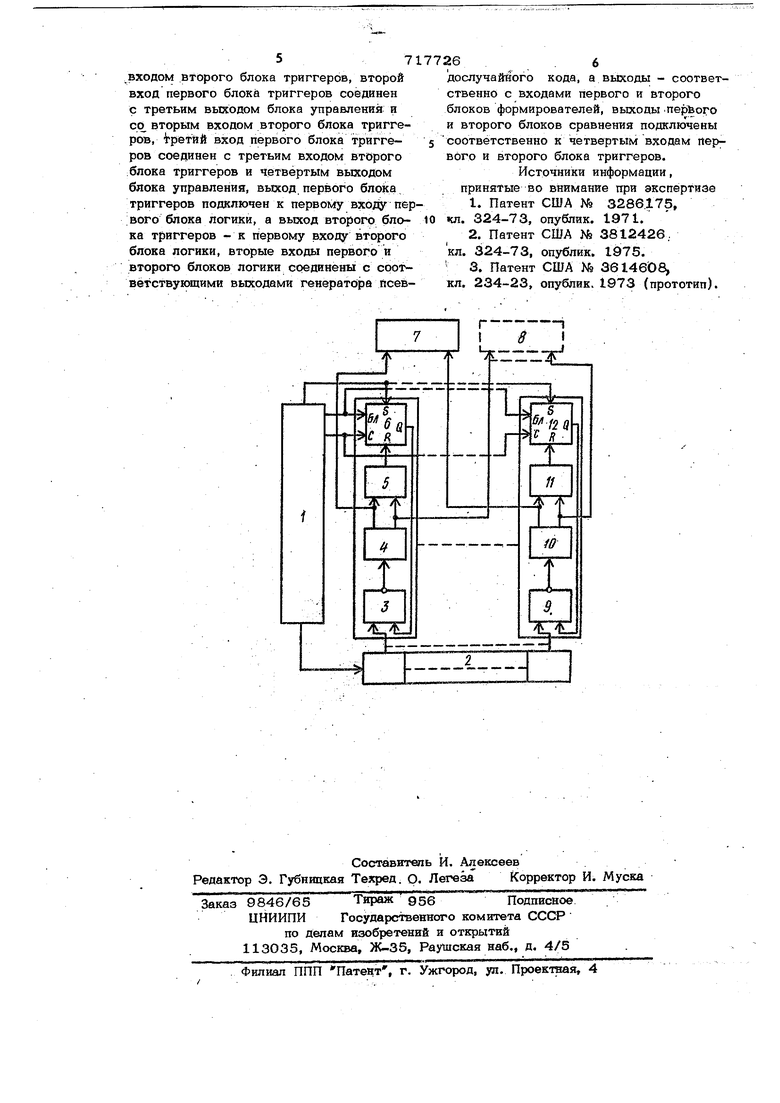

Предлагаемое устройство относите к контрольно-измерительной технике и може быть использовано в устройствах проверки логических ячеек вычислительных машин. Ийвестны устройства, в которых в качестве коммутационных элементов испол зовали тyмблepa,j реле 1 и т.п., а также устройства, в которых коммутация входов и выходов осуществляется по за- данвой программе 21. Общим недостатком устройств fl и 2 является сложность узла коммутации. Наиболее близким по технической сущ ности к данному изобретению является устройство для проверки логических схем содержагаее первый и второй блоки форми рователей, одна группа выходов которь1х соединена с соответствующими входами проверяемого объекта, а другая - с соответствующими входами эТалокйогб объекта, первый и второй блоки сравнен и блок упрявления, первый выхбд которог подключен к входу, генератора псевдослучайного кода З. Недостатком устройства является его низкая наделтость, вытекающая из сложности узяа коммутапий. Целью изобретения является надежность устройства.. Указанная цель достигается тем, что оно содержит первый и второй блоки логики, первый и второй блоки триггеров, первый вход первого блока триггеров соединен со вторым выходом блока управ-i ления и, с первым входом второго блока триггеров,, второй вход первого блока триггеров соединен с третьим выходом блока управления и со вторым входом второго блока триггеров, третий вход первого блока триггеров соединен с , третьим входом второго блока триггеров и четвертым выходом блока управления, выход первого блока триггеров подключен к первому входу первого блока логики, а выход второго блока триггеров - к первому входу второго блока логики, вторые входы первого и второго блоков логики соединены с соответствующими выхоДайи генё ратора псевдослучайного кода, а выходы - соответственнЬ с входами первого и второго блоков фор мирователей, выходы первого и второго блоков сравнения подключены соответственно к четве зтым входам первого и второго блока тг)иггеров. . Недостатком, устройства является низкая еГо надежность. Целью изобретения является повышение надежности устройства. . . Предлагаемое устройство имеет два рёжима работы-йастройка и проверка. .В режиме настройки подключается один проверяемый узел, на все выводы которого подается случайный код. этом производится автоматическое разделение входови выходов проверяемоГо узла. Это осуществляется при сравнени СИ налов на выводах с поданйътм кодом. Если данный вывод является входом, то сйГ-налы идёнтичкЁы,; если - выходом, то в некоторый момент времени произойдет несовпадение, по сигналу которого срабатывает схема коммутации и отключает . .генератор псевдослучайного кода (ГПК): от данного вывода проверяемого узла. Перевод стенда в режим проверки блокирует схему коммутации и позволяет далее вести проверку сравнением с эталонным узло Блок-схема . устройства представлена на чертеже., Устройство содержит блок управления 1, генератор псевдослучайного кода (ГПК 2,первый блок логики 3, первый блок формирователей 4, первый блрк сравнения 5, первый блок триггеров 6, проверяемый объект 7, эталонный бъект 8, второй . блок логики 9, второй блок формирователей 1О и второй блок сравнения 11, второй блок триггеров 12.: Устройство работает следующим образом. В режиме настройки в; устройству подключаются один проверяемый объект 7. Одновременно с запуском ГПК 2 блок управления 1 устанавливает в 1 все три1Р герь блока 6. Код ГПК 2 проходит блок 3, формирователь 4 и поступает на одно- Я) именные выводи 7 и 8 и на входы блока 5. Схема блока 4 выбрана такой, чтобы при объединении ее выхода с выходом микросхем проверяемого узла реалидовывалась логическая функция И для их вы- 55 ходных сигналов. Результат сравнения на R входе триггера блока 6 стробируется узким импульсом. Если данный вывод проверяемого узла является вьЬсодным, то сигнал на выводе объекта 7 будет отличаться от сигнала на одноименном выводе объекта 8, так как там нет однотийной .проверяемой схемы. Первое же несовпадение вызовет переброс триггера блока б в О, что Запретит прохождение сигнала данного разряда ГП1К 2 через блок 3 и установит соответствуюший форрирователь 4 в 1. Подобная ситуация может возникнуть не сразу после начала работы ГПК 2, поэтому для достгоберностй коммутации блдк I отводит достаточно большое число тактов на режим настройки. По окончании режима блок I вырабатываёт сигнал блокировки триггеров блока 6 и останавливает ГПК 2. При переключении стенда в режим проверки в блоке 1 вырабатьтается запрета на блок 6, при этом состояние триггеров фиксируется, и устройство подготовлено к проверке лЬгических схем данного типа. Далее, подключив эталон 8, можно проводить проверку методом сравнения. Длительность такта ГПК невелика (порядка, нескольких микросекунд)г- поэтому даже при большом числе тактов настройки коммутация входов-выходов занимает порядка 0,1 сек, а надежность .устройства при большом числе вьгеодов проверяемых узлов суще ственно выше, чем у известных, за счет сокращения числа и упрощения коммутационных элементов, которые вьгаолнены на микросхемах широкого пользования. Таким образом, предлагаемое устройство обладает большей надежностью по сравнению с известными устройствами контроля логических узлов. Формула изобретения Устройство для проверки логических схем, содержащее первый и второй блоки формирователей, одна группа выходов которых соединена с соответствующими входами проверяемого объекта, а другая с соответствующими входами эталонного объекта, первый и второй блоки сравненйя и блок управления, первый выход которого подключен к входу генератора псёвд1ослучайного кода, отличающееся тем, что, с целью повышения надежности устройства, оно содержит пер-вый и второй блоки логики, первый и второй блоки Триггеров, первый вход перво го блока триггеров соединен со вторым выходом блока управления и с первым 57 ,входом второго блока триггеров, второй вход первого блока триггеров соединен с третьим выходом блока управления и cfi вторым входом второго блока триггеров, третий вход первого блока триггеров соединен с третьим входом второго блока триггеров и четвертым выходом блока управления, выход первого блойа триггеров подключен к первому входу пер ;вого блока логики, а выход второго блока триггеров к первому входу второго блока логики, вторые входы первого и второго блоков логики соединены с соответствующими выходами генерато эа йсев26.6 дослучаййого кода, а выходы - соответственно с входами первого и второго блоков формирователей, выходы .перЬого и второго блоков сравнения подключены соответственно к четвертым входам первого и второго блока триггеров. Источники информации, принятые во внимание при экспертизе 1.Патент США Мэ 3286.175, кл. 324-73, опублик. 1971. 2.Патент США Ns 3812426. кл. 324-73, опублик. 1975. 3. Патент США 6 3614608, кл. 234-23, опублйк. 1973 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Устройство для контроля программных автоматов | 1988 |

|

SU1571552A1 |

| Устройство для контроля логических узлов | 1981 |

|

SU993168A1 |

| Устройство контроля микропроцессорных блоков | 1986 |

|

SU1332320A2 |

| Устройство для поиска неисправностей в логических узлах | 1981 |

|

SU970283A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1260961A1 |

| УСТРОЙСТВО ДЛЯ ИМИТАЦИИ ОТКАЗОВ И ВНУТРИСХЕМНОГО ТЕСТИРОВАНИЯ ЭЛЕМЕНТОВ ДИСКРЕТНОЙ АППАРАТУРЫ | 1995 |

|

RU2093885C1 |

| Многоканальное устройство тестового контроля логических узлов | 1985 |

|

SU1265778A1 |

| Устройство контроля микропроцессорных блоков | 1982 |

|

SU1042023A1 |

| Устройство для контроля цифровых узлов | 1986 |

|

SU1518906A2 |

Авторы

Даты

1980-02-25—Публикация

1977-09-09—Подача